Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советские

Социалистнческмк

Реслублмк

< >841065 (61) Дополнительное к авт. свид-ву № 574774 (22) Заявлено 11.11.79 (21) 2839076/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 23.06.81. Бюллетень №23

Дата опубликования описания 28.06.81 (51) M. Кл.

G 11 С 29/00 .

Гасударственные кемитет (53) УДК 681.327 (088.8) пп делам нзобретений и аткрмтий (72) Авторы изобретения

Г. А. Семавин и А. А. Обухович (71) Заявитель (54) УСТРОЛСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно по основному авт. св. № 574774 устройство для защиты памяти, которое содержит датчик интервалов времени, подключенный выходом к первому входу элемента И, блок регистрации адреса, входы которого соединены соответственно с адресными шинами и выходом элемента И, последовательно соединенные дешифратор, ключевые элементы, триггеры, дополнительные элементы И и элемент ИЛИ, выход которого подключен ко второму входу элемента

И, входы дешифратора и датчика интервалов времени соединены соответственно с адресными шинами и выходами дополнительных элементов И, причем одни из входов последних подключены к соответствующим выходам ключевых элементов (1).

Недостатком этого устройства является его низкая надежность, выражающаяся в том, что устройство не ограничивает число обращений к закрытым ячейкам памяти.

При многократном обращении к закрытым ячейкам памяти (например, при преднамеренных попытках получения доступа к закрытым ячейкам памяти) возрастает вероятность ложного срабатывания устройства, вследствие которого происходит нарушение защиты.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в устройство введены счетчик, элемент И-НЕ и элемент задержки, вход которого подключен к адресным шинам, а выход — к первому входу элемента И-НЕ, второй вход которого соединен с выходом элемента И, а выход— с входом счетчика, выход которого подключен к одному из входов блока регистрации адреса и к одним из входов триггеров.

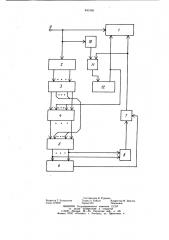

На чертеже изображена функциональная схема устройства.

Устройство содержит блок 1 регистрации

1s адреса, дешифратор 2, ключевые элементы

3, триггеры 4, дополнительные элементы И 5, датчик интервалов времени 6, элемент И 7, элемент ИЛИ 8, адресные шины 9, элемент

10 задержки, элемент И-НЕ 11 и счетчик 12.

Вход элемента 10 задержки подключен к адресным шинам 9, а выход — к первому входу элемента И-НЕ 11, второй вход которого соединен с выходом элемента И 7, а выходс входом счетчика 12, выход которого под841065 ключен к одному из входов блока 1 и к одним из входов триггеров 4.

Элемент 10 задержки задерживает поступление кода адреса на элемент И-НЕ 11 на время срабатывания дешифратора 2, ключевых элементов 3, дополнительных элементов И 5, элемента ИЛИ 8, элемента И 7.

Элемент И-НЕ 11 предназначен для включения счетчика 12 при неудачных попытках обращения к защищаемым ячейкам памяти.

Счетчик 12 предназначен для подсчета числа неудачных попыток обращений к закрытым ячейкам памяти и для регистрации в блоке 1 регистрации адреса.

Устройство работает следующим образом.

В начальном состоянии производится установка триггеров 4, для чего на шины 9 подаются коды адресов ячеек памяти, доступных данной программе. При этом на соответствуюших выходах дешифратора 2 появляются сигналы, которые через ключевые элементы 3 устанавливают соответствуюшие триггеры 4 в единичное состояние, подготавливая тем самым срабатывание элементов

И 5. Триггеры 4 в единичном состоянии определяют допуск к соответствующим ячейкам памяти.

Кодовый адрес запрашиваемой ячейки поступает в блок 1 и дешифратор 2. На соответствуюшеи выходе дешифратора 2 появляется сигнал, который через один из выходов ключевых элементов 3 поступает на вход соответствующего элемента И 5. Если к запрашиваемой ячейке памяти разрешен допуск. то на вход этого элемента И 5 подается разрешающий сигнал с соответствующего триггера 4. Элемент И 5 срабатывает и через элемент ИЛИ 8 открывает элемент И 7, а также запускает датчик 6 интервалов времени. Датчик 6 формирует временной интервал, в течение которого разрешается допуск к запрашиваемой ячейке памяти. Этот сигнал через открытый элемент И 7 поступает в блок 1, выдающий сигнал разрешения допуска в течение сформированного интервала времени.

Одновременно с подачей кодового адреса на дешифратор 2 он поступает и на эле4 мент 10 задержки, выходной сигнал которого подается на вход элемента И-НЕ 11 по истечении времени, величина которого определяется суммой времени срабатывания дешифратора 2, ключевых элементов 3, дополнительных элементов И 5, элемента ИЛИ

8, элемента И 7.

В случае обращения к закрытым ячейкам памяти сигнал на выходе элемента И 7 не подается, т.е. на выходе элемента И-НЕ

Il находится положительный сигнал, включающий счетчик 12. Счетчик 12 построен таким образом, что выходной сигнал появляется только при достижении определенного предельного числа обращений к закрытым ячейкам памяти. Этот сигнал поступает в блок 1 регистрации адреса и на триггеры

4, которые блокируют последующие обрашения к ячейкам памяти. Таким образом, для дальнейшего выполнения программы оператору ЭВМ необходимо принимать специальные решения.

20 В предлагаемом устройстве повышение надежности защиты достигается тем, что устройство ограничивает число обращений к закрытым ячейкам памяти, уменьшая тем самым вероятность ложного срабатывания устройства.

Формула изобретения, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 5747?4, кл. G 11 С 29j00, 1976.

Устройство для защиты памяти по авт. з0 св. № 574774, отличающееся тем, что, с целью повышения надежности устройства, оно содержит счетчик, элемент И-НЕ и элемент задержки, вход которого. подключен к адресным шинам, а выход — к первому входу элемента И-НЕ, второй вход которого соединен с выходом элемента И, а выход — с входом счетчика, выход которого подключен к одному из входов блока регистрации адреса и к одним из входов триггеров.

841065

Составитель В. Рудаков

Редактор Т. Кугрышева Техред А. Бойкас Корректор М. Демчик

Заказ 4780/81 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушсная наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4