Преобразователь кода грея в двоичныйкод

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Соаетскм

Социалистических

Реслублмк (61) Дополнительное к авт. саид-ву (22) Заявлено 261173 (21) 1976353/18-24 с присоединением заявки М (51)М. Кл.з

С 06 Г 5/02

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 3006 81.Бюллетень М 24 (53) УДК681 325 (088. 8) Дата опубликования описания ЗОЯ6.81 (72) Автор изобретения

А. В. Ходаков (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЫЙ КОД

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей кода Грея, аналого-циф- с ровых преобразователей и узлов контроля по четности.

Известно устройство для преобразования кода Грея в двоичный код, содержащее ряд последовательно соединенных полусумматоров (1).

Недостаток этого преобразователя сотоит в низком быстродействии.

Наиболее близким к предлагаемому изобретению по технической сущности и схемному решению является преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумматоров, прямые и инверсные входы первых слагаемых которых соединены с прямыми и инверсными выходами соответствующих разрядов входного регистра, прямой и инверсный выходы переноса j.-ro (i = 2 —. п) полусумматора (где n — число разрядов кода

Грея) соединены со входами второго слагаемого (i-1) -ro полусумматора (2) .

Недостаток известного преобразователя также состоит в низком быстр одей ст вин . 30

Цель изобретения — повышение быстродействия преобразователя.

Поставленная цель достигается за счет того, что в преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумматоров, прямые и инверсные входы первых слагаемых которых соединены с прямыми и инверсными выходами соответствующих разрядов входного регистра, прямой и инверсный выходы переноса 1-ro (i = 2 — n) полусумматора, где n — число разрядов кода Грея, сое. динены со входами второго слагаемого (i-1 ) -oro полусумматора, введены источники логической единицы и логического нуля, два нагрузочных резистора и группа дифференциальных усилителей., первый и второй входы каждого из ко-, торых соединены с пряьыми и инверсными выходами переноса соответствующего полусумматора, а выходы дифференциальных усилителей являются выходами преобразователя, выходы полусумматора мпадшего разряда соединены через первый и второй резисторы с шиной нулевого потенциала, прямой и инверсный вход второго слагаемого полусумматора старшего разряда соединены со входами логической единицы и логического нуля

842783 соответственно, а также тем, что в нем каждый из полусумматоров выполнен иэ четырех ключей, причем информационные входы первого и второго ключей являются пряьим входом второго слагаемого полусумматора, информационные входы третьего и четвертого ключей являются инверсным входом второго слагаемого полусумматора, управляющие входы первого и третьего ключей являются прямым входом первого слагаемого полусумматора, управляющие входы второго и четвертого ключей являются инверсным входом первого слагаемого полусумматора, выход первого ключа соединен с выходом четвертого ключа и является 15 инверсным выходом переноса полусумматора, выход второго ключа соединен с выходом третьего ключа и является прямым выходом переноса полусумматор а. 20

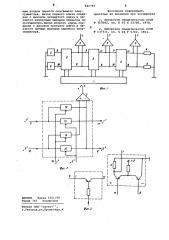

На фиг, 1 представлена блок-схема преобразователя кода Грея в двоичный код; н а фи r . 2 — схема полу сумматора; на фиг. 3 — один иэ возможных вари антон выполнени я ключа и ди фференциального усилителя.

Преобразователь кода Грея в двоичный код содержит входной регистр 1, полу суммат оры 2, ди ффер енци ал ьные усилители 3, нагрузочные резисторы

4, источники 5 и б логической единицы. Выходы 7 дифференциальных усилителей 3 являются выходами преобразователя. Прямой и инверсный входы первого слагаемого полусумматора соединены с выходами соответствующего раэ- 35 ряда входного регистра. Каждый полусумматор 2 имеет инверсный выход 8 переноса, прямой вход 9 второго слагаемого, инверсный вход 10 второго слагаемого и прямой выход 11 4() переноса. Полусумматор 2 содержит (фиг. 2) ключи 12 — 15 .

Преобразователь работает следующим образом.

Код Грея поступает во входной регистр 1 (старшие разряды слева), при этом каждый раэ два иэ четырех полусумматоров будут открыты. Результат суммирования распространяется от старших разрядов к младшим парафазно по двум цепям: цепи прямого значения

ll 9 и цепи инверсного значения 8 и 10. При малом числе разрядов выходной сигнал двоичного кода может быть снят непосредственно с выхода

11. При большом количестве разрядов 55 необходим съем с помощью дифференциального усилителя 3.

Формула изобретения

60 инверсным входом второго слагаемого полусумматора, управляющие входы перТакое выполнение преобразователя позволяет осуществить передачу сигнала от разряда к разряду практически беэ задержки, поскольку сосгояние ключей задается параллельно во всех разрядах путем подачи кода

Грея на их управляющие входы. Распространение же сигналов происходит без переключения самих ключей.

Потери сигнала в упомянутых цепях

{например, за счет остаточного напряжения на ключах) приводит к смещению уровня напряжения как в цепи передачи единицы, так и в цепи передачи нуля, что ограничивает число разрядов преобразователя, Использование дифференциального усилителя поэ— воляет увеличить допустимое число разрядов за счет того, что разность смещения уровней единицу и нуля от разряда к разряду статистически неизменна. Само же допустимое смещение уровней может быть увеличено, поскольку он а являет ся син фаз ной помехой для дифференциального усилителя, коэффициент передачи синфазной помехи которого может быть сделан малым.

1. Преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полу сумматоров, прямые и инверсные нходы первых слагаемых которых соединены с пряьыми и ин в ерсными выходами соответствующих разрядов входного регистра, прямой и инверсный выходы i-ro полусумматора (i = 2 — n), где n — число разрядов кода Грея, соединены со входами второго слагаемого (i 1)-го полусум матора, о тл и ч аю щи и с я тем, что, с целью увеличения быстродействия, н него нведены источники логической единицы и логического нуля, дна нагрузочных резистора и группа дифференциальных усилителей, первый и второй входы каждого из которых соединены с прямыми и инверсными выходами переноса соответствующего полусумматора, а выходы дифференциальных усилителей являются выходами преобразователя, выходы полусумматора младшего разряда соединены через первый и второй нагруэочные резисторы с шиной нулевого потенциала, прямой и инверсный нходы второго слагаемого полусумматора старшегс разряда соединены с источниками логической единицы и логического нуля соответственно.

2, Преобразователь по и, 1, о т ли чающий ся тем,что,снем каждый полусумматор ныполнен из четырех ключей, причем информационные входы первого и второго ключей являются пряьым входом второго слагаемого полусумматора, информационные входы третьего и четвертого ключей являются ного и третьего ключей являются прямым входом первого. слагаемого полусумматора, управляющие входы второго и четвертого ключей являются инверс842783 иг. 1 фиг. Р

Г я lf ным входом первого слагаемого полусумматора, выход первого ключа соединен с выходом четвертого ключа и является инверсным выходом переноса полусумматора,выход второго ключа соединен с выходом третьего ключа и является пряеым выходом переноса полусуммат ор а.

ВНИИПИ Заказ 5101/59

Тираж 745 Подписное

Филиал ППП Патент, г.Ужгород,ул,Проектная,4

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Ю 357682, кл. Н 03 К 23/00, 1970.

2 . Авт орс кое сви де тел ь ст во СССР

9 137311, кл. С 06 F 5/02, 1961.

Г

1 !

j ! 11 I