Преобразователь последовательногодвоичного квазиканонического модифи-цированного кода b параллельныйканонический код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ЕТЕЛЬСТВУ

Опубликовано 300681. Бюллетень М 24

Дата опубликования описания 3006,81 5> < > „э

G 06 F 5/04

Государственный комитет. СССР по делам изобретений и открытий (53) УДК681. 325 (088. 8) В.И.Жабин, В.И.Корнейчук, B.Ï.Òàðàñåíêî,;

E.М.Швец и A. А.Щербина! (72) Авторы изобретения

Киевский ордена Ленина политехнический и ститут им. 50-летия Великой Октябрской социалистической революции (71) Заявитель (5 4 ) ПРЕО ВРАЗ ОВАТЕЛ Ь ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО

КВАЗИ КАНОНИЧЕСКОГО МОДИФИЦИРОВАННОГО КОДА

В ПАРАЛЛЕЛЬНЫЙ КАНОНИЧЕСКИЙ КОД

Изобретение относится к цифровой вычислительной технике и может быть использовано, например при построении арифметических устройств работающих в избыточной двоичной системе счисления с цифрами 1, О, 1.

Известен преобразователь последовательного двоичного квазиканонического модифицированного кода в параллельный кан он и ческий код, содержащий элементы И, распределитель импульсов регистры и элементы задержки (1) .

Недостаток этого устройства — большие аппаратурные затраты и низкое быстродей ст ви е.

Наиболее близким по технической сущности и схемному решению к предлагаемому является преобразователь последовательного двоичного квазиканонического модифицированного кода в параллельный канонический код, содержащий распределитель сигналов, вход которого соединен с первым тактирующим входом преобразователя, и регистр числа (2) .

Недостаток известного преобразователя — низкое быстродействие, связанное с медленным распространением Зр сигналов з аема при выполн енни опера-, ций вычитания.

Цель изобретения — увеличение быстродействия преобразователя °

Поставленная цель достигается за счет того, что в преобразователь последовательндго двоичного квазикано- нического модифицированного кода в параллельный канонический код, содержаший распределитель сигналов, вход которого соединен с первым тактирующим входом преобразователя, и регистр числа, введены три группы элементов И, группа элементов ИЛИ, вспомогательный регистр и два элемента И, причем пряьые. выходы разрядов распределителя сигналов соединены соответственно со входами установки в единицу резрядов вспомогательного регистра и с первыми входами элементов И первой группы, а инверсные выходы разрядов распределителя сигналов подключены соответственно к первым входам элементов И второй группы,выходы которых подключены соответственно ко входам установки в ноль разрядов вспомогательного регистра, выходы которого связаны соответственно с первыми входами элементов И

842785

1G

50

60 третьей группы, выходы одноименных элементов И первой и третьей групп соединены через соответствующие эле— менты ИЛИ группы со счетными входами разрядов регистра числа, первый информационный вход преобразователя соединен с первыми входами первого и второго элементов И и со вторыми входами элементов И н торой группы, второй информационный вход преобразователя соединен со вторым входом первого элемента И, выход которого соединен со вторыми входами элементов И третьей группы, второй тактирую щий вход преобразователя подключен к третьему входу первого и второго входу нторого элементов И, выход последнего из которых подключен ко вторым входам элементов И первой группЫ, а третий тактирующий вход преоб— разователя соединен с входами з аписи информации вспомогательного регист-ра.

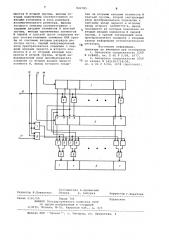

На чертеже изображена структур— ная схема преобразователя последовательного двоичного квазиканоничес— кого модифицированного кода в параллельный канонический код.

Преобраз онат ель содержит р аспределит ел ь 1 си гн алов, который может быт ь ныполнен, например, как кольцевой и разрядный сдвиговой регистр или счетчик с дешифратором на и входов, вспомогательный регистр 2, содержащий п тактируемых RS-триггеров, регистр

3 числа, содержащий и Т вЂ” триггеров, группы элементов И 4 — 6, элементы

И 7 и 8, группу элементов ИЛИ 9, информационные входы 10 и 11 и тактирующие входы 12 — 14.

Прямые выходы распределителя 1 сигн алов соединены с входами реги ст†ра 2 и с первыми входами элементов

И 6 первой группы, а инверсные ныходы распределителя 1 подключены к первым входам элементов И 4 второй группы, подключенных выходами к вхо— дам реги стр а 2, выходы которого св яз аны с первыми входами элементов И 5 третьей группы. Выходы элементов И 5 и 6 второй и третьей групп соедине— ны со входами группы элементов ИЛИ 9, выход которой подключен к счетным нходам регистра 3 числа. Информацион— ный вход 10 преобразователя подведен к первым входам элементов И 8 и 7 и вторым входам элементов И 4 второй группы, а информационный вход 11 связан со вторым входом элемента И 8, выход которого соединен со вторыми входами элементов И 5 третьей группы, Тактирующий вход 12 подключен к третьему входу элемента И 8 и второму входу элемента И 7, выходом подключенного ко вторым нходам элементов И 6 первой группы, тактирующий вход 13 соединен с цепями приема кода вспомогательного реги стра 2, а тактирующий вход 14 подключен к управляющему входу расспределителя 1 си гн алов, Преобраз онат ель работ ает следующим образом.

В исходном состоянии н распределит еле 1 си гн алов еди ни ца н аходи т ся во втором, а но вспомогательном регистре 2 — в первом разряде слева, в остальных разрядах записаны нули.

В каждом 1-м цикле (i = I,n-l) на информационные входы 10 и 11 посту— пает цифра а; операнда А, имеющая вес 2 и принимающая значение из множества (1, О, 1) . Пифры кодируются сл едующим о бр аз о м:

Значение Шина Шина цифры 0 11

1 1 0

О О О

1 1 1

На выходе распределителя 1 единица находится в +1-м разряде.

В первом такте каждого i.— — го цикла по сигналу с входа 12 происходит инвертирование 1 — го разряда регистра

3, если принимаемая цифра равна 1 или 1. Если принимаемая цифра равна

1, то в регистре 3, кроме того, происходит инвертиронание тех разрядов, на которые поступают единицы с вспо— могательного регистра 2. Если прини— маемая цифра равна О, то содержимое регистра 3 не меняется.

Во в-ором такте по сигналу с вхо— да 13 н i-й разряд вспомогательного регистра 2 записывается единица. Ес— ли же поступившая цифра равна 1 или

1, то при этом происходит еще и обнуление остальных разрядов регистра 2

B третьем такте по сигналу с выхода 14 единица в распределителе 1 сигналов сдвигается на один разряд вправо, Если распределитель 1 и регистр

2 выполнены на триггерах .= внутренней задержкой, то тактирующие сигналы с входов 12 — 14 могут поданаться одновременно.

В результате выполнения i — го цикла в регистре 3 числа формируется ре— зультат А, причем крайний слева разрядд является з иаковым.

При выполнении регистра 2 и распределителя 1 сигналов на триггерах с внутренней задержкой время преобразования п-1 разрядного кода с помощью предлагаемого устройства приблизительно равно n7..

Таким образом, предлагаемое устройство превосходит по быстродейcTнию известное примерно в и раз, В таблице приведен пример форьирования устройством результата А при поступлении на него операнда А

10011011.

842785

Цикл Такт Циф- Шина Шина Распредели- Регистр 2 Регистр 3 ра Х 1о тель 1

Исходное состояние

1 1

010000000 100000000 000000000

1 0 О 010000000 100000000 01000000

010000000 010000000 01000000

001000000 010000000 0100000

0 О О 001000000 0100000000 01000000

2 1

001000000 011000000 01000000

000100000 011000000 01000000

0 000100000 011000000 01000000

000100000 011100000 01000000

000010000 011100000 0) 000000

1 000010000 011100000 001110000

000010000 0000 10000 00 111000

000001000 0000 10000 00 111000

1 0 00001000 0000 10000 001101000

000001000 000001000 001101000

000000100 000001000 001101000

0 000000100 000001000 001101000

00 О

3 1

4 1

5 1 б 1

00 110 1000

000000100 000001100

0000000 10 00000 1100 00 110 1000

О 0000000 10 00000 1100 00 110 10 10

00000001О 000000010 001101010

000000001 000000010 001101010

1 000000001 000000010 001101001

000000001 000000001 001101001

000000000 000000001 001101001

7 1

8 1

Формула изобретения

Преобразователь последовательного двоичного квазиканонического модифицированного кода в параллельный канонический код, содержащий распреде- 60 литель сигналов, вход которого соединен с первым тактирующим входом преобразователя, и регистр числа, о т л и ч а ю шийся тем, что, с целью увеличения. быстродействия, в него 65 введены три группы элементов И, группа элементов ИЛИ, вспомогательный регистр и два элемента И, причем прямые выходы разрядов распределителя сигналов соединены соответственно со входами установки в единицу раз— рядов вспомогательного регистра и с первыми входами элементов И первой группы, а инверсные выходы разрядов распределителя сигналов подключены соответственно к первым входам эле842785

Q ц 1 /

Составитель А.Аршавский

Редактор И.Ковальчук Техрец Н. Бабурка

Корректор Г.Решетник

Заказ 5101/59 Тираж 745

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 ментов И второй группы, выходы которых подключены соответственно ко входам установки в ноль разрядов вспомогательного регистра, выходы которого связаны соответственно с первыми входами элементов И третьей группы, выходы одноименных элементов

И первой и третьей групп соединены через соответствующие элементы ИЛИ группы со счетными входами разрядов регистра числа, первый информационный вход преобразователя соединен с первыми входами первого и,второго элементов И и со вторыми входами элементов И второй группы, второй информационный вход преобразователя соединен со вторым входом первого 15 элемента И, выход которого соединен се вторыми входами элементов И третьей группы, второй тактирующий вход преобраз ов ат ел я подключен к третьему входу первого и второму входу второго элементов И, выход последнего из которых подключен ко вторым входам элементов И первой группы, а третий тактирующий вход преобразователя соединен с входами записи информации вспомогательного регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 628485, кл. G 06 F 5/04, 1977.

2, Авторское свидетельство СССР по заявке У 2421567/18-24, кл. G 06 F 5/04, 1978 (прототип).