Матричное устройство для возведенияв квадрат

Иллюстрации

Показать всеРеферат

Союз Соаетсинх

Соцнаннстнчесннх

Распубанн

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<1>842804

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 250679 (21) 2789818/18-24 с присоединением заявки HP (23) Приоритет

Опубликовано 300681 Бюллетень Но 24 (51)М. Кд.

G 06 F 7/552

Государетееииый комитет

СССР ио делаи изобретений и открытий (53) УДК 681. 325 (088.8) Дата опубликования описания 3006 81 (72) Авторы изобретения

Л.A. Шумилов, A. И. Суейдан, А. A. Д. Али и К.Б. Декусар (71) Заявитель

Ленинградский ордена Ленина электротехнический институт им. В.И. Ульянова (Ленина) (54) .МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных устройствах.

Известны матричные множительные устройства, в которых операция возведения во вторую степень обычно осуществляется как операция умножения (1 j и (23, Однако известные матричные множительные устройства требуют для своей реализации больших аппаратурных затрат и не имеют предельного быстродействия.

Наиболее близким по технической сущности к предлагаемому изобретению является матричное устройство, предназначенное для умножения двух и-разрядных чисел, состоящее из (n-1) строк сумматоров, и строк элементов И, причем каждая строка содержит и столбцов (3).

Недостаток устройства - большие аппаратурные затраты при реализации,, а йменно: и (n-1)-сумматоров и n . элементов И и ограниченное быстродействие, составляющее (2пЪ +и ь ), где - время получения сигнала

- l переноса E после того, как на его входы поступил последний иэ входных сигналов, -) — время голучения сигна5 ла суммы В.

Цель изобретения — увеличение быстродействия и сокращение аппаратурных затрат при реализации устройства.

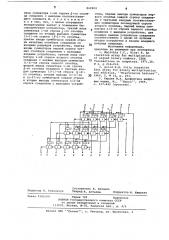

1Q Поставленная цель достигается тем, что в матричном устройстве, содержащем матрицу ячеек иэ n/2 строк и (n-1) столбцов, причем каждая ячейка содержит сумматор и элемент И, первый вход сумматора 1-ой строки

g --ro (i 1, ...,n/21,) =1, ...,n-1, где и разрядность операнда) соединен с первым выходом сумматора i-ой строки (j +1)-ro столбца, первые входы

2О сумматоров (п-1)-го столбца соединены с нулевыми входами устройства, входы элементов И первой строки соединены соответственно со входами старших разрядов операнда, второй

25 вход сумматора i-сй строки g-ro столбца соединен с выходом соответствующего элемента И, третий вход сумматора i-ой строки 1 -го столбца соединен со вторым выходом сумматора (i-1)ой строки (З -2)-го столбца, третьи

842804 входов устройства и входом младшего разряда операнда.

На чертеже представлена блок-схема матричного устройства возведения в квадрат.

Устройство содержит сумматоры 1, элементы И 2, входы 3 и 4 (входы 4.для подачи нулевых сигналов), выходы 5.

Устройство работает следующим образом.

Каждая строка элементов И формирует определенную группу частичных произведений. Каждая строка сумматоров суммирует эти частичные произведения с другой группой частичных

15 произведений. Улучшение характеристик быстродействия и затрат оборудования происходит в результате учета свойства склеивания некоторых членов частичных произведений.

QQ Учет этого свойства иллюстрируется на данном примере. Пусть хдвоичное б-разрядное число, Требуется найти y=x а а а а а а а а а а а а а а

Частичные суммы без учета свойства склеивания аааао а а а а а а а а о а а а а а а а а о аа.аа аааа а а о а а а а а а аа аа аааа а а а а а а а а а а а а а а а о а а а а а а

С учетом этого свойства аааааааааа а а а а а а а а а а

Формула изобретения

ЭФФективность устройства заключается в уменьшении аппаратурных затрат при его реализации и увеличении быстродействия при вычислениях.

Для реализации устройства требуется и и (n-1) ° — сумматоров и (и-1) ° — эле- 55

2 2 ментов И, что примерно вполовину экономит количество оборудования по сравнению с известным устройством.

Время работы устройства примерно равно 2п v< +2 t>- 4i<, что означает

dO выигрыш по быстродействию — Ь + 4Q,, 2 где - время получения сигнала суммы сумматора, 4p — время получения переноса сумматора. 65 входы сумматоров первой строки нечетных столбцов соединены со входами разрядов устройства, третьи входы сумматоров первой строки четных столбцов соединены с нулевыми входами устройства, третий вход сумматора

1-ой строки второго столбца соединен с первым выходом сумматора (i-1)ой строки первого столбца, второй выход сумматора i-ой строки j -го столбца соединен с третьим входог сумматора (i+1)-ой строки (+2) -ro столбца, вторые выходы (n-1)-го и (n-2)-го сумматоров каждой строки и вторые выходы сумматоров n/2-ой строки соединены с выходами устройства, первые выходы сумматоров первого столбца каждой строки соединены с третьими входами соответствующих сумматоров последующей строки второго столбца, первый выход сумматора и/2-ой строки первого столбца соединен с выходом устройства, два младших выхода устройства соединены соответственно с одчим из нулевых

Матричное устройство для возведения в квадрат, содержащее матрицу ячеек из r /2 строк и (n-1) столбцов, причем каждая ячейка содержит сумматор и элемент И, первый вход сумматора 1-ой строки g --ro столбца (i = l,...,n/2; =1...,п-1, где

n — разрядность операнда) соединен с первым выходом сумматора i-ой строки (+1)-ro столбца, первые входы сумматоров (n-1) -го столбца соединены с нулевыми входами устройства, входы элементов И первой строки соединены соответственно со входами старших разрядов операнда, второй

842804

3 3 3 3 3

5 5 5 5 5 5 5 5

Составитель В. Венцель

Техред И. Асталош Корректор M. Швыдкая

Редактор И. Ковальчук

Заказ 5102/60

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 вход сумматора i-ой строки y -ro столбца соединен с выходом соответствующего элемента И, о т л и ч а ю щ е-, е с я тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия устройства, третий вход сумматора i-ой строки q --ro столбца соединен со вторым, выходом сумматора (i-1)-ой строки (4-2)-го столбца, третьи входы сумматоров первой строки нечетных столбцов соединены со входами разрядов устройства, третьи входы сумматоров первой строки четных столбцов соединены с нулевыми входами устройства, третий вход сумматора i-ой строки второго столбца соединен с первым выходом сумматора 15 (i-1)-ой строки первого столбца, второй выход сумматора 1-ой строки

)-го столбца соединен с третьим входом сумматора (1+1)-ой строки (q -2)—

ro столбца, вторые выходы (n-1) -ro Щ и (n-2)-ro сумматоров каждой строки и вторые выходы сумматоров n/2-ой строки соединены с выходами устройства, первые выходы сумматоров первого столбца каждой строки соединены с третьими входами соответствующих сумматоров последующей строки второго столбца, первый выход сумматора n/2-ro строки первого столбца соединен с выходом устройства„ два младших выхода устройства соединены соответственно с одним из нулевых входов устройства и входом младшего разряда операнда.

Источники информации, принятые во внимание при экспертизе

1. Majithia I.Ñ °, Kitai R. An

iterative array for multipication

of signed binary numbers. IEEE

Transactions on computers, 1971,20, Р 2, р 214-216, 2. Guild Н.Н. Jully iterative

fast array for binary multiplication

and addition, Electronics Letters, 1969, 5, 9 12, р. 263.

3. Карцев М.A. Арифметика цифровых машин, М., Наука, 1969, с. 437-442 (прототип).