Устройство для вычисления квадратногокорня

Иллюстрации

Показать всеРеферат

Союз Советскиз

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТВЛЬСТВУ (61) Дополнительное к ввт. свид-ву е 611208 (22) Заявлено 12.11.79 (21) 2842587/18-24 с присоединением заявки Нов (23) Приоритет 51)М. Кл.

G 06 F 7/552

Государственный комитет

СССР но делам изо4ретеиий и открытий

Оиубяиковаио 3006.81 Бюллетеиь ЙЯ 24 (53) УДК 681. 3 (088. 8) Дата опубликования описания 30Я681 (72) Автор изобретения

В.В. Чекушкин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИ . КВАДРАТНОГО КОРНЯ

Изобретение относится к вычисли- тельной технике и может быть исполь эовано в специализированных вычислительных устройствах.

По основному авт.св. 9 611208 5 известно устройство для извлечения квадратного корня, содержащее входной и выходной регистры, блок управления, блок подбора цифр результата, постоянное запоминающее устройство, схему сравнения, входы которой соединены с выходом постоянного запоминающего устройства и первого входного регистра, вход которого подключен к первому входу устройства, вы- 15 ход останова схемы сравнения соединен со входом блока управления, а два других — с информационными входами блока подбора цифр результата, управляющий вход которого соединен 20 с выходом блока управления, а выход блока подбора цифр результата через выходной регистр соединен с первым входом постоянного запоминающее о устройства и с первым, выходом ус- 25 тройства (11

Недостаток известного .устройства» ограниченные функциональные возможности (его можно использовать только для извлечения квадратного корня) . 3P

Цель. изобретения — расширение функциональных возможностей эа счет дополнительного вычисления вэаимообратных монотонно изменяющихся функций и выполнения операции деления.

Поставленная цель достигается тем, что в устройство дополнительно введены второй входной регистр и коммутатор, причем второй вход устройства соединен со вторым входом постоянного запоминающего блока, третий вход которого подключен к выходу коммутатора, первый, второй и третий входы которого соединены соответственно с выходом выходного регистра, третьим входом устройства и выходом второго входного регистра, выход которого является четвертым входом устройства, выход постоянного запоминающего устройства является вторым выходом устройства.

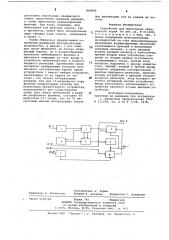

Блок"схема устройства представлена на чертеже.

Устройство содержит первый входной регистр 11схему 2 сравнения, постоянное запоминающее устройство 3, блок 4 управления, блок 5 подбора цифр результата, выходной регистр 6, второй входной регистр 7, коммутатор 8.

842806

Устройство работает следующим образом.

При наличии команды Вычисление квадратного корня в первый входной регистр 1 заносится параллельный код аргумента Х. Все разряды выходного регистра 6 устанавливаются в нуле,вые состояния, а блок 3 по команде, поступающей нэ второй вход устройства, пеРеводится в режим умножения двоичных чисел. В этом случае первый и третий входы блока 3 соответствуют входам умножителя кодов, а выход блока 3 - ° выходу умножителя. С помощью коммутатора 8 по команде, поступающей на третий вход устройства осуществляется подключение на оба вхо- 15 да блока 3 выхода выходного регистра

6. Таким образом, при выполнении операции извлечения квадратного корня блок 3 и коммутатор 8 осуществляют возведение в квадрат значения 20 кода, снимаемого с выхода выходного регистра 6. В .первом такте вычислений включается генератор тактовых импульсов в блоке 4 управления и с е г выходов (чи сло которых равно 25 числу разрядов входного регистра 1) в каждом такте появляются управляющие импульсы. Первый управляющий импульс (в первом такте) устанавливает логическую единицу в самом старшем разряде выходного регистра 6.

Содержание которого возводится в квадрат в блоке 3 и сравнивается схемой сравнения 2 с.содержанием входного регистра 1. Еслй значение квадрата в выходном регистре 6 больше значения аргумента Х во входном регистре 1, то со второго выхода схемы сравнения 4 на соответствующий информационный вход блока подбора цифр результата 5 выдается сиг- 40 нал, который открывает в блоке 5 соответствующие элементы И (на входах сброса старшего разряда и установки следующего разряда выходного регистра 6). В следующем такте управля- 45 ющий импульс со следующего выхода блока 4 управления проходит через открытые элементы И и устанавливает логический нуль в старшем разряде и логическую единицу в следующем разряде. Если квадрат значения в выходном регистре 6 меньше аргумента

Х, то с третьего выхода схемы 2 сравнения на другой информационный вход блока 5 подбора цифр результата выдается сигнал, который открывает в блоке 5 соответствующий элемент H (на выходе установки соответствующего разряда выходного регистра 6), В следующем такте управляющий импульс со следующего выхода блока управле- 60 ния 4 проходит через этот элемент И и устанавливает логическую единицу в следующем разряде. Предыдущий старший разряд при этом остается значащим.Полученное число в выходном реги- 65 стре 6 возводится блоком 3 в квадрат и сравнивается в схеме 2 сравнения со значением аргумента X и т.д.

Если квадрат значения в выходном регистре 6 равен значению аргумента

Х, то с первого выхода схемы 2 сравнения на вход блока 4 управления выдается сигнал, который останавливает работу устройства, так как процесс вычисления квадратного корня закончен. Максимальное число тактов равно n — числу разрядов входного регистра 1.

При наличии команды Вычисление кода угла ф в первый входной ре-. гистр 1 заносится значение величины

sing.Bce разряды выходного регистра 6 устанавливаются в нулевые состояния, а блок 3 по команде, поступающей на второй вход, устройства, переводится в режим вычисления функции синуса.

В этом случае первый вход блока 3 соответствует входу цифрового синусного преобразователя, а выход блока 3 соответствует выходу преобразователя. Вычисление кода угла, как и вычисление квадратного корня, производится в соответствии с вышерассмотренным методом поразрядного уравновешивания с определением на каждом такте вычислений одной значащей цифры кода угла, который снимается с выхода выходного регистра 6. При наличии команды Выполнение операции деления в первый входной регистр 1 заносится делимое

d, а во второй входной регистр 7 делитель f. По команде, поступающей на третий вход устройства, выход второго входного регистра 7 подключается на третий вход блока.3 через коммутатор 8. По команде со второго входа устройства блок 3 переводится в режим умножения кодов. В первом такте вычислений с выхода выходного регистра 6 задается первое значение частного 6 в виде 011...11. С выхода блока 3 снимается произведение f К и сравнивается в схеме 2 сравнения со значением кода делимого d. Ha основании результата сравнения формируется первая значащая цифра частного. Например, при d)f-б в первом разряде записывается логическая единица. Значение частного снимается с выхода выходного регистра 6.

При наличии команды Вычисление функций sing"значение кода угла Я заносится во второй входной регистр 7 и по команде, поступившей с третьего входа устройства, через коммутатор передается на третий вход блока 3, которое по команде, поступившей со второго входа устройства переводится в режим вычисления функции sin P .

Ход функции в1п считывается со второго выхода устройства.

Таким образом, с помощью предлагаемого устройства может быть осу842806

Формула изобретения

15

2S

8c(x Х

Вк

Составитель н. Зорин

Редактор И. Ковальчук Техред H. Асталош Корректор Г. Назарова

Тираж 745 йодписное. ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5102/60

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 ществлено извлечение квадратного корня, выполнение операции деления, а также вычисление вэаимообратных функций. При этом, например, для вычисления как функции синуса, так и арксинуса, может быть использована одна таблица кода синуса, заложенная в блоке 3.

Таким образом в предлагаемом устройстве расширены функциональные воэможности, а именно: с его помощью можно вычислять не только квадратный корень, но и вэаимообратные монотонно изменяющиеся функции и выполнять операцию за счет ввода в устройство мультиплексора и второго входного регистра. Применение предлагаемого изобретения позволит реализовать поставленную задачу одним устройством (вместо набора устройств, реализующих ту же задачу по частям), что снизит аппаратурные затраты. Так для 12-разрядного кода функции аппаратурные затраты при реализации предлагаемого устройства, используемого для осуществления сразу трех видов вычислений в режиме разделения времени, составят 68 микросхем 133 серии, что на 52 микросхемы меньше аппаратурных затрат при реализации той же задачи по частям.

Устройство для вычисления квадратного корня по авт. св. 9 611208, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей за счет дополнительного вычисления взаимообратных-монотонно изменяющихся функций и выполнения операции деления, в него введены второй входной регистр и коммутатор, причем второй вход устройства соединен со вторым входом постоянного запоминающего блока, третий вход которого подключен к выходу коммутатора, первый, второй и третий входы которого соединены соответственно с выходом выходного регистра, третьим, входом устройства и выходом второго входного регистра, вход которого является четвертым входом устройства, выход постоянного запоминающего устройства является вторым выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 611208, кл. G 06 F 7/38, 1978,