Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ТЕЛЬСТВУ

Союз Советскнх

Социалистических

Республик (щ842843 (61) Дополнительное к авт. свид-ву (22) Заявлено 02,1079 (21) 2828157/18-24 р > g,Ç с присоединением заявки Но

G 06 G 7/161

Государственный комитет

СССР ио дезам изобретений и открыти и (23) Приоритет

Опубликовано 300681. Бюллетень М 24 (53) УДК 681.33Ь (088;8) Дата опубликовани я описания 3 0,06,81 (72) Авторы изобретения

В.Г. Чернов и В.Ф. Овчинников (71) Заявитель.

Владимирский политехнический институт (54) ИИОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в гибридных аналого-цифровых вычислительных устройствах, устройствах измерения мощности и качества электрической энергии, а также в других типах инФормационно-.измерительных систем, где требуется выполнение множительно-делительных операций..

Известны множительно-делительные устройства с применением частотноимпульсных, время-импульсных и амплитудно-импульсных модуляторов, содержащие усилители, модуляторы, ключи и Фильтр (1J и (2).

Недостатками указанных устройств является ограниченное число входных переменных, необходимость аналогового усреднения для получения конечного результата.

Наиболее близким по технической сущности к предлагаемому изобретению является множительно-делительное устройство, содержащее источники первого, второго и третьего входных сигналов, первый интегратор с . ключом сброса в цепи обратной связи, вход первого интегратора к источнику первого входного сигнала, нуль орган, один вход которого подключен к.выходу первого интегратора, а другой вход нуль-органа подключен к выходу источника второго входного сигнала, второй интегратор, первый .вход которого подключен к выкоду .источника третьего входного сигнала, триггер, первый вход которого подключен к выходу нуль-органа, одновибратор и запоминающий блок 3).

Недостатком этого устройства является низкая точность работы и ограниченное число входных переменных.

Цель изобретения — повышение точности и увеличение количества входных переменных.

Поставленная цель достигается тем, что в устройство, содержащее источники первого, второго и третьего входных сигналов, первый интегратор с ключом сброса в цепи обратной связи, вход первого интегратора подкяпочен к источнику первого входного сигнала, нуль-орган, один вХод которого подключен к выходу первого интегратора, а другой вход. нульоргаиа подключен к выходу источника второго входного сигнала, 30 второй интегратор, первый вход ко842843 торого подключен к выходу источника третьего входного сигнала и триггер, первый вход которого подключен к выходу нуль-органа, введены клич, пороговый элемент и источник четвертого входного сигнала, причем вход порогового элемента подключен к выходу второго ийтегратора, выход порогового элемента подключен ко второму входу триггера, первый выход которого является выходом устройства и подключен к управляющему входу ключа, информационный вход которого подключен к выходу источника четвертого входного сигнала, выход ключа подключен ко второму входу второго интегратора, . второй выход триггера подключен к управляющему входу ключа сброса первого интегратора.

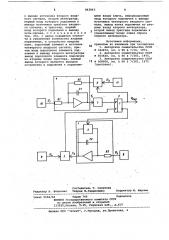

На чертеже приведена блок-схема множительно-делительного устройства

Множительно-делительное устройство содержит первый интегратор 1 с ключом 2 сброса, нуль-орган 3, второй интегратор 4, триггер 5, ключ 6, пороговый элемент 7, источники первого, второго, третьего и четвертого входных сигналов 8-11 соответственно.

Множительно-делительное устройст во работает следующим образом.

В исходном состоянии триггер 5 установлен в нулевое положение..

При подаче входного сигнала U . .на первый вход второго интегратора 4, второй интегратор 4 интегрирует его согласно уравнении » = к с к о

При U, = const V„ = U, t.Èíòåãрирование осуществляется до тех пор, пока V» не сравняется с порогом срабатывания порогового элемента 7. При срабатывании порогового элемента 7 триггер 5 по S входу устанавливается,в единичное состояние, при этом размыкается ключ 2 и замыкается ключ 6. В результате запускается первый интегратор 1, на вход которого поступает сигнал от источника 8. На второй вход второго интегратора 4 поступает входной сигнал 02 от источника

11, в полярности противоположной полярности сигнала.

Первый интегратор 1 интегрирует сигнал О> по.упавнению (l

V = — (U dt (2)

R2C2 Ъ к

const V= Ut . Ингегtttci рирование идет до момента равенства Vg и 0», которое фиксируется нуль-органом 3. При срабатывании нуль-органа 3 триггер 5 по R-входу устанавливается в нуль. Время единичного состояния триггера определяется уравнениями

К

» R3C2 Ь (3) 5 О» КЪС2 (4)

К О

Именно на ремя 1» определяемое соотношением (4), ко входу второго интегратора 4 через ключ 6 подклю10 чается напряжение 0>,,ïo знаку противоположное О, . Если параметры схе мы выбраны так, что за,время t +1; изменение напряжения на интегрирующей емкости С1 второго интегратора

4 равно нулю, то справедливо уравнение

t + t с»Х к» (к»

Т »С» " » 1 2к-»» 2, о t к к.

»»С»»к С1

Обозначая t + Ь = Т и т=—

1 т

g RU»

21 О Ъ получим

25 или с учетом (4) ИИК Еке ЦИ

" "»

ЗО

Используя различные комбинации входных воздействий, получим различные типы устройств.

35 IIPH 02 = 0» = const множительное

Е = АО 05 при О» = Оо = const, f =К-

U или 0< — U f — Ку и т д..»

Принимая в качестве выходной величины период, получим обратную зависимость

Т = — * — - 1 0 U к u u, Получение результата в частотной или временной форме позволяет прос45 тыми средствами выполнить аналогоцифровое преобразование, что расширяет область применения предлагаемого устройства.

Предлагаемое техническое решение позволяет увеличить число входных переменных и повысить точность выполняемых преобразований.

Формула изобретения

Множительно-делительное устройство, содержащее источники первого, второго итретьего входньис сигналов, первый интегратор с ключом сброса

d0 в цепи обратной связи, вход первого интегратора подключен к источнику первого входного сигнала, нульорган, один вход которого подключен к выходу первого интегратора, Я а другой вход нуль-органа подключен

8.4 2843

Составитель Т. Сапунова

Редактор A. Власенко Техред Е,Гаврилешко Корректор M. Шароши

Заказ 5104/62 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035,Иосква, Л-35, Раушская наб., д.4/5 филиал ППП "Патент", г.Ужгород, ул.Проектная, 4 к выходу источника второго входного сигнала, второй, интегратор, первый вход которого подключен к выходу источника третьего входного сигнала, и тригггер, первый вход которого подключен к выходу нуль-органа, о т л и,ч а ю щ е е с я тем, что, с целью повышения точности и увеличения количества входных переменных, в устройство введены ключ, пороговый элемент и источник четвертого входного сигнала, причем вход порогового элемента подключен к выходу второго. интегратора выход порогового элемента подключен ко.второму входу триггера, первый выход которого является выходом устройства и подключен к управляющему входу ключа, информационный вход которого подключен к выходу источника четвертого входного сигнала, выход ключа подключен ко второму входу второго интегратора, второй выход триггера подключен к управляющему входу ключа сброса первого интегратора.. Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 344454, кл. С 06 С 7/16, 1971.

2. Авторское свидетельство СССР

9 564640, кл. G 06 G 7/161, 1975.

3. Авторское свидетельство СССР

15 Р 568056, кл. G 06 G 7/161, 1975 (прототип).