Интегрирующее устройство с анало-говой памятью

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социапистических

Республик

К АВТОРСКОМУ СВИ ЕТИЛЬСТВУ (6! ) Дополнительное к ввт. саид-ву (51)М. Кл з (22) Заявлено 100676 (21) 2370392/24 с присоединением заявки Hо

G G 7/18

ГосударствеииыЯ комитет

СССР по делам изобретеииЯ и открйтиЯ (23) Приоритет

Опубликовано 3006.81, Бюллетень Ю 24

Дата опубликования описания 300р,81 (53) УДК 681 335 (088.8) A.Ä. Рябинин, A.Н. Никитин> В.Н. Яшин, Б.B. Болотов и В.А. Рябинин (72) Авторы изобретения (71) Заявитель (54) ИНТЕГРИРУЮЩЕЕ УСТРОИСТВО С АНАЛОГОВОЙ

ПАМЯТЬЮ

Изобретение относится к электронной технике и может быть использо.вано в системах распознавания, искусственных нейронных сетях; а также при создании адаптивных роботов и цифровых (гибридных) вычислительных систем.

Известны интегрирующие устройства с магнитными аналоговыми регулирующими и запоминающими устройствами, не отвечающие предъявляемым к ним требованиям, главными из которых являются линейность интегрирования, аналоговая память и высокая скорость отработки 11 .

Наиболее близким техническим решением к предлагаемому является устройство, содержащее операционный усилитель с прямым и инверсным входами, являющимися входами устройства, и магнитный аналоговый регулирующий и запоминающий блок (21, Недостатком известного устройства является его малое быстродействие, вызванное необходимостью переписывания информации.

Цель. изобретения - устранение укаэанного недостатка, т.е. повышение быстродействия устройства.

Это достигается тем, что устройство дополнительно содержит нуль. орган, первый и второй интеграторы, мультивибратор, импульсный усилитель, триггер, первый и второй ждущие мультивибраторы, расширитель .импульсов, логический элемент ИЛИ, первый, второй, третий, четвертый

1О и пятый ключи, причем выход операционного усилителя подсоединен через первый ключ ко входу первого интегратора, выход которого подключен к одному из входов нуль-органа, другой вход нуль-органа соединен с вы S ходом магнитного аналогового регулирующего и запоминающего блока, а выход подсоединен ко входам второго и третьего ключей, выходы которых подключены соответственно ко входу

2О первого и второго интеграторов, выход второго интегратора соединен через четвертый ключ ко входам импульсного усилителя, выход которого подсоединен к управляющим входам магнитного аналогового регулирующего и запоминающего блока, вход мультивибратора соединен со входом пятого ключа и счетным входом триггера, прямой выход которого через первый ждущий мультивибратор под842844 соединен к управляющему входу четвертого ключа, а инверсный выход через второй ждущий мультивибратор к управляющему входу пятого ключа, выход которого подсоединен ко входу считывания магнитного аналогового регулируюцего и запоминающего блока, выход логического элемента ИЛИ, входами подключенного ко входу устройства, соединен со входом расширителя импульсов, прямой выход которого подсоединен к управляющим входам первого и третьего ключей, а инверсный выход — к управляющему входу второго ключа.

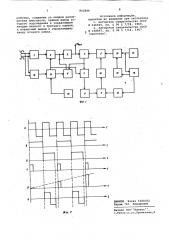

На фиг.1 изображена блок-схема предлагаемого устройства, фиг.2 иллюстрирует временное разделение процессов записи и считывания с магнитного аналогового регулирующего и запоминающего блока.

Устройство содержит операционный усилитель 1 с прямым и инверсным входами, соединенный через первый ключ 2 со входом первого интегратора 3, выход которого подсоединен к одному из входов нуль-органа 4 и одновременно является выходом интегрирующего устройства с аналоговой памятью. На другой вход нульоргана 4 подается сигнал с магнитного аналогового регулирующего и запоминаюцего блока 5, выход нульоргана 4 через второй ключ б соединен со входом первого интегратора 3 и через третий ключ 7 со входом второго интегратора 8. Выход второго интегратора 8 через четвертый ключ 9 и импульсный усилитель 10 подсоединен к управляющим входам блока 5 . Для разделения во времени процессов записи и считывания с блока 5 в устройстве используется мультивибратор 11, выход которого соединен со счетным входом триггера 12 и через пятый ключ 13 со входом считывания блока 5. Сигнал с инверсного выхода триггера 12 запускает второй ждущий.мультивибратор 14, с помощью которого осуцествляется управление пятым ключом 13. Сигнал с прямого выхода триггера 12 запускает первый ждущий мультивибратор 15, управляющий четвертым ключом 9. Импульсы управления, поступающие на прямой и инверсный вхо- . ды операционного усилителя 1, подаются на вход логического элемента ИЛИ 16, с выхода которого осуществляется запуск схемы расширителя импульсов 17. Инверсный выход расширителя импульсов 17 управляет вторым ключом 6, а прямой выход первым и третьим ключами 2 и 7. В устройстве используется схема 18 защиты, подключенная к расширителю 17 импульсов. Предлагаемое устройство полностью реализуется на интегральных элементах за исключе5 (0

20 нием навесных деталей-конденсаторов и ячейки памяти блока 5.

Устройство работает следующим образом.

В исходном состоянии (при отсутствии сигналов на прямом и инверсном входах операционного усилителя 1 на инверсном выходе расширителя

17 импульсов имеется отрицательное напряжение, а на прямом — положитель ное так,.что первый и третий ключи.

2 и 7 закрыты, а второй ключ б открыт, при этом выход нуль-органа 4 оказывается подключенным через втброй ключ б ко входу первого интегратора 3. На один из входов нуль-органа 4 поступает напряжение с первого интегратора 3, а на другой напряжение, записанное в блоке 5

При этом первый интегратор 3 оказывается включенным в цепь следящей обратной связи таким образом, что на его выходе поддерживается напряжение, равное напряжению, снимаемого с выхода блока 5 с точностью, равной величине порога

75 срабатывания нуль-органа 4.

При поступлении на прямой вход операционного усилителя 1 управляющего импульса последний усиливается. Одновременно этот же импульс через логический элемент ИЛИ 16 запускает расширитель 17 импульсов.

При этом знаки напряжений на выходах расширителя импульсов 17 изменяются, первый и третий ключи 2 и 7 открываются, а второй ключ б закрывается, причем выход операционного усилителя 1 оказывается подключенным через первый ключ 2 ко входу первого интегратора 3, а выход нуль-органа 4 через третий

40 ключ 7 оказывается подсоединенным ко входу второго интегратора 8.

Первый интегратор 3 интегрирует поступивший на его вход с выхода операционного усилителя 1 импульс, и напряжение на его выходе и на выходе всего устройства (0 „,„ ) увеличивается. Возникшая на входах нуль-органа 4 разность напряжений приводит к его срабатыванию (если величина этого рассогласования превышает напряжение порога нуль-органа 4) и на выходе нульоргана 4 появляется достаточно высокое напряжение того или иного знака в зависимости от знака напряжения рассогласования. Выходное напряжение нуль-органа 4 интегрируется вторым интегратором 8 и через четвертый ключ 9 постуйает на импульсный усилитель 10 и затем на упЩ равляющие входы блока 5. Временное разделение процессов записи и считывания с блока 5 осуществляется следующйм образом: мультивибратор

11 генерирует меандр (аиг.2а), который поступает íà c»eòHHé вход

842844

5 (О!

20 триггера 12. Триггер 12 делит частоту входного сигнала на два и положительным перепадом выходного сиг. нала с прямого выхода- (фиг.2б) запускает первый ждущий мультивибратор 15, генерирующий импульс, длительность которого несколько меньше периода сигналов„ генерируемых мультивибратором 11 (фиг.2в). Выходной импульс второго ждущего мультивибратора 14 открывает пятый ключ 13 таким образом, что из сигна— ла, генерируемого мультивибратором

11, "вырубается" биполярный импульс (фиг.2е), поступающий на вход считывания блока 5. Положительным перепадом выходного сигнала инверсного выхода триггера 12 запускается первый ждущий мультивибратор 15, который генерирует достаточно короткие импульсы (фиг.2г). Четвертый ключ 9 периодически открывается этими импульсами, осуществляя тем самым амплитудно-импульсную модуляцию (фиг.2д). Последовательность нарастающих по амплитуде импульсов напряжения, поступающих на вход импульсного усилителя 10, преобразуется в последовательность нарастающих по амплитуде импульсов тока, действующих в управляющих обмотках блока 5. Напряжение на выходе блока 5 увеличивается до тех пор, пока не станет равным выход= ному напряжению 0 „,» устройства (с точностью, равной величине порога срабатывания нуль-органа 4). При этом нуль-орган 4 включается и даль нейшее нарастание выходного напряжения блока 5 прекращается, второй интегратор 8 разряжается. Расширитель импульсов 17, защищенный входными импульсом через элемент ИЛИ

16, находится во включенном состоянии в течение времени, необходимого для завершения всех вышеописанных процессов. После этого он переходит в исходное состояние, при этом первый и третий кличи 2 и 7 закрываются, а второй ключ 6 откры-. вается, и устройство переходит в исходное состояние. В результате поступления на вход устройства управлявшего импульса и прохождения вышеописанного процесса выходное напряжение устройства (U> )увеличивается на определенную величину

С поступлением на вход устройства каждого очередного импульса выходное напряжение (И!,,» ) каждый раз соответственно увелйчивается и таким образом происходит запоминание последовательности управляющих импульсов. Выходное напряжение (U!,>>» ) прямо пропорционально числу запомненных управляющих имI пульсов. Для предотвращения ложного срабатывания расширителя 17 импульсов при включении и выключе25

ЗО

4. :

65 нии питающих напряжений, устройствс содержит блок 18 защиты, подключенный к одному из входов расширителя

17 импульсов.

Таким образом, обладая высоким быстродействием, достаточно большим объемом памяти и, высокой стабильностью, а также возможностью исполнения на интегральных элементах, предлагаемое устройство позволит значительно расширить круг задач, решаемых цифровыми.и гибридными вычислительными системами, и кроме того, дает возможность приступить к созданию самонастраивающихся распознающих нейронных сетей, что в свою очередь позволит проектировать адаптивные роботы промышленного и специального назначения.

Формула изобретения

Интегрирующее устройство с аналоговой памятью, содержащее операционный усилитель с прямым и инверсным входами, являющимися входами устройства, и магнитный аналоговый регулирувщий и эапоминаиций блок, о т л и ч а и щ е е с я тем, что, с целью повышения быстродействия, оно дополнительно содержит нуль-орган первый и второй интеграторы, мультивибратор, импульсный усилитель, триггер, первый и второй ждущие мультивибраторы, расширитель импульсов, логический элемент ИЛИ и первый, второй, третий, четвертый и пятый кличи, причем выход операционного усилителя подсоединен через первый клич ко входу первого интегратора, выход которого подключен к одному их входов нуль-органа, другой вход нуль-органа соединен с выходом магнитного аналогового регулирувщего u запоминающего блока, выход подсоединен ко входу второго и третьего ключей, выходы которых подключены соответственно ко входу первого и второго интеграторов, выход второго интегратора соединен через четвертый клич со входом импульсного усилителя, выход которого подсоединен к управляющим входам магнитного аналогового регулирующего и запоминающего блока, выход мультивибратора соединен со,входом .пятого клвча и со счетно входом триггера, прямой выход которого через первый ждущий мультивибратор подсоединен к управляищему входу четвертого ключа, а инверсный выход через второй ждущий мультивибратор к управляющему входу пятого ключа, выход которого подсоединен ко входу считывания магнитного аналогового регулирующего и запоминающего блока, выход логического элемента ИЛИ, входами подключенного ко входу уст842844

Pvc. 1 ройства, соединен со входом расширителя импульсов, прямой .выход которого подсоединен к управляющим входам первого и третьего ключей, а инверсный выход к управляющему входу второго ключа.

Источники инФормации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 246929, кл. G 06 G 7/18, 1969.

2. Авторское свидетельство СССР

Р 238897, кл. G 06 G 7/14, 1967 (прототип).

ВНИИПИ Заказ 5104/62

Тираж 745 Подписное

Филиал ППП Патент, r.Ужгород,ул.Проектная,4