Интегратор с запоминанием

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик I

> (б1) Дополнительное к авт. саид-ву (22) Заявлено 160779 (21) 2798267/18-24 (5 )М

Государственный комитет

СССР по делам изобретений и открытий с присоединением заявки HP (23) Приоритет

G G 7/18

G 11 С 27/00

Опубликовано 30,06.81. Бюллетень ЙЯ 24 (53) УДК 681. 335 (088.8) Дата опубликования описания 300681. (72) Авторы изобретения

С.Д. Лутов и 0.К. Цыганков

1

iг

I ! (71) Заявитель

Ордена Ленина институт кибернетики

AH Украинской ССР (54) ИНТЕГРАТОР С ЗАПОМИНАНИЕМ

Изобретение относится к автомати- ке и вычислительной технике и может использоваться в различных моделирующих и управляющих устройствах для интегрирования и (или) запоминания аналоговых сигналов на больших интервалах времени.

Такой интегратор . с запоминанием может использоваться в качестве. Уст ройства запоминания управляющих воздействий, поступающих от ЭВМ к аналоговым исполнительным устройствам в системах автоматического управления различными объектами, в частности инерционными технологическими процессами в химической и других отраслях промышленности.

Известны аналоговые интегрирующие и запоминающие устройства, использующие.в качестве накопительного элемента конденсатор, сохранение уровня напряжения на котором в режиме хранения (памяти) обеспечивается специальной схемой коррекции (11.

Известна аналоговая схема с компенсацией дрейфа, в которой компенсация двухнаправленного дрейфа достигается значительным усложнением схемы, так как цепь компенса2 ции, по существу дублируется для положительного и отрицательного дрейфа j2).

Наиболее близким по технической сущности к предлагаемому является интегратор с запоминанием, содержащий операционный усилитель с интегрирующим конденсатором в цепи отрицательной обратной связи, установ1О лены коммутирующие элементы, командные входы которых соединены с шиной управления режимом работы интегратора. К первому из коммутирующих элементов подсоединена об-, 15 щая точка элементов входной цепи (в данном случае это параллельно включенные резистор и конденсатор), а ко второму подключен выход элемента цепи коррекции (два встреч20 но-параллельно включенных диода)

Выход этого,:элемента подключен к выходу генератора корректирующих импульсов и к третьему коммутирующему элементу, выход которого соединен с шиной нулевогс потенциала, а командный вход подключен к выходу одновибратора, установленного на,выходе .компаратора. Один вход компаратора соединен с выходом опеЗО рационного усилителя, являющимся

842845

60 выходом устройства, а его другой вход подключен к выходу генератора пилообразного напря:хения, соединенного также с одним из входов вспомогательного компаратора, другой вход которого соединен с шиной опор ного напряжения,.а выход — co входо л блокировки генератора корректирующих импульсов. Входы синхронизации генераторов соединены с выходом операционного усилителя (3).

Это устройство достаточно сложно из-за наличия в цепи коррекции двух коммутирующих элементов, необходимости иметь разнополярный выход у генератора корректирующих импульсов и использования в каждом интеграторе своего генератора пилообразного напряжения и генератора корректирую щих импульсов, так как они синхронизируются or выходного напряжения устройства. Это затрудняет использование устройства в блоках долговременных аналоговых запоминающих устройств с применением современных логических микросхем, которые в большинстве случаев являются однополярными. Кроме того, устройст во отличается повышенным потреблением,энергии в цепи коррекции, так как, с одной стороны, мощность гене ратора корректирующих импульсов должна бить достаточно большой для обеспечения требуемой коррекции (заряда конденсатора.в коротких проме:хутках времени), а, с другой стороны, выход этого генератора большую часть периода коррекции заземлен через коммутирующий элемент.

Цель изобретения — упроцение устройства и снижение потребляемой энергии.

Поставленная цель достигается тем, что в интегратор с запоминанием, содержаций операционный усилитель, вход которого через интегрирующий конденсатор подключен к его выходу, через последовательно соединенные первый коммутирующий элемент и входной импеданс соединен со входом интегратора и через последовательно соединенные второй коммутирующий элемент и ограничивающий элемент подключен к выходу компаратора и входу одновибратора, Управляющий вход первого коммутирую щего элемента подключен к входу управления режимом работы интегратора, генератор пилообразного напряжения и генератор корректирующих импульсов, введен элемент И, при.чем выход одновибратора соединен с управляющим входом второго коммутирующего элемента и первым входом элемента И, второй вход которого подключен к выходу генератора корректирующих импульсов, выходы элемента И и генератора пилообразного напряжения соединены соответст5 !

О

50 венно с первым и вторым входами компаратора, третий вход которого подключен к выходу операционного усилителя, вход блокировки одновибратора подключен к входу управления режимом работы интегратора, а к входу синхронизации генератора пилообразного напряжения подключен выход генератора корректирующих импульсов.

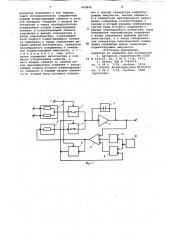

На фиг.1 приведен интегратор, структурная схема, на фиг.2 — временная диаграмма,. поясняющая его работу.

Интегратор с запоминанием (фиг.1) содержит операционный усилитель 1 с интегрируюцим конденсатором 2 в цепи отрицательной обратной связи.

На входе операционного усилителя 1 установлены коммутирующие элементы 3 и 4, к первому из которых подключен входной импеданс 5 (эта цепь может иметь несколько входов) а ко второму подсоединен выход ограничивающего элемента б цепи коррекции. Управляющий вход первого коммутируюцего элемента 3 подключен к входу 7 управления режимом работы интегратора, а второго 4 — к выходу одновибратора 8, соединенному также с одни л из входов элемента И 9, другой вход которого соединен с выходом генератора корректи руюцих импульсов 10. Вход ограничивающего элемента б цепи коррекции и вход одновибратора 8 подключены к выходу компаратора 11, одий вход которого соединен с выходом интегратора, другой вход соединен с вы-, ходом генератора 12 пилообразного напряжения, а третий . — с выходом элемента И 9. Вход блокировки одновибратора 8 соединен с входом 7 управления режимом работы интегратора, а вход синхронизации генератора

12 пилообразного напряжения подключен к выходу генератора 10 корректи рующих импульсов.

Интегратор с запоминанием работает следующим образом.

В исходном положении, соответствующем режиму интегрирования входных сигналов, коммутирующий элемент

3 находится в замкнутом состоянии, а коммутирующий элемент 4 — в разомкнутом, так как одновибратор 8 блокируется командным сигналом с входа 7 управления режимом работы интегратора. При этом устройство работает как обычный емкостный интегратор суммарного тока, поступающего на вход операционного усилителя 1 через входной импеданс 5. Заметим, что при подключении одного из входов этой цепи к выходу операционного усилителя 1, устройство реализует функции инерционного звена.

Такое включение применяется при использовании предлагаемого интег842845 ратора в функции аналогового запоминающего устройства и позволяет повысить его быстродействие в режиме записи входных сигналов.

При подаче команды с входа 7 на .запоминание заинтегрированного ("записанного") напряжения коммутирующий элемент 3 размыкается, а одновибратор 8 деблокируется и периодически замыкает коммутирующий элемент 4, обеспечивая прохождение на вход операционного усилителя 1 корректирующих импульсов из цепи коррекции, включающей элементы б, 8... 12. Формирование им.пульсов коррекции представлено на временной диаграмме (фиг.2).

Компаратор 11 сравнивает напря>кение U„„ с выхода генератора пилообразного напря><ения 12 и выходное напряжение интегратора U, (фиг.2а). Последнее под действием дрейфовых токов на входе операционного усилителя 1 может изменяться в ту или иную сторону от запоминаемого уровня. При этом изменяется момент времени t (фиг.26) когда выполняется равенство U „„ = U,„„ и компаратор 11 изменяет свое состояние, запуская одновибратор 8, который выдает и>лпульс определенной длительности ь,> (фиг26). Этот импульс замыкает коммутирующий элемент 4, сое диняющий выход элемента б цепи коррекции со входом операционного усилителя 1, и одновременно разрешает проходить на выход элемента И 9 корректирующим импульсам от генератора 10 (фиг.2в) . Длительность импульса одновибратора выбрана равной или меньшей полупериода напряжения U«> корректирующих импульсов с генератора 10 гг>ь» 1/2 Tppp),, Период напряжения Ul- ц генератора

12 синхронизирован импульсами с генератора 10, т.е. выполняется Т „„ = п.Т» „, где и — число ступенчатой коррекции, определяющих точность поддер>кивания запоминае>лого напря>кения (обычно n=250-500, что соответствует погрешности 0,2-0,1Ъ).

Поэтому при изменении -момента t появления импульса одновибратора (фиг.2б) изменяется его взаимное расположение относительно импульсов генератора 10 и на выходе элемента И 9 возможны четыре различных случая наложения импульсов одновибратора 8 и генератора 10, по-. казанные на фиг.2г.

Импульсы с выхода элемента И 9 поступают на компаратор 11, например, на неинвертирующий вход его дифференциального усилителя с разнополярным выходом, на основе которого обычно выполняется компаратор, сравнивающий разнополярные входные сигналы. Таким образом, после изменения состояния компаратора в (О

Интегратор с запоминанием, содержащий операционный усилитель, вход которого через интегрирующий кон20

ЗО

55 момент t (фиг.2д) из "+" в "-" он может снова вернуться в предшествующее состояние по команде импульса с выхода элемента,И 9. Различные случаи изменения напряжения на Выходе компаратора на интервале Т показаны на фиг.2д, а форма импульсов коррекции на входе операционного усилителя 1 (т.е. импульсов тока с выхода компаратора 11 через элемент б и замкнутый ключ 4) показана на фиг.2е. Как видно в случаях I u IV результирующая коррекция близка к нулю, в случае II импульс корректирующего тока отрицательный, а в случае III — положительный. Точка равновесия в случае

I является неустойчивой, а в случае

IV — устойчивой.

Таким o6pазом, благодаря включению на входе компарагора элемента Р определяющего изменение взаимного расположения импульсов одновибратора и генартора корректирующих импульсов, более эффектно используются функциональные и технические воз>ложности ко>лпаратора — он выполняет как функции элемента сравнения, так и формирователя импульсов коррекции требуемой попярности беэ усложнения схемы и при снижении потребляемой общей .энергии, так как отбор мощности компаратора производится в очень короткие промежутки времени (Yo+) . Отметигл также, что импульсы на выходе одновибратора, генератора корректирующих импульсов и элемента И являются однополярными что упрощает реализацию этих элементов в предлагаемом устройстве,, в частности, для этого могут быть использованы современные интегральные микросхемы однополярной логики

Блокировка одновибратора в режиме интегрирования входных сигналов устройства также позволяет упростить его, так как из схемы исключается один коммутирующий элемент, использовавшийся в известном устройстве.

Синхронизация генератора пило образного напряжения от генератора корректирующих импульсов позволяет испольэовать эти генераторы как общие элементы для нескольких интеграторов C .sànoìèíaíèåì, что также упрощает их реализацию.

Предлагаемый интегратор с запоминанием используется в устройстве ввода данных анализаторов для обработки и запоминания хроматографических сигналов.

Формула изобретения

842845 денсатор подключен к его выходу, через последовательно соединенные первый коммутирующий элемент и вход ной импеданс соединен с входом интегратора и через последовательно соединенные второй коммутирующий элемент и ограничивающий элемент подключен к выходу компаратора и входу одновибратера, управляющий вход первого коммутирующего элемента подключен к входу управления режимом работы интегратора, генератор пилообразного напряжения и генератор корректирующих импульсов, о т л и ч а ю шийся тем, что,с целью упрощения интегратора и снижения потребляемой энергии, в него введен элемент И, причем выход одновибратора соединен с управ-, ляющим входом второго коммутирующего элемента и первым входом элемента И, второй вход которого подключен к выходу генератора корректирующих импульсов, выходы элемента

И и генератора пилообразного напряжения соединены соответственно с первым и вторым входами компаратора третий вход которого подключен к выходу операционного усилителя, вход блокировки одновибратора подключен к входу управления режимом работы интегратора, а к входу синхронизации генератора пилообразного напряжения подключен выход генератора корректирующих импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

15 В 424165, кл. G 06 G 7/18, 1972.

2. Патент СИА Р 3784919, кл. G 06 G 7/18, опублик. 1974.

З.Патент Великобритании 91274191 кл. G 06 G 7/18, опублик. 1968 (прототип).

Составитель С. Белан

Редактор A. Власенко Техред M.долинка Корректор М. лароши

Заказ 5104/62 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Л 35 Раушская наб,О.д,4/5

Филиал ППП " атент", Г..ужгород, ул.Проектная, 4