Формирователь тока выборки дляблоков памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

М АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик (ii)842954 (61) Дополнительнде к авт. свид-ву— (22) Заявлено 29.06.79 (21) 2786148/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К .

G 11 С 7/00.Гесудлрстеенный кемнтет

l (53) УДК 628.327. .6 (088.8) Il0 делам нэебретеннй н етнрытнй

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 (72) Авторы изобретения

В. 3. Авсеев, В. В. Балабин и В. А. Милосл вов

В;,:,: ..;-:., =у

П:, l (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ ДЛЯ БЛОКОВ ПАМЯТИ

Изобретение относится к вычислительной технике и может найти применение при создании магнитных запоминающих устройств (ЗУ) в качестве формирователей токов выборки адресных цепей.

Известен формирователь тока выборки, содержащий входное и выходное устройства с трансформаторной связью между ними (1j

Недостатком известного формирователя тбка выборки является наличие в нем межкаскадного трансформатора связи, приводящего к искажению фронта импульса тока выборки, ограничению быстродействия и ограничению степени возможной интеграции.

Наиболее близким по технической сущности к предлагаемому техническому решению является формирователь тока выборки, который содержит ключевые транзисторные входной и выходной каскады, выполненные на транзисторах е-р-п, и р-л;р типах проводимости. Входной каскад выполнен на транзисторе и;-р-п, ттииппаа, база которого через первый резистор подключена ко входу формирователя, к которому подключен второй резистор. Другой вывод резистора соединен с источником питания. Коллектор данного транзистора через резистор соединен с базой транзистора р-и-р типа выходного каскада, эмиттер последнего через резистор соединен с базой и подключен к источнику положительного смещения. Отсутствие трансформатора связи между входным и выходным каскадом в этом формирователе тока выборки улучшает форму импульса тока выборки, обеспечивая достаточно крутые фронты импульса тока и обладает диапазоном рабочих частот до 500 кГц при амплитуде выходного импульса порядка 300 мА те и позволяет осуществить непосредственно управление от комплекса логических схем (2) .

Однако транзистор выходного транзисторного каскада, выполненного в виде ключа напряжения, работает в режиме насыщения, внося задержки при входе в насыщение транзистора и выходе из него. Это приводит к ограничению быстродействия формирователя тока выборки. Кроме того, в ключе напряжения нарастание тока через индуктивность происходит по экспоненциальному закону с постоянной времени; прямо пропорциональной индуктивной составляющей нагрузки, значительная величина ко8429511

55 торой характерна для адресных шин магнитных ЗУ, что приводит к затягиванию фронта импульса тока выборки, ухудшая временные параметры ЗУ.

Для уменьшения длительности фронта импульса тока необходимо увеличивать активную составляющую нагрузки, величина которой связана с длительностью фронта тока обратно пропорциональной зависимостью.

Это приводит к необходимости увеличения номинала положительного смещения, сохраняя требования к его стабильности.

В результате снижаются весогабаритные показатели блока питания магнитных ЗУ, в которых используются эти формирователи.

Последнее время быстро развиваются ЗУ на тороидальных сердечниках с прямоугольной петлей гистерезиса, в которых использован режим частичного переключения магнитного потока для повышения быстродействия, и на запоминающих элементах со считыванием- без разрушения типа биакс, что приводит к возникновению необходимости формирования тока выборки с высокими временными характеристиками (малая длительность

50 — 100 нс и период следования 150 — 200 нс).

Цель изобретения — повышение надежности формирователя (меньшая длительность, крутой фронт, высокая частота повторения).

Поставленная цель достигается тем, что формирователь тока выборки содержит ключевые входной и выходной каскады, выполненные на транзисторах различного типа проводимости, при этом база транзистора ключевого транзисторного выходного каскада соединена с источником питания через первый резистор, ключевой выходной каскад формирователя содержит второй резистор, включенный между источником питания Е и эмиттером транзистора ключевого выходного каскада, база транзистора которого соединена с коллектором транзистора ключевого входного каскада.

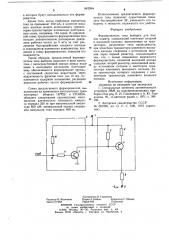

На чертеже представлена принципиальная электрическая схема формирователя тока выборки.

Формирователь тока выборки содержит транзисторные ключевые входной 1 и выходной 2 каскады, выполненные на транзисторах

3 и 4 различного типа проводимости (на приведенной схеме и;р-п, и р-и;р типа), первый и второй резисторы 5 и 6 транзисторного ключевого каскада, источник 7 питания, нагрузку 8 и источник 9 напряжения смещения, полярность которого противоположна полярности источника 7 питания. Транзисторный ключевой входной каскад 1 содержит третий и четвертый резисторы 10 и 11.

Общая точка 12 связи третьего и четвертого резисторов 10 и 11 является входом формирователя тока выборки. Нагрузка 8 в состав предлагаемого устройства не входит и изображена на чертеже лишь для пояснения работы формирователя.

5 о

zo

25 зо

4

Формирователь тока выборки работает следующим образом.

В статическом состоянии, т.е. при отсутствии сигналов выборки потенциал точки

12, определяемый исходным состоянием выходного каскада логической схемы управления, низкий и транзистор 3 транзисторного ключевого входного каскада 1 находится в режиме отсечки; Транзистор 4 транзисторного ключевого выходного каскада 2 на ходится также в режиме отсечки, что обеспечивается выбором определенного номина.— ла первого резистора 5. При поступлении на вход формирователя тока выборки положительного импульса транзистор 3 транзисторного ключевого входного каскада 1 переходит в режим насыщения, что обеспечивается выбором определенного номинала третьего резистора 10 и четвертого резистора

11, фиксируя потенциал базы транзистора 4 тра нзисторного ключевого выходного каскада около уровня земли. Так как между эмиттером транзистора 4 транзисторного ключевого выходного каскада и источником

7 питания включен второй резистор 6 отрицательной обратной связи, то транзистор

4 находится в активном режиме. В комплексной нагрузке 8 протекает ток выборки, величина которого определяется номиналами второго резистора б и источника 7 питания и практически не зависит от величины напряжения источника 9 смещения.

Ток через индуктивную составляющую нарастает линейно и время нарастания тока при прочих равных условиях примерно в 2 раза быстрее„чем в известном формирователе.

По окончании входного сигнала транзистор 3 транзисторного ключевого входного каскада 1 и транзистор 4 транзисторного ключевого выходного каскада 2 переходят в исходное состояние (режим отсечки), прерывая ток в нагрузке.

Построение формирователя тока с непо- . средственной связью между входными и выходными транзисторными ключевыми каскадами, выходной каскад которого выполнен в виде ключа тока, обеспечивает высокие временные характеристики и стабильность адресных токов выборки магнитных ЗУ. Это позволяет существенно повысить быстродействие этих ЗУ, особенно ЗУ на тороидальных сердечниках с прямоугольной петлей гистерезиса, в которых использован режим частичного переключения потока и на сердечниках со сложным магнитопроводом, в которых считывание происходит без разрушения информации, так как быстродействие этих магнитных ЗУ в основном зависит от быстродействия электронного обрамления.

Вместе с тем, в предлагаемом формирователе тока выборки снимаются требования к стабильности и величине номинала источника Е, что приводит к понижению весогабаритных показателей блока питания ЗУ, 842954

Формула изобретения

Составитель В Гордонова

Редактор В.Матюхина Техред А. Бойкас Корректор С. Щомак

Заказ 5119/68 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, % — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 в которых будут использоваться эти формирователи.

Кроме того, когда требуемая амплитуда тока не превышает 160 мА, в качестве входного каскада можно использовать транзисторно-транзисторную логическую интегральную схему, например, 133 серии. В упрощенной схеме предлагаемого формирователя происходит дополнительное расширение диапазона рабочих частот до 5 мГц за счет увеличения быстродействия. входного каскада и сокращается количество компонентов, входящих в схему формирователя, повышая его надежность.

Таким образом, предлагаемый формирователь тока выборки выполнен в виде ключа тока с непосредственной связью между входными и выходными каскадами, благодаря чему обеспечивается формирование крутых, с постоянной скоростью нарастания через индуктивность фронтов тока (до 10 нс), исключаются задержки насыщения, расширяя диапазон рабочих частот формирователя.

Схема предлагаемого формирователя, выполненная на кремниевых интегральных транзисторных сборках 1НТ251 и 2ТС622А, обладает следующими параметрами: минимальная длительность выходного импульса порядка 250 нс при максимальной.амплитуде 600 аМ; минимальный период следования импульсов тока порядка 400 нс.

Использование предлагаемого формирователя тока позволяет существенно повысить быстродействия ЗУ, уменьшить его габариты и повысить надежность его работы.

Формирователь тока выборки для блоков памяти, содержащий ключевые входной и выходной каскады, выполненные на транзисторах, различного типа проводимости, 10 при этом база транзистора ключевого выходного каскада соединена с источником питания через первый резистор, отличающийся тем, что, с целью повышения надежности формирователя, ключевой выходной каскад содержит второй резистор, включенный между источником питания и эмиттером транзистора ключевого выходного каскада, база транзистора которого соединена с коллектором транзистора ключевого входного каскада.

20 Источники информации, принятые во внимание при экспертизе

1. Специальные элементы запоминающих устройств ЭВМ на полупроводниковых приборах.Под ред. Е. И. Гальперина.и А. Ю. Гордонова. М., «Советское радио», 1971, с. 189" 195.

2. Авторское свидетельство СССР № 381095, кл. G 11 С 7/00, 1973 (прототип).