Запоминающее устройство

Иллюстрации

Показать всеРеферат

АНИЕ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИЯЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 06.07.79 (21) 2791171/18-24 (51) М. Кл.з с присоединением заявки №вЂ” (23) Приоритет—

G 11 С 11/00

Гееуддрстеенный кемнтет

СССР (53) УДК 681.327 (088.8) I

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81

ho делам нзебретеннй.н еткрмтий (72) Авторы (54) ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

Изобретение относится к запоминающим устройствам и может быть использовано для построения оперативных запоминающих устройств с частичным резервированием накопителя.

Известно запоминающее устройство; содержащее регистр адреса, причем нулевые 3 выходы последнего подключены к одним из входов элементов И первой и второй групп, другие входы которых соединены соответ ственно с входами устройства и выходами одноразрядных блоков памяти, а выходы подключены соответственно к входам одноразрядных блоков памяти и выходам устройства и резервный одноразрядный блок памяти (1) .

Недостатком этого устройства является его низкая надежность.

Наиболее близким техническим решением к предлагаемому является запоминающее устройство, содержащее регистр адреса, нулевые выходы которого подключены к одному из входов элементов И первой и вто- 2h рой групп, другие входы которых соединены. соответственно с входами устройства и выходами одноразрядных блоков памяти, а выходы подключены соответственно к входам одноразрядных блоков памяти и выходам устройства, резервный одноразрядный блок памяти, третью, четвертую и пятую группы элементов И, причем первые входы элементов И третьей и четвертой групп подключены к единичным выходам регистра адреса, вторые входы — соответственно к входам устройства и выходу резервного одно/ разрядного блока памяти, а выходы — соответственно к входу резервного одноразрядного блока памяти и выходам устройства, первые входы элементов И пятой группы соединены с входами устройства, вторые входы — с управляющей шиной, а выходы — с входами регистра адреса, нулевые выходы регистра адреса подключены к входам первого элемента И, выход которого. соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены соответственно к входной контрольной шине и выходу резервного одноразрядного блока памяти, а выходы — соответственно к входу резервного одноразрядного блока памяти и выходной контрольной шине (2).

Однако возмоЖная потеря информации после исключения неисправности и ограни842955 ченная возможность дистанционного управления при устранении неисправности снижает надежность его работы.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее группу накопителей, триггеры, группу элементов ИЛИ, пять групп элементов И, накопитель, элементы И и первый элемент ИЛИ, причем первые входы элементов И первой, второй и пятой групп являются информаци- 10 онными входами устройства, выходы элементов И первой группы соединены соответственно со входами накопителей группы, выходы которых подключены соответственно к первым входам элементов И третьей группы, вто- 5 рые входы элементов И первой и третьей групп соединены соответственно с нулевыми выходами триггеров и входами первого элемента И, выход которого подключен к первым входам второго и третьего элементов И и вторым входам элементов И пятой груп- 20 пы, выходы которых соединены соответственно с единичными входами триггеров, .выход второго элемента И подключен к одному из входов первого элемента ИЛИ, другие входы которого соединены соответственно с выхо25 дами элементов И второй группы, выход первого элемента ИЛИ подключен ко входу накопителя, выход которого соединен со вторым входом третьего элемента И и первыми входами элементов И четвертой группы, вторые входы элементов И второй и четвертой групп подключены к единичным выходам триггеров соответственно, выходы элементов

И третьей и четвертой групп соединены соответственно с первыми и со вторыми входами элементов ИЛИ группы, выходы которых являются информационными выходами уст- 3 ройства, второй вход второго и выход третьего элементов И являются соответственно контрольными входом и выходом устройства, введены два генератора импульсов, счетчик, элемент задержки, дешифратор и второй элемент ИЛИ, причем выход первого генератора

-:Mïóëüñîâ соединен с первым входом второго элемента ИЛИ и установочным входом счетчика, выход которого подключен ко входу дешифратора, выходы которого соединены с третьими входами элементов И пятой груп- 4 пы соответственно, выход второго элемента

ИЛИ подключен к нулевым входам триггеров, а второй вход — к выходу второго генератора импульсов и входу элемента задержки, выход которого содинен со счетным входом счетчика.

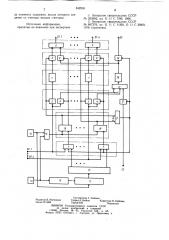

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит группу накопителей 1, группу элементов ИЛИ 2, первую 3, вторую 4, третью 5, четвертую 6 и пятую 7 группы элементов И, первый 8, второй 9 и третий 10 элементы И, первый 11 и второй

12 элементы ИЛИ, первый 13 и второй 14 генераторы импульсов, дешифратор 15, элемент 16 задержки, счетчик 17, накопитель

18, являющийся резервным, и триггеры 19.

Устройство имеет входы 20.1 — 20.п и выходы 21.1 — 21.К а также контрольные вход

22 и выход 23.

Первые входы элементов И первой 3, вто- рой 4 и пятой 7 групп являются информационными входами 20.1 — 20.п устройства. Выходы элементов И первой 3 группы соединены соответственно со входами накопителей 1 группы, выходы которых подключены соответственно к первым входам элементов И третьей 5 группы. Вторые входы элементов И первой 3 и третьей 5 групп соединены соответственно с нулевыми выходами триггеров

19 и входами первого элемента И 8, выход которого подключен к первым входам второго 9 и третьего 10 элементов И и вторым входом элементов И пятой 7 группы, выходы которых. соединены соответственно с единичными входами триггеров 19. Выход второго элемента И 9 подключен к одному из входов первого элемента ИЛИ 11, другие входы которого соединены соответственно с выходами элементов И второй группы 4. Выход первого элемента ИЛИ 11 подключен ко входу накопителя 18, выход которого соединен со вторым входом третьего элемента

И 10 и первыми входами элементов И четвертой 6 группы. Вторые входы элементов И второй 4 и четвертой 6 групп подключены к единичным выходам триггеров 19 соответственно. Выходы элементов И третьей 5 и четвертой 6 групп соединены соответственно с первыми-и со вторыми входами элементов

ИЛИ 2 группы, выходы которых являются информационными выходами 21.1 — 21.п устройства. Второй вход второго 9 и выход третьего 10 элементов И являются соответственно контрольными входом 22, и выходом 23 устройства.

Выход первого генератора импульсов 13 соединен с первым входом второго элемента ИЛИ 12 и установочным входом счетчика 17, выход которого подключен ко входу дешифратора 15, выходы которого соединены с третьими входами элементов И пятой 7 группы соответственно. Выход второго элемента ИЛИ 12 подключен к нулевым входам триггеров 19, а второй вход — к выs ходу второго 14 генератора импульсов и входу элемента 16 задержки, выход которого соединен со счетным входом счетчика 17, Накопители 1 группы и накопитель 18 являются одноразрядными. Триггеры 19 выполняют функции регистра адреса.

Устройство" работает следующим образом.

После подачи питающих напряжений на запоминающее устройство (ЗУ) первый 13 генератор импульсов вырабатывает сигнал, 5 который устанавливает счетчик 17 и триггеры 19 в нулевое состояние. Сигналы высокого уровня на нулевых выходах триггеров

19 открывают элементы первой 3 и второй

4 группы, а также первый элемент И 8.

842955

Запись числа в накопители 1 группы происходит через открытые элементы И первой

3 группы, а чтение — через открытые элементы И третьей 5 группы и элементы ИЛИ 2.

Запись контрольного сигнала в одноразрядный накопитель 18- происходит через открытый второй элемент И 9 и первый элемент ИЛИ 11, а чтение — через открытый третий элемент И 10. Накопитель 18 выполняет функцию контрольного разряда на четность (нечетность) информации накопителей 1 группы.

Устранение неисправности в одном из множества неисправных разрядов ЗУ производится следующим образом. На информационные входы 20.1 — 20.п подается код, состоящий из нулевых и единичных сигна- 1 лов. Нулевые сигналы кода соответствуют исправным разрядам — ЗУ, т.е. накопителя

1 группы, а единичные сигналы — неисправным. Выбирается любой накопитель 1 группы, в котором необходимо устранить неисправность. Зная порядковый номер этого 20 накопителя 1 группы, т.е. разряда ЗУ (например, 10-й разряд), оператор производит запуск второго 14 генератора импульсов (например путем 10-кратного нажатия специальной кнопки). Сигналы с выхода генератора 14 импульсов через элемент 16

25 задержки поступают на счетный вход счетчика 17 и устанавливают его в состояние, соответствующее числу поступающих на его вход сигналов. Состояние счетчика дешифрируется дешифратором 15; с выхода которого сигнал поступает на третий вход элемента И 10 пятой 7 группы, который открывается и пропускает единичный сигнал десятого разряда кода на единичный вход соответствующего триггера 19. После установки выбранного триггера 19 в единичное состоя- 35 ние остальные триггеры 19 продолжают находиться в нулевом состоянии. Элементы И первой 3 и третьей 5 групп, подключены к нулевому выходу выбранного, например десятого, триггера 19, установленного в единичное состояние, закрываются, а элементы И второй 4 и четвертой 6 групп, подключенные к единичному выходу выбранного триггера

19, открываются и соединяют выбранный информационный вход 20.1 — 20.п со входом

° накопителя 18, а его выход — с соответст- 4 вующим информационным выходом 21.1—

21.п устройства. При этом неисправный накопитель 1 группы блокируется и вместо него подключается резервный накопитель 18.

Одновременно закрывается первый элемент

И 8, так как на один из его входов подан 50 сигнал низкого уровня с нулевого выхода выбранного триггера 19, который установлеи в единичное состояние. При этом элементы И пятой 7 группы закрываются и блокируют триггеры 19 по вторым входам, что исключает установку в единичное состояние других триггеров 19. Выключаются также второй 9 и третий 10 элементы И, которые прерывают цепи для сигналов с контрольного входа 22, на вход резервного накопителя 18 и с его выхода — на контрольный вход

22 устройства. При этом контроль на четность (нечетность) в ЗУ не производится.

Технико-экономическое преимущество предлагаемого устройства по сравнению с известным заключается в повышении надежности за счет введения двух генераторов импульсов, счетчика, дешифратора и новых связей, обеспечивающих частичное резервирова ние на ко пителя.

Формула изобретения

Запоминающее устройство, содержащее группу накопителей, триггеры, группу элементов ИЛИ, пять групп элементов И, накопитель, элементы И и первый элемент

ИЛИ, причем первые входы элементов И первой, второй и пятой групп являются информационными входами устройства, выходы элементов И первой группы соединены соответственно со входами накопителей группы, выходы которых подключены соответственно к первым входам элементов И третьей группы, вторые входы элементов И первой и третьей групп соединены соответственно с нулевыми выходами триггеров и входами первого элемента И, выход которого подключен к первым входам второго и третьего элементов И и вторым входам элементов

И пятой группы, выходы которых соединены соответственно с единичными входами триггеров, выход второго элемента И подключен к одному из входов первого элемента ИЛИ, другие входы которого соединены соответственно с выходами элементов И второй группы, выход первого элемента ИЛИ подключен ко входу накопителя, выход которого соединен со вторым входом третьего элемента И и первыми входами элементов И четвертой группы, вторые входы элементов И второй и четвертой групп подключены к единичным выходам триггеров соответственно, выходы элементов И третьей и четвертой групп соединены соответственно с первыми и со вторыми входами элементов ИЛИ группы, выходы которых являются информационными выходами устройства, второй вход второго и выход третьего элементов И являются соответственно контрольными входом и выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит генераторы импульсов, счетчик, элемент задержки, дешифратор и второй элемент ИЛИ, причем выход первого генератора импульсов соединен с первым входом второго элемента ИЛИ и установочным входом счетчика, выход которого подключен ко входу дешифратора, выходы которого соединены с третьими входами элементов И пятой группы соответственно, выход второго элемента ИЛИ.подключен к нулевым входам триггеров, а второй вход — к выходу второго генератора импульсов и вхо842955

Составитель T. Зайцева

Редактор В. Матюхина Техред A. Бойкас Клрректор Н. Бабинец

Заказ 5119/68 Тираж 545 Подписное

ВНИИПИ Государственного комитета СССР по дела м изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ду элемента задержки, выход которого соединен со счетным входом счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 263682, кл. G 11 С 7/00, 1966.

2. Авторское свидетельство СССР № 607276, кл, G 11 С 11/00, G 11 С 29/00, 1978 (прототип).