Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Реслублик

ОП ИСАНИ Е „,)Я42962

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 21.08.79 (21) 2814119/18-24 с присоединением заявки №вЂ” (51) М. Кл.

0 11 С 15/00

Гасударственные камитет (23) Приоритет— (53) УДК 681.327 (088.8) Опубликовано 30.06.81. Бюллетень №24

Дата опубликования описания 05.07.81 ао делам изебретеиий и еткрытий

Д. А. Тодуа, Т. А. Клдиашвили, Г. А. Бакши, Н. Н. Ш бурова, " т f f. / т;

Н. А. Шемйгин, В. К. Хачатуров и О. Е. Жуковс (72) Авторы . изобретения

Тбилисский научно-исследовательский институт приборостроения средств автоматизации Научно-производственного объединения «Элва» (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно ассоциативное запоминающее устройство (АЗУ), содержащее элементы памяти, блоки записи, формирователи опросных токов, регистр опроса, детекторы (1).

Недостатком этого устройства являются большие аппаратурные затраты.

Наиболее близким техническим решением к предлагаемому является АЗУ, содержащее матрицу элементов ассоциативной памяти, каждый из которых содержит запоминающую ячейку, блок считывания, блок сравнения, две группы блоков выдачи, три группы входных элементов НЕ, а также входные шины поиска (записи),шины выбора строки,. выходные шины считывания и шины результата поиска, позволяющие выполнять операции записи информации с входных шин в любые элементы ассоциативной памяти, считывание из них информации, сравнения содержимого этих элементов с информацией на входных шинах и маскирование записи и сравнение определенных столбцов памяти (2) .

Однако поиск (запись) и маскирование информации производится по одним и тем же входным шинам, что вынуждает кодировать одноразрядную информацию двумя двоичными разрядами, причем одна из четырех возможных комбинаций в этих двух разрядах является запрещенной. Кроме того, нет четкого разделения в выборе входных шин при различных режимах работы. В частности, во время режима чтения на шины поиска (записи) должен подаваться уровень логической единицы, а при режиме поиска уровень логической единицы должен подаваться

10 на шины выбора строки. Это вызывает усложнение управлений при работе с АЗУ и ограничивает возможности его применения.

Цель изобретения — упрощение устройства и расширение области его применения за счет обеспечения возможности отделения > маскирующих шин от информационных и исключения запрещенной комбинации на этих входах, четкого разделения в выборе входных шин при различных режимах работы.

Поставленная цель достигается тем, что в ассоциативное запоминающее устройство, содержащее матрицу элементов памяти, первый группы элементов НЕ и блоков выдачи данных — по числу строк матрицы, вторую и третью группы элементов НЕ и вто842962

1О

15 рую группу блоков выдачи данных — по числу столбцов матрицы, причем выходы элементов НЕ первой группы подключены к первым входам элементов памяти одноименных строк матрицы, выходы элементов НЕ второй и третьей групп соединены соответственно со вторыми и третьими входами элементов памяти одноименных столбцов матрицы, входы блоков выдачи данных первой и второй групп подключены соответственно к первым и вторым выходам элементов памяти одноименных строк и столбцов матрицы, введены первый и второй элементы И вЂ” НЕ, группа элементов И вЂ” НЕ и логические блоки, причем выход первого элемента И вЂ” НЕ подключен к одним из входов элементов И вЂ” НЕ группы, выходы которых соединены со входами элементов НЕ первой группы, выход второго элемента И вЂ” НЕ подключен к одним из входов логических блоков, выходы которых соединены со входами элементов НЕ второй и третьей групп, первыв входы первого и второго элемента И вЂ” НЕ объединены и являются одним из управляющих входов устройства, другими управляющими входами которого являются вторые входы первого и второго элементов И вЂ” НЕ и другие входы логических блоков и элементов И вЂ” НЕ группы.

При этом логический блок целесообразно выполнять в виде блока, содержащего элементы И вЂ” НЕ и элемент НЕ, выход и вход которого подключены к первым входам элементов И вЂ” HE, вторые и третьи входы которых объединены соответственно и являются одними из входов логического блока, другим входом которого является вход

-элемента НЕ, а выходы элементов И вЂ” НЕ являются выходами логического блока.

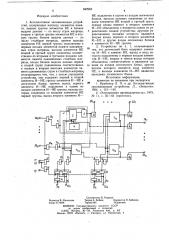

На чертеже изображена структурная схема предлагаемого АЗУ.

Устройство содержит матрицу элементов .1 g — 1ц» памяти, состоящую из и строк и К столбцов. Каждый элемент 1 памяти состоит из запоминающей ячейки 2, блока 3 считывания н схемы 4 сравнения. Устройство также содержит первую группу блоков 5 —

5» выдачи данных, вторую группу блоков

6> — 6»выдачи данных, первую, вторую и третью группы элементов НЕ 7, — 7„, 8,— 8» и 91 — 9„, группу элементов И вЂ” НЕ 10, — 10„ логические блоки 11, — 11,, каждый из которых состоит из элементов И вЂ” НЕ 12 и 13 и элемента НЕ 14.

Устройство содержит первый 15 и второй 16 элементы И вЂ” НЕ, входные шины чтения 17 и записи 18 режимов, шины 19 поиска, шины 20 — 20„,выбора строки, информационные шины 21» — 21», маскирующие шины 22, — 22„„выходные шины 23 — 23, считывания слова и шины 24, — 24,„результатов поиска.

Выход элемента И вЂ” НЕ 15 подключен к одним из входов элементов И вЂ” НЕ 10, — 10,„ го

Зо

40 . 45

55 выход элемента И вЂ” НЕ 16 подключен к одним из входов блоков 11, — 11,, выходы которых соединены с входами элементов НЕ

8> — 8„и 9, — 9», первые входы элементов

И вЂ” НЕ 15 и 16 объединены и являются одним из управляющих входов устройства, другими управляющими входами которого являются вторые входы элементов И вЂ” НЕ

15 и 16 и другие входы блоков 11, — 11» и элементов И вЂ” НЕ 10, — 10„.

Каждый из блоков 11, — 11» содержит элементь1 И вЂ” НЕ 12 и 13 и элемент НЕ 14, выход и вход которого подключен к первым. входам элементов И вЂ” НЕ 12 и 13, вторые и третьи входы объединены соответственно и являются одними из входов блока 11, другим входом которого является вход элемента НЕ 14, а выходы элементов И вЂ” НЕ 12 и 13 являются выходами блока 11.

Устройство работает следующим образом.

В режиме чтения сигнал логического «О» с шины 17, проходя через элемент И вЂ” НЕ 15, разрешает выбор элементов 1 памяти любой строки. Одновременно работа с элементами памяти по информационным 21 — 21» и маскирующим 22> — 22„шинам запрещается с выхода элемента И вЂ” НЕ 16. Считываемая информация из элементов 1 памяти выбранной строки через соответствующие блоки

5i — 5» поступает на выходные шины 23t—

23» считывания слова, В режиме записи обращение к элементам 1 памяти разрешается одновременно по шинам 20, — 20„выбора строки и по информационным 21, — 21» и маскирующим 22, — 22 шинам. В элементы 1 памяти выбранной строки записывается информация, соответствующая уровням на входных информационных шинах 21),—

211. Причем запись информации происходит только в незамаскированных входными маскирующими шинами 221 — 22» элементах 1 памяти строки. В режиме поиска выбор строки запрещается с выхода элемента И вЂ” НЕ

15, а элемент И вЂ” НЕ 16 разрешает работу по информационным 21> — 21»и маскирующим 22, — 22 шинам.

Информация, находящаяся в элементах

1 памяти сравнивается с информацией, поступающей на входные информационные шины 21 -21.

Результат поиска с блоков 6, — 6 поступает на выходные шины 24, — 24„. Причем сравнение с входной информацией происходит только в незамаскированных входными маскирующими шинами 22, — 22» элементах 1 памяти строки.

Предлагаемое устройство по сравнению с известными обладает упрощенным управлением, раздельными шинами маскирования и информации, в нем исключена запрещенная комбинация сигналов на шинах, строго разграничен выбор входных шин при различных режимах работы.

842962

Формула изобретения /7

Составитель В. Рудаков

Редактор В.Матюхина Техред А. Бойкас Корректор Н. Бабинец

Заказ 5119 68 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

1. Ассоциативное запоминающее устройствд, содержащее матрицу элементов памяти, первые группы элементов НЕ и блоков выдачи данных — по числу строк матрицы, вторую и третью группы элементов НЕ и вторую группу блоков выдачи данных — по числу столбцов матрицы, причем выходы элементов НЕ первой группы подключены к первым входам элементов памяти одноименных строк матрицы, выходы элементов НЕ второй И третьей групп соединены соответственно 11о вторыми и третьими входами элементов памяти одноименных столбцов матрицы, входы блоков выдачи данных первой и вторЬй групп подключены соответственно к первым и вторым выходам элементов памяти одноименных строк и столбцов матрицы, отличающееся тем, что, с целью упрощения устройства, оно содержит первый и второй элементы И вЂ” НЕ, группу элементов И вЂ” НЕ и логические блоки, причем выход первого элемента И вЂ” НЕ подключен к одним из входов элементов И вЂ” НЕ группы, выходы которых соединены со входами элементов НЕ первой группы, выход второго элемента И—

НЕ подключен к одним из входов логических блоков, выходы которых соединены со входами элементов HE второй и третьей групп, первые входы первого и второго элемента

И вЂ” НЕ объединены и являются одним из управляющих входов устройства, другими управляющими входами которого являются вторые входы первого и второго э,лементов

И вЂ” НЕ и другие входы логических блоков и элементов И вЂ” НЕ группы.

2. Устройство по п. 1, отличающееся тем, что логический блок содержит элементы И вЂ” НЕ и элемент НЕ, выход и вход которого подключены к первым входам элементов И вЂ” НЕ, вторые и третьи входы которых объединены соответственно и являются одними из входов логического блока, другим входом которого является вход элемента

НЕ, а выходы элементов И вЂ” НЕ являются выходами логического блока.

Источники информации, принятые во внимание при экспертизе

1. Крайзмер Л. П. и др. Ассоциативные запоминающие устройства. Л., «Энергия», 1964, с. 121 — 145.

2. «Электронная промы1л нность», И75> № 11, с; 35 — 42 (прототип).