Устройство для контроля регистрасдвига

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (ii) 842968 (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.10.79 (21) 2828739/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К..

G 11 С 19/00

G 11 С 29/00

Гасударственный кемитет

IIo делам изееретений н еткрмтий

Опубликовано 30,06.81. Бюллетень №24

Дата опубликования описания 05.07.81 (53) УДК 681.327..66 (088.8) (72) Авторы изобретения

В. А. Зернов, В. К. Кузнецов и Д. Н. Федоров (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РЕГИСТРА

СДВИГА

Изобретение относится к вычислительной технике, а более конкретно к устройствам контроля функционирования электрических узлов,и может быть использовано для контроля ЗУ, выполненных на регистре сдвига.

Известно устройство для контроля информации в регистре сдвига, в котором сигнал ошибки выдается в случае отсутствия изменения количества единиц в регистре при наличии неравнозначности на входе и выходе после операции сдвига, а также если есть равнозначность на входе и выходе регистра и есть изменение количества единиц в устройстве (1) .

Ввиду сложной схемной реализации известное устройство имеет большой объем контрольного оборудования.

Наиболее близким к предлагамому по технической сущности является устройство для контроля регистра сдвига, содержащее триггер четности, входной триггер, выходной триггер, свертку по модулю два и сумматор по модулю два, входы которого соединены с выходами перечисленных узлов. В случае несовпадения информации об изменении числа единиц в контролируемом регистре с информацией равнозначности на входе и выходе регистра сдвига на выходе сумматора по модулю 2 появляется сигнал ошибки (2).

К недостаткам. этого устройства следует отнести значительный объем оборудования и большое количество элементов памяти (триггеров), которые подвержены сбоям, что снижает надежность устройства.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройство для контроля регистра сдвига, содержащее блок свертки по модулю два, входы которого соединены с выходами регистра сдвига, первые входы регистра сдвига соединены с шинами управления сдвигом информации, вторые входы регистра сдвига подключены к одним информационным ши1ъ нам, а третий вход — к шине управления записью информации, первый сумматор, триггер четности и другую информационную шину, введены элемент ИЛИ и второй сум, матор, один из входов которого соединен с выходом блока свертки по модулю два, другой вход второго сумматора подключен к выходу триггера четности, первый вход которого соединен с выходом элемента ИЛИ; второй вход триггера четности подсоединен

842968 к шине управления записью информации, один из входов элемента ИЛИ соединен с выходом первого сумматора, а другой вход— с другой информационной шиной, первый вход первого сумматора подключен к одному из выходов регистра сдвига, второй вход первого сумматора соединен с одной из шин управления сдвигом.

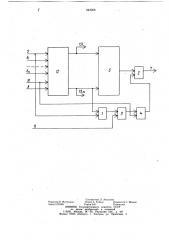

На чертеже представлена функциональная схема предлагаемого устройства, Устройство содержит сумматоры 1 и 2, элемент ИЛИ 3, триггер 4 четности, блок

5 свертки по модулю два, первые информационные шины 6,— 6п (где и — число разрядов двоичного числа), выход 7 сумматора 2 является выходом устройства, шины 8 и 9 управления сдвигом, шину 10 управления записью информации, вторую информационную шину 11, регистр 12 сдвига и выходы 13.1 — 13п,, регистра 12 сдвига.

Устройство функционирует следующим образом.

Сумматор 1 сравнивает информацию на шине 9 и выходе 13 1, регистра сдвига. В случае неравнозначности на выходе сумматора 1 появляется логическая единица, которая через элемент ИЛИ 3 поступает на вход триггера 4 четности, который определяет четность числа единиц в контролируемом регистре 12 сдвига.

Если сдвиг выполнен правильно, то бит четности (БЧ содержимое триггера 4) и бит свертки БСВ (содержимое блока 5 свертки по модулю два) равны

БЧ = БСВ

Если условие (1) не выполняется, то сумматор 2 выдает сигнал ошибки.

В первом такте работы всего устройства по сигналу на шине 10 происходит запись сдвигаемого кода в регистр 12, запись бита четности сдвигаемого кода в триггер 4 четности.

Блок 5 свертки складывает принятый код по модулю два, сумматор 2 сравнивает информацию на триггере 4 четности и на блоке 5 свертки по модулю два.

Если информация принята неправильно, вырабатывается сигнал ошибки, Во втором такте по сигналу на шине 8 происходит сдвиг информации в регистре 12, при этом в триггере 4 четности фиксируется информация о требуемой четности единиц в регистре 12. Блок 5 свертки складывает код. Сумматор 2 производит анализ условия (1).

В каждом следующем такте выполняется сдвиг на один разряд и работа устройства контроля повторяется.

Предлагаемое устройство выполнено с меньшими аппаратурными затратами чем

1О известные, так как вместо трех триггеров и многоразрядных сумматоров использованы один триггер, простой элемент ИЛИ и полусумматоры.

Формула изобретения

Устройство для контроля регистра сдвига, содержащее блок свертки по модулю два, входы которого соединены с выходами регистра сдвига, первые входы регистра сдвига соединены с шинами управления сдвигом информации, вторые входы регистра сдвига подключены к одним информационным шинам, а третий вход — к шине управления записью информации, первый сумматор, триггер четности и другую информационную шину, отличающееея тем, что, с целью упрощения устройства, введены элемент ИЛИ и второй сумматор, один из входов которого соединен с выходом блока свертки по модулю два, другой вход второго сумматора подключен к выходу триггера четности, первый вход которого соединен с выходом элемента

ИЛИ, второй вход триггера четности подсоединен к шине управления записью информации, один из входов элемента ИЛИ соединен с выходом первого сумматора, а другой

35 вход — с другой информационнои шинои, первый вход первого сумматора подключен к одному из выходов регистра сдвига, второй вход первого сумматора соединен с одной из шин управления сдвигом.

4О

Источники информации, принятые во внимание при экспертизе

1. Селлерс Ф. Методы обнаружения ошибок в работе ЭВМ., М., «Мир, 1972.

2. Авторское свидетельство СССР

4> № 529489, кл. G 11 С 29/00, 1976 (прототип) .

842968

Составитель Л. Амусьева

Редактор В.Матюхина . Техред А. Бойкас Корректор С. Шомак

Заказ 5! 20 69 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4