Буферное запоминающее устройствос автономным контролем

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистическик

Реслублик

О П И С А Н И Е 842973

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сид-ву— (22) Заявлено 02.04.79 (21) 2743820/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 11 С 29/00

G 11 С 9/00

Гееудерствеинмй кемитет

СССР (53) УДК 681.327 (088.8) Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 по денем иэебретений и еткрмтий (72) Автор изобретения

С. С. Спиваков (7! ) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЛСТВО

С АВТОНОМНЫМ КОНТРОЛЕМ

Изобретение относитя. к запоминающим устройствам.

Известно буферное запоминающее устройство, содержащее поразрядно соединенные регистры, схемы управления перезаписью, выход и один вход каждой из которых подключены соответственно к входу считыва. ния и выходу маркерного разряда одноименного регистра, а другой вход каждой схемы управления перезаписью, кроме последней, подключен к выходу маркерного разряда следующего регистра (1). о

Однако устройство не обладает достаточной надежностью ввиду отсутствия контроля информации при перезаписи из одного регистра в другой.

Наиболее близким техническим решением к предлагаемому является буферное запоминающее устройство, содержащее поразрядно соединенные регистры, элементы

И, ИЛИ, НЕ и маркерные триггеры (21.

Недостатком этого устройства является возможность возникновения неисправного сбоя в информации при перезаписи ее из регистра в регистр, что снижает надежность устройства.

Цель изобретения — повышение надежности работы. устройства за счет обнаружения и исправления сбоев в информации при записи в регистры устройства.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее триггеры, элементы И, первый элемент HE и последовательно соединенные регистры, входы записи которых подключены к выходам элементов И, кроме последнего, нулевые выходы триггеров подключены к первым входам одноименных элементов И, кроме последнего, а единичные выходы— ко вторым входам элементов И, кроме первого, третьи входы нечетных элементов И соединены с первым управляющим входом устройства, а четных — к выходу первого элемента НЕ, вход которого соединен с первым входом устройства, второй вход первого элемента И и первый вход последнего элемента И являются соответственно вторым и третьим управляющими входами устройства, информационные входы первого регистра и информационные выходы последнего регистра являются соответственно информационными входами и выходами устройства, введены дополнительные элементы И, 842973 второй элемент НЕ и блоки контроля данных, входы которых подключены к выходам одноименных регистров, первые и вторые входы дополнительных элементов И, кроме последнего, подключены соответственно к выходам одноименных блоков, контроля данных и входам Записи одноименных регистров, третьи входы нечетных дополнительных элементов И подключены к четвертому управляющему входу устройства, а четных-к выходу второго элемента НЕ, вход которого соединен с четвертым управляющим входом устройства, выходы дополнительных элементов И, кроме последнего, соединены с единичными входами одноименных триггеров, нулевые входы которых подключены к выходам дополнительных элементов И, кроме первого, первый и второй входы последнего дополнительного элемента И подключены к выходу последнего основного элемента И и являются управляющим выходом устройства.

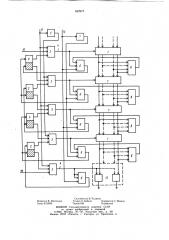

На чертеже изображена структурная схема предлагаемого устройства.

Устройство содержит и последовательно соединенных регистров 1, п триггеров 2, и+1 элементов И 3, имеющих выходы 4, первый элемент НЕ 5, и+1 дополнительных элементов И 6, второй элемент НЕ 7, блоки контроля данных 8.

Устройство имеет первый управляющий вход 9, служащий для подачи тактовых сигналов, второй управляющий вход 10, служащий для подачи сигналов записи, третий управляющий вход 11, служащий для подачи сигналов считывания; четвертый управляющий вход 12, служащий для подачи сигналов опроса.

К выходам устройства подключены выходные элементы И 13.

В качестве блоков 8 могут быть использованы, например, комбинационные сумматоры по модулю два. Входы блоков 8 подключены к выходам одноименных регистров 1. Первые и вторые входы элементов И 6, кроме последнего (нижний на чертеже), подключены соответственно к выходам одноименных блоков 8 и выходам записи одноименных регистров 1, третьи входы нечетных элементов И 6 подключены ко входу 12 устройства, а четных — к выходу элемента НЕ 7, вход которого соединен со входом

12 устройства. Выходы элементов И 6, кроме последнего, соединены с единичными входами одноименных триггеров 2, нулевые входы которых подключены к выходам элементов И 6, кроме первого, первый и второй входы последнего элемента И 6 подключены к выходу последнего элемента И 3 и являются управляющим выходом устройства.

Устройство работает следующим образом.

В исходном состоянии триггеры 2 находятся в нулевом состоянии. На вход 9

4 устройства постоянно поступают тактовые импульсы, частота которых не ниже частоты записи информации

На вход 12 постоянно поступают импульсы опроса, форма и частота которых совпадают с формой и частотой импульсов на входе 9, а фаза отстает. Фазовый сдвиг определяется быстродействием регистров 1 и блоков 8.

Для записи информации в запоминающее устройство на вход 10 поступает запрос на запись. Информация со входов переписывается в первый регистр 1 по переднемфронту тактового импульса при наличии единичного потенциала на нулевом выходе триггера 2 этого регистра и запроса на запись. -Если запись информации в регистр происходит верно, то по переднему фронту сигнала опроса триггер 2 первого регистра

1 устанавливается в единичное состояние.

Единичный потенциал с выхода первого триггера 2 открывает второй элемент И 3 по одному из его входов. По другому входу элемент И 3 открыт единичным потенциалом, поступающим с нулевого плеча второго триггера 2. По заданному фронту тактового импульса на входе 9, на выходе второго элемента И 3 формируется сигнал, осуществляющий перезапись информации из первого регистра 1 во второй регистр 1 и открывающий второй элемент И 6 по одному из его входов.

Сигнал с выхода второго блока 8 поступает на первый вход второго элемента И 6.

Если запись информации во второй регистр

1 происходит со сбоем, то нулевой потенциал на выходе второго блока 8 блокирует второй элемент И 6, первый и второй триггеры 2 остаются в прежнем состоянии, не фиксируя перезапись информации из первого регистра 1 во второй. В следующем периоде тактовой частоты производится повторная перезапись из первого регистра 1 во второй (для исправления сбоя).

Если запись информации во второй регистр 1 происходит без сбоя, то единичный потенциал с выхода второго блока 8 открывает второй элемент И 6. По заднему фронту импульса опроса на входе 12 на выходе второго элемента И 6 формируется сигнал, устанавливающий первый триггер 2 в нулевое состояние, а второй триггер 2 — в единичное.

Дальнейшее продвижение информации из регистра в регистр осуществляется аналогично. Сдвиг по фазе между тактовыми импульсами и импульсами опроса необходим для анализа правильности записи информации в регист)з 1.

Через — — тактовых импульсов, где ив п количество регистров 1, а m — число обнаруженных сбоев информации, первое слово оказывается в последнем регистре 1.

При считывании информации на вход 11 подается сигнал запроса и слово через эле842973 менты И 13 выводится из устройства и последний триггер 2 устанавливается в нулевое состояние, разблокируя предыдущий элемент И 3.

По переднему фронту тактового импульса информация переписывается из четных регистров 1 в нечетные, по заднему фронту происходит перезапись информации из нечетных регистров 1 в четные.

По переднему фронту импульсов опроса производится анализ правильности записи в нечетные регистры 1, а по заднему — в четные.

Предлагаемое устройство позволяет обнаруживать и исправлять сбой в информации при продвижении ее по регистрам, значительно повышая надежность функционирования устройства, что особенно важно при невозможности повторного получения информации.

Формула изобретения

Буферное запоминающее устройство с автономным контролем, содержащее триггеры, элементы И, первый элемент HE u последовательно соединенные регистры, входы записи которых подключены к выходам элементов И, кроме последнего, нулевые выходы триггеров подключены к первым входам одноименных элементов И, кроме последнего, а единичные выходы — ко вторым входам элементов И, кроме первого, третьи входы нечетных элементов И соединены с первым управляющим входом устройства, а четных — к выходу первого элемента НЕ, вход которого соединен с первым входом устройства, второй вход первого элемента И и первый вход последнего элемента И являются соответственно вторым и третьим управляющими входами устройства, информационные входы первого регистра и информационные выходы последнего регистра являются

5 соответственно информационными входами и выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительные элементы И, второй элемент НЕ и блоки контроля данных, входы которых подключены к выходам одноименных регистров, первые и вторые входы дополнительных элементов И, кроме последнего, подключены соответственно к выходам одноименных блоков контроля данных и входам записи одноименных регистров, третьи входы нечетных дополнительных элементов И подключены к четвертому управляющему входу устройства, а четных — к выходу второго элемента НЕ, вход которого соединен с четвертым управляющим входом устройства, выходы дополнительных элементов И, кроме последнего, соединены с единичными входами одноименных триггеров, нулевые входы которых подключены к выходам дополнительных элементов И, кроме первого, первый и второй входы последнего дополнительного элемента И подключены к выходу последнего основного элемента И и являются управляющим выходом устройства.

Источники информации

ЗО принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 407396, кл. G 11 С 19/00, 1972.

2. Авторское свидетельство СССР № 551705, кл. G 11 С 27/00, 1975 (прототип).

842973

Редактор В. Матюхина

Заказ 5120/69

Составитель В. Рудаков

Техред А. Бойкас Корректор С. Щомак

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4