Устройство для исправления ошибокв блоке памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 842976 (61) Дополнительное к авт. свид-ву— (22) Заявлено 10.07.79 (21) 2795497/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 11 С 29/00

Государственный комитат (53) УДК 681.327 (088.8) Опубликовано 30.06.81. Бюллетень № 24 по девам изобретений и открытий

Дата опубликования описания 05.07.81 (72) Авторы изобретения

Т. Н. Андреева, А. В. Городний, В. И. Корнейчук, Н. М. Лазинцев, M. Н. Орлова, В. П. Палкин, И. Ф. Рудниченко и Ю..Б.,Рычагов

Киевский ордена Ленина политехнический институт имейи 50-летия

Великой Октябрьской социалистической революции (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

В БЛОКЕ ПАМЯТИ

Изобретение относится к запоминающим устройствам и предназначено для исправления однократных, двухкратных и трехкратных ошибок, возникающих при отказах разрядов накопителя.

Извстно устройство, которое содержит регистр прямого кода, блок сумматоров по модулю два, дешифратор номера отказавшего разряда, контрольный регист р и накопитель (1) .

Недостатком этого устройства является низкая надежность.

Наиболее близким к предлагаемому является устройство, содержащее информационный регистр, выходы которого подключены ко входам многовходовых сумматоров по модулю два, а выходы последнего подсоединены к контрольному регистру, дешифратор и блок управления (2).

Недостатком этого устройства является невысокая точность контроля и снижение надежности вследствие значительного увеличения избыточной емкости памяти и аппаратурных затрат.

Цель изобретения — повышение точности контроля и надежности устройства.

Поставленная цель достигается тем, что в устройство для исправления ошибок в блоке памяти, содержащее сумматоры по модулю два, регистр прямого кода, дешифратор, блок управления и выходной регистр, причем одни из входов сумматоров по модулю два подключены к первому выходу регистра прямого кода, а первый и второй выходы — соответственно к одному из вхо дов блока управления и ко входам дешифратора, выходы которого соединены с первым входом выходного регистра, выход которого является первым информационным выходом устройства, а второй вход подключен к соответствующему выходу блока управления, другие входы и выходы которого являются управляющими входами и выходами устройства, первый вход регистра прямого кода является первым информационным входом устройства, второй вход подключен к соответствующему выходу блока управления. а третий вход и второй выход регистра прямого кода. являются вторыми информационными входом и выходом устройства, введены регистр обратного кода, схема сравнения, два элемента И, формирователь.сигна842976 лов кратности отказа и элемент ИЛИ, причем первый вход схемы сравнения подключен к первому выходу регистра прямого кода и первому входу первого элемента И, а второй вход схемы сравнения — к другим входам сумматоров по модулю два, первому входу второго элемента И и инверсному выходу регистра обратного кода, входы которого соединены со вторым информационным входом устройства, выход схемы сравнения подключен к первому входу формирователя сигналов кратности отказа, второй вход которого соединен с третьим выходом сумматоров по модулю два, а первый и второй выходы подключены соответственно ко вторым входам первого и второго элементов

И, а третий выход является контрольным выходом устройства, выходы элементов И соединены соответственно со входами элемента ИЛИ, выход которого подключен к третьему входу выходного регистра.

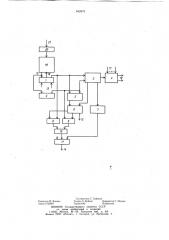

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит регистр 1 прямого кода, регистр 2 обратного кода, сумматоры

3 по модулю-.два, блок 4 управления, схему 5 сравнения, формирователь 6 сигналов кратности отказа, дешифратор 7, первый 8 и второй 9 элементы И, элемент ИЛИ 10, выходной регистр 11, котрольный выход 12, первые информационные вход 13 и выход

14, вторые информационные вход 15 и выход 16, управляющие вход 17 и выход 18.

Один из входов сумматоров 3 по модулю два подключены к первому выходу регистра 1 прямого кода, а первый и второй выходы — соответственно к одному из входов блока 4 управления и ко входам дешифратора 7. Выходы дешифратора 7 соединены с первым входом выходного регистра 11, выход которого является первым информационным выходом 14 устройства, а второй вход подключен к соответствующему выходу блока 4 управления, другие входы и выходы которого являются управляющими входами 17 и выходами 18 устройства. Первый вход регистра 1 прямого кода является первым информационным входом 13 устройства, второй вход подключен к соответствующему выходу блока 4 управления, а третий .вход и второй выход регистра 1 прямого кода являются вторыми информационными входом 15 и выходом 16 устройства. Первый вход схемы 5 сравнения подключен к первому выходу регистра 1 прямого кода и первому входу первого элемента И 8. Второй вход схемы 5 сравнения подключен к другим входам сумматоров 3 по модулю два, первому входу второго элемента И 9 и инверсному выходу регистра 2 обратного кода, входы которого соединены со вторым информационным входом 15 устройства. Выход схемы 5 сравнения подключен к первому входу формирователя 6 сиг5 !

25 зю

45 ,50

4 налов кратности отказа, второй вход которого соединен с третьим выходом сумматоров 3 по модулю два, псрвый и второй выходы подключены соответственно ко вторым входам первого 8 и второго 9 элементов И, а третий выход является контрольным выходом 12 устройства. Выходы первого 8 и второго 9 элементов И соединены соответственно со входами элемента ИЛИ 10 выход которого подключен к третьему входу выходного регистра 11. Вторые информационные вход 15 и выход 16 устройства подключаются к информационным выходу и входу контролируемого блока .19 памяти, адресные входы которого подключены к выходам регистра 20 адреса, имеющему входы 21.

Устройство работает следующим образом.

При записи на первый информационный вход 13 регистра 1 прямого кода поступает закодированное кодом Хэмминга слово, которое записывается в блок 19 памяти по адресу, хранящемуся в его регистре 20 адреса.

В цикле чтения считанное информационное слово поступает в регистр 1 прямого кода, а с его выхода — на сумматоры 3 по модулю два, которые формируют контрольнЫе разряды в соответствии с алгоритмом образования кода Хэмминга., В случае отсутствия ошибок во всех контрольных разрядах информационное слово с первого выхода регистра 1 прямого кода через первый элемент И 8, элемент ИЛИ 10 и выходной регистр 11 поступает на первый информационный выход 14 устройства.

Если же искажающие информацию отказы имеют место, то по сигналам блока 4 управления осуществляется коррекция считанной информации. Для этого с регистра

1 прямого кода снимается инверсное значение информационного слова, которое заносится в ту же ячейку проверяемого блока 19 памяти. Затем выполняется цикл чтения с занесением считанной информации в регистр 2 обратного кода.

Содержимое регистра 1 прямого кода и

2 обратного кода сравнивается с помощью схемы 5 сравнения, на выходе которой сигнал «1» появится в тех разрядах, в которых не совпадают прямой и обратный коды. Эти разряды запоминающей ячейки блока 19 памяти отказали и представляют собой генераторы констант («генератор О» или «генератор 1»). Информация о схемы 5 сравнения поступает в формирователь 6 сигналов кратности отказа, который определяет кратность отказа. Если кратность отказа больше трех, то формирователь 6 сигналов кратности отказа выдает на контрольный выход 12 сигнал о неисправимой ошибке.

Если кратность отказа меньше или равна трем, то с инверсного выхода регистра 2 обратного кода информация поступает на

842976

Формула изобрег ения

50 сумматоры 3 по модулю два. В случае отсутствия ошибок по всем контрольным разрядам, сформирбванным сумматорами 3 по модулю два,(а это возможно, если три отказа вызывают три ошибки в прямом коде и после указанных выше действий в обрат- 5 ном коде нет ошибок), информационное слово с инверсного выхода регистра 2 обратного кода через второй элемент И 9, элементы ИЛИ-10, и 13 (при наличии разрешающего сигнала с формирователя сигналов кратности отказа 6) и выходной ре- 10 гистр 11 поступает на первый информационный выход 14. Если в информации, считанной из проверяемого блока 19 памяти, присутствует двухкратная ошибка, то в информационном слове, хранящемся при этом в регистре 2 обратного кода, присутствует нечетная (одиночная) ошибка, которая обнаруживается сумматорами 3 по модулю два, и формирователь 6 сигналов кратности отказа вырабатывает разрешающий сигнал на выдачу . информационного .слова с ин- 20 версного выхода регистра 2 обратного кода через второй элемент И 9 и элемент ИЛИ

10 на выходной регистр 11. Одновременно с этим код ошибочного разряда поступает на дешифратор 7, который дешифрирует номер отказавшего разряда и выдает сигнал на

25 инвертирование отказавшего разряда в выходном регистре 11. После этого исправленное информационное слово поступает на первый информационный выход 14.

Если обнаружена четная (т. е. двойная) 30 ошибка в информационном слове, хранящемся в регистре 2 обратного кода, то в регистре 1 прямого кода содержится информация с одним ошибочным разрядом. Формирователь сигналов кратности отказа вырабатывает разрешающий сигнал на выдачу информационного слова с регистра 1 прям< го кода через первый элемент И 8 и элем .нт ИЛИ 10 на выходной регистр 11. Одновременно с этим на дешифратор 7 поступает код ошибочного разряда для слова, хранящегося в регистре 1 прямого кода. Де40 шифратор 7 выдает сигнал на инвертирование отказавшего разряда в выходном регистре 11, после чего информационное слово поступает на первый информационный выход 14 устройства.

Технико-экономическое преимущество предложенйого устройства заключается в том, что в нем без увеличения аппаратурных затрат .обеспечивается обнаружение и исправление всех трехкратных ошибок, возникающих в результате отказа некоторых разрядов ячеек накопителя, за счет чего повышается точность контроля и надежность устройства.

Устройство для исправления ошибок в блоке памяти, содержащее сумматоры по модулю два, регистр прямого кода, дешифратор, блок управления и выходной регистр, причем одни из входов сумматоров по модулю два подключены к первому выходу регистра прямого кода, а первый и второй выходы — соответственно к одному из входов блока управления и ко входам дешифратора, выходы которого соединены с первым входом выходного регистра, выход которого является первым информационным выходом устройства, а второй вход подключен к соответствующему выходу блока управления, другие входы и выходы которого являются управляющими входами и выходами устройства, первый вход регистра прямого кода является первым информационным входом устройства, второй вход подключен к сосответствующему выходу блока управления, а третий вход и второй выход регистра прямого кода являются вторыми информационными входом и выходом устройства, отличающееся тем, что, с целью повышения точности контроля и надежности устройства, оно содержит регистр обратного кода, схему сравнения, два элемента И, формирователь сигналов кратности отказа и элемент ИЛИ, причем первый вход схемы сравнения подключен к первому выходу регистра прямого кода и первому входу пер-. вого элемента И, а второй вход схемы сравнения — к другим входам сумматоров по модулю два, первому входу второго элемента И и инверсному выходу регистра обратного кода, входы которого соединены со вторым информационным входом устройства, выход схемы сравнения подключен к первому входу формирователя сигналов кратности отказа, второй вход которого соединен с третьим выходом сумматоров по модулю два, первый и второй выходы подключены соответственно ко вторым входам первого и второго элементов И, а третий выход является контрольным выходом устройства. выходы элементов И соединены соответственно со входами элемента ИЛИ, выход которого подключен к третьему входу выходного регистра., Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР №402870, кл. G 06 F 11/08, 1974.

2. Хетагуров Я. А., Руднев 1О. П. Повышение надежности цифровых устройств методами избыточного кодирования. М.,!974, с. 51 — 54 (прототип).

842976

Составитель Т. Зайцева

Редактор М. Янович Техред А. Бойкас Корректор С. Щомак

Заказ 5120/69 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4