Групповой стандарт частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

«»843155 (61) Дополнительное к авт. саид-ву(51) РА. Сл .> (22) Заявлено 270879 (21) 2818456/18-09 с присоединением заявки ¹

Н 03 В 3/08

Государственный комитет

СССР но делам изобретений и открытий (2З) Приоритет—

Опубликовано 3006.81. Бюллетень М

Рз) УД 621, 376 (088. 8) Дата опубликования описания 300681 (72) Авторы изобретения

Г.Д. Новиков, В.3. Ганкин, A. Г. Козодаен, A. Г. Геворкян, И.М. Болотов и A.Ë.Кясников (71) Заявитель (S 4 ) ГРУППОВОЙ СТАНДАРТ ЧАСТОТЫ

Изобретение относится к радйотех. нике и может использоваться в устройствах,формирующих выходной сигнал высокостабильной частоты.

Известен групповой стандарт частоты, содержащий три канала, каждый из которых состоит из последовательно соединенных стандарта частоты, фозовращателя и фазового детектора, причем второй вход фазового детектора

-первого канала соединен с выходом фазовращателя второго канала, второй вход фазового детектора второго канала соединен с выходом фазовращателя третьего канала, а второй вход фазового детектора третьего канала соединен с выходом фазовращателя первого канала (1)..

Однако известный стандарт частоты имеет плохую долговременную стабильность выходного сигнала.

Цель изобретения — улучшение долговременной стабильности выходного сигнала.

Поставленная цель достигается тем, что в групповой стандарт частоты, содержащий три канала,,каждый из кото. рых состоит из последовательно соединенных стандарта частоты, фазовращателя и фазового детектора, причем второй вход фазового детектора пер— вого канала соединен с выходом фазовращателя второго канала, второй вход фазового детектора второго канала соединен с. выходом фазовращателя третьего канала, а второй вход фазового детектора третьего канала соединен с выходом фазовращателя первого ка-нала, введены последовательно соединенные вычислитель среднего значения частоты, блок формирования сигналов управления и решающий блок, а также блок анализа фазовых ошибок, при этом сигнальные выходы стандарта частоты

15 каждого из каналов соединены с соответствующими входами вычислителя сред. него значения частоты и блока формирования сигналов управления, выходы которого подключены к управляющему

20 входу стандарта частоты соответствующего канала, информационные выходы которых соединены со вторыми входами решающего блока, третьи входы которого подключены к соответствующим вы25 ходам блока анализа фазовйх сшибок, входы которого соединены с выходами фазовых детекторов каждого из каналов, при этом в каждом из каналов введены ключ и последовательно соединенные

30 инвертор, коммутатор и интегратор, 843155 выход которого соединен с управляющим входом фазовращателя этого же канала, другой вход коммутатора подключен к выходу фазового детектора этого же канала, вход инвертора второго канала соединен с выходом фазового детекто-. ра первого. канала,.вход инвертора третьего канала соединен с выходом фазового детектора второго канала, а вход инвертора первого, канала соединен с выходом фазового детектора третьего канала, управляющие входы коммутаторов каждого из каналов соединены с первыми выходами решающего блока, вторые выходы которого соединены с управляющими входами интегратора и клю. ча соответствующего канала, причем сигнальный вход ключа каждого из каналов подключен к выходу фазовращате ля этого же канала, а выходы ключей объединены и являются выходом устрой 2О ства.

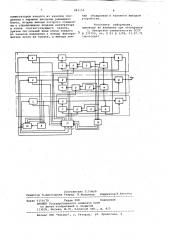

На чертеже представлена структурная электрическая схема предлагаемого стандарта частоты.

Групповой стандарт частоты содержит три канала 1, каждый из которых состоит из стандарта 2 частоты, фазовращателя 3, фазового детектора 4, инвертора 5, коммутатора 6, интегратора 7 и электронного ключа 8, вычислитель 9 среднего значения частоты, блок 10 формирования сигналов управления, решающий блок 11, блок 12 . анализа фазовых ошибок.

Устройство работает следующим образомм.

Выходные сигналы стандартов 2 частоты каждого канала 1 с частотами и f > через фазовращатели 3 поступают на входы электронных ключей

8. Одновременно они поступают на 40 вход вычислителя 9, который производит периодическое измерение разностей частот стандартов 2 частоты, Причем измерения производятся по кольцу, например ь Г д = f - f.ä, Ь fz>=» д Г = f3 - f< и вычисляет среднее значение частоты. Вычисление отклонения частоты каждого стандарта

2f от среднего значения Г „ и выработ1 к а управляюще го воз дей ст вия, пропорционального (f+ - f„), произ водится блоком 10 формирования сигналов управления. В результате воздействия сигналов управления на выходах стан1 артов 2 частоты и, соответственно, а входах электронных ключей 8 будут действовать сигналы стандартов ? частоты, подстроенные к

Время обработки сигнала вычислителем 9 и период между подстройками выбирается исходя из качества стан- Я дартов частоты, определяемого паспортными значениями их погрешности и вариаций действительного занчения частоты (ДЗЧ), Точное фазирование выходных сигналов с ошибкой менее 1 осу- Я ществляется с помощью фазовращателей .t

3, охваченных системой фазовоп авто- подстройки. В состав цепи автоподстройки входит фазовый детектор 4, коммутатор 6, интегратор 7.

Как видно из чертежа, кбммутируя входные сигналы коммутатора 6, схема позволяет либо разомкнуть цепь автоподстройки, либо осуществить подстройку фазовращателя 3 сигналами управлеия с выхода фазового детектора 4 данго или предыдушего канала, Включение инвертора 5 в цепь автоподстройки позволяет исключить переI стройку фазы выходного сигнала фазовращателя при переключении выхода фазового детектора 4 данного канала для управления фазовращателем соседнего канала.

Каждый из каналов может работать в режиме автоподстройки или режиме хранения (памяти) фазы. Канал, находящийся в режиме памяти, является ведущим. Обеспечение режима памяти осуществляется по команде, поступающей с решающего блока 11 на коммутатор 6 данного канала. При этом в веду. щем канале коммутатор разрывает цепь автоподстройки фазовращателя 3 и замыкает их в других каналах. Причем замкнуты цепи автоподстроек по тем входам коммутаторов 6, при замыкании которых обеспечивается последовательная подстройка сигналов по фазе выходного сигнала фазовращателя ведущего канала. Одновременно с подачей сигнала управления на коммутатор 6 с решающего блока 11 выдается команда управления на интегратор 7 и электронный ключ 8 каждого канала.

По этой команде интегратор 7 ведущего канала хранит напряжение, имевшее место на момент перехода канала в режим памяти, а интеграторы 7 других каналов работают в режиме синхронизации сигналов по фазе ведущего канала.

По этой же команде замыкается электронный ключ 8 ведущего канала и размыкаются цепи электронных ключей

8 других каналов, в результате чего на выход устройства транслируется сигнал с выхода стандарта частоты ведущего канала. Нормальная работа цепей автоподстроек фазовращателей в каналах контролируется при помощи блока 12 анализа, фазовых ошибок, При исправной работе цепей автоподстроек фазовращат елей 3 с выходов фаз овых детекторов

4 на вход блока 12 анализа фазовых саыбок подаются напряжения 0@ц= О, соответствующие нулевой ошибке. В слу-. чае неисправности цепи автоподстройки одного из каналов на выходе фазовых детекторов соответствующих каналов появится напряжение, отличающее-. ся от нулевого на величину, большую

+Uö „, Блок 12 анализа фазовых ошибок формирует команду о неисправности це843159.пи АПФ аварийного канала и транслирует ее на соответствующий вход решаю щего блока 11 °

На другие входы решающего блока 11 с информационных выходов стандартов

2 частоты поступают сигналы, сформиро- ванные на основе внутреннего анализа и соответствующие их исправной или неисправной работе.

На следующие входы решающего блока 11 поступает информация о величине о отклонения i-го значения частоты стандарта 2 от средней величины, а такх<е исправности вычислителя 9 и блока 10 формирования сигналов управления.

На основании поступающей информа- 15 ции решающий блок формирует команды управления, по которым осуществляется один из вариантов схем соединения . каналов.

В качестве примера рассмотрим 20 случай, когда в исходном состоянии сигналы всех трех каналов исправны. и ведущим выбран первый канал. Структура решающего блока 11 позволяет оператору любой из исправных каналов 5 выбрать в качестве ведущего. В этом случае с выходов решающего блока 11 на управляющие входы коммутатора б, интеграторов 7 и электронных ключей 8 поступают команды, в резуль- З тате воздействия которых осуществляется соответствующее соединение каналов. В ведущем (первом) канале замыкается электронный ключ 8, размыкается цепь автоподстройки фазовращателя 3, а интегратор 7 переходит в режим памяти напряжения. В случае аварии сигнала по третьему каналу смены ведущего канала и перекоммутации каналов не произойдет, так как по фазе сигнала с третьего канала ни 40 один из сигналов не подстраивается.

В случае аварии сигнала по второму каналу произойдет перекоммутация каналов.

Смены ведущего канала не произойдет, а аварийный канал становится в конце последовательной цепи автоподстройки фазы.

В случае аварии сигналов по второму -и третьему каналам производится

cooTâåòñòâóþøåå соединение каналов.

Такая логика, заключака аяся в том, что аварийный канал всегда включается в конце последовательной цепи автоподстройки фазы, позволяет производить ремонт канала, не ухудшая пара55 метров выходного сигнала.

В случае аварии сигнала по ведущему каналу произойдет смена ведущего канала, а аварийный (в данном случаепервый канал) подключается в конце ц последЬвательной цепи автоподстройки.

Ведущим становится второй канал, ийтегратор данного канала переходит в режим памяти напряжения, т.е. Фик сируется Фаза сигнала на момент при- у хода команды на переключение. Учитывая. то, что фазы сигналов сведены, то при смене ведущего канала скачка

Фазы выходного сигнала не произойдет.

Аналогично работает логика решающего блока 11 при различных ситуациях с новым ведущим каналом, Таким образом, при достаточно простой схеме группового стандарта частоты достигается воэможность улучшения долговременной стабильности, сохранения спектральных характеристик стан- дартов частоты на выходе .устройства и отсутствие скачков Фазы сигнала при переключении ведущего канала..

Формула изобретения

Групповой стандарт частоты, содержащий три канала, ках<дый из которых состоит иэ последовательно соединенных стандарта .частоты, Фазовращателя и Фазового детектора, причем второй вход фазового детектора первого канала соединен с выходом фазовращателя второго канала, второй вход фазового детектора второго канала соединен с выходом фазовращателя третего канала,, а второй вход фазового детектора третьего канала соединен с выходом фазовращателя первого канала, отличающийся тем, что, с целью улучшения долговременной стабильности выходного сигнала, в него введены последовательно соединенные вычислитель среднего значения частоты, блок формирования сигналов управления и решающий блок, а так>ке блок анализа Фазовых ошибок, при этом сигнальные выходы стандарта частоты каждого из каналов соединены с соответствующими входами вычислителя среднего значения частоты и блока

Формирования сигналов управления, выходы которого подключены к управляющему входу стандарта частоты соответст— вующего канала, информационные выходы которых соединены со вторыми входами решающего блока, третьи входы которого подключены к соответствующим .выходам блока анализа фазовых сшибок, входы которого соединены с выходами

Фазовых детекторов каждого иэ каналов, при этом в каждом из каналов вве,дены ключ и последовательно соединен" ные инвертор, коммутатор и интегратор, выход которого соединен с уп« равляющим входом Фазовращателя этого же канала, другой вход коммутатора подключен к выходу фазового детектора этого же канала, вход инвертора. второго канала соединен с выходом фазового детектора первого канала, вход инвертора третьего канала соединен с выходом фазового детектора. второго канала, а вход инвертора первого канала соединен с выходом фазового детекторатретьего канала, управляющие входы

843155

Составитель F.. Голуб

Редактор И.Лысогорова Техред Н.Ковалева Корректор Н ° 8« « - Í

Эаказ 5159/78 Тираж 988 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 т

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 коммутаторов каждого из .каналов соединены с первыми выходами решающего блока, вторые выходы которого соединены с управляющими входами интегратора и ключа соответствующего канала, причем сиг. альный вход ключа каждого из каналов подключен к выходу фазовращателя этого же канала, а выходы ключей объединены и являются выходом устройства.

Источники информации, принятие во внимание при экспертизе

1. Авторское свидетельство СССР

Р 375750, кл. Н 03 В 3/08, 21. 07. 71 (прототип )