Импульсный частотно-фазовый дискри-минатор

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнапнстнческнх

Республнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву Р 569000 (22) Заявлено 080879 (21) 2816391Р.8-21 Ф)М с присоединением заявки hl9 (23) Приоритет

Н 03 0 13/00

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 3pp681,Бюллетень М9 24

Дата опубликования описания 3006.81 (53) УДИ 621. 317. .772:621.316. .727(088.8) ;с ., н >

1, »47 .:...

f 5 т . " : il4p ".,, 6! r, ;,„, " Р„; (72) Автор изобретения

В.И.Стребков (71) Заявитель (54 ) ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

По основному авт. св. Р 569000 известен импульсный частотно-фазовый дискриминатор содержит два входных логических элемента И, один из входов каждого из которых подключен к источнику входных сигналов, а вы.—

: ход — ко входу логического элемента

ИЛИ, выходной триггер со счетным.входом, который соединен с выходом второго логического элемента ИЛИ, входы которого соединены с выходами двух дополнительных логических элементов

И, первые входы которых подключены к !5 выходам соответствующих входных логических элементов И, а вторые входык выходам входного триггера; вход которого соединен с выходом первого из упомянутых логических элементов 20

ИЛИ, и два дополнительных логических элемента ИЛИ, входы которых подключены к выходам указанных триггеров, а выходы соединены с другими входами входных логических элементов И

Этот дискриминатор имеет логический выход с выходного триггера и может работать в двух режимах — частотного и фазового сравнения сигналов. В режиме частотного сравнения сигна- ЗО лов характеристика дискриминатора релейная. В режиме фаз.ового сравнения сигналов выходной сигнал дискрими натора импульсный, при этом относительная длительность импульсов пропорциональна раз ности фаэ сравниваемых сигналов на интервале 0-360

Переключение из одного режима в другой происходит автоматически (1 ).

В ряде случаев применения дискриминатора необходима информация о режиме работы. Однако, дискриминатор не дает сигнала,. несущего указанную информацию, что ограничивает его функциональные возможности.

Цель изобретения - расширение функциональных возможностей дискриминатора за счет получения информации о ре>киме работы дискриминатора.

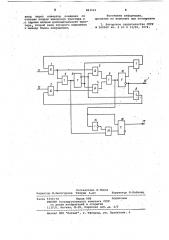

Указанная цель достИгается тем, что в импульсный частотно-фазовый дискриминатор, содержащий два выходных логических элемента И, один из.входов каждого из которых подключен к источнику входных сигналов, а выходк входу логического элемента ИЛИ, выходной триггер со счетным входом, который соединен с выходом второго логического элемента ИЛИ, входы которого соединены с выходами двух допол843163 нительных логических элементов И, первые входы которых подключены к выходам соответствующих входных логических элементов И, а вторые входы к выходам второго триггера,,вход которого соединен с выходом первого из упомянутых логических элементов ИЛИ даа дополнительных логических элемента ИЛИ, входы которых подключены к выходам указанных триггеров, а выходы соединены с другими входами входных логических элементов И, введены допол-1 нительный триггер, инвертор и блок совпадения, первый вход которого подключен к счетному входу второго триггера, второй вход через инвертор соединен со счетным входом выходного Я триггера и с первым входем дополнительного триггера, второй вход которого подключен к выходу блока совпадения, На чертеже представлена функциональная. схема импульсного частотнофаз ов о го ди скр ими н ат ор а.

Дискриминатор содержит логические элементы И 1-4, логические элементы, ИЛИ 5-8, триггеры 9 и 10 со счетными входами, входы 11 и 12 дискриминируемых сигналов F и F>, выход 13, инвертор 14,. блок 15 совпадения, триггер 16 с разделительными входами и дополнительный выход 17.

Принцип работы, дискриминатора заключается в следующем.

На входы 11 и 1? элементов И 1 и

2 поступают сигналы с частотами соответственно F и Fz. По вторым входам элементы И 1 и 2 управляются че- . рез элементы ИЛИ 7 и 8 сигналами с 35 выходов триггеров 9 и 10. Входные импульсы поступают на счетные входы триггеров 9 и 10. Сигнал на выходе

13 несет информацию по результатам дискриминирования сигналов. 40

Дискриминатор может иметь четыре состояния, характеризуемые соответствующими комбинациями состояний триггеров

9 и 10.

При условииГ < Fq триггер 10 не из-. меняет своего состояния и на выходе 13 имеется сигнал "1". Дискриминатор работает в режиме частотного сравнения сигналов.

При увеличении Fz после момента . времени, соответствующего равенству

F< "- Е, импульсы частоты F начинают опережать по фазе импульсы частотЫ

F и между какими-то двумя соседними импульсами частоты Fz проходят два импульса частоты F< . С приходом вторб"5 ! го из этих импульсов дискриминатор переходит в другое состояние. Далее импульсы частоты F< и F чередуются, при этом триггер 10 йереключается и.сигнал на выходе 13 соответствен-щ) но принимает значения "1" и "0". Огносительная длительность импульсов на выходе 13 линейно, зависит от разности фаз сигналов F и F> на интервале

0-360, т.е. в этом случае дискримиВ Ф натор работает в режиме фазового сравнения сигналов.

При Fz > F< на выходе 13 имеется: сигнал "0". Дискриминатор работает в режиме частотного сравнения сигналов.

B режиме частотного сравнения сигналов импульсы с выхода элемента ИЛИ

5 поступают на вход триггера 9, а . также через блок 15 совпадения - на первый раздельный вход триггера 16 и переключают его в состояние "0", которое определяет сигнал на допол.нительном выходе 17.

В режиме фазового сравнения сигналов появляются импульсы на выходе элемента ИЛИ 6, которые кроме входа

P триггера 10 поступают также на вход инвертора 14. Инвертированные импульсы поступают на,один из входов блока

15 совпадения и, совпадая во времени с импульсами, поступающими на другой вход, закрывают прохождение их через блок 15. Таким образом, в этом случае импульсы на выходе блока 15 отсутствуют и не поступают на первый раздельный вход триггера 16. На второй раздельный вход триггера 16 поступают импульсы со входа инвертора 14 и переключают триггер 16 в состояние

"1", которое определяет сигнал на дополнительном выходе 17.

Таким образом, сигнал на дополнительном выходе 17 в режиме фазового сравнения соответствует "1", а в режиме частотного сравнения - "0", т.е. несет информацию о режиме работы дискриминатора.

В зависимости от конкретной реализации триггера 16 для его переключения необходимо подавать сигналы "1" или "0" ° Соответственно второй раздельный вход триггера 16 должен быть подключен ко входу или выходу инвертора 14.

Введение дополнительного триггера с раздельными входами, ивертора, блока совпадения при Предлагаемом их соединении между собой и с другими элементами схемы обеспечивает получение дополнительного выходного сигнала, несущего информацию о режиме работы дискриминатора, что расширяет функциональные возможности дискриминатора и, соответственно, область его применения.

Формула изобретения

Импульсный частотно-фазовый дискриминатор по авт.св. Р 569000, о т— л и ч а ю шийся тем,что,с целью расширения функциональных возможностей устройства за счет получения информации о режиме работы дискриминатора, в него введены дополнительный триггер, инвертор и блок совпадения, первый вход которого подключен к. счетному входу второго триггера, второй

84 3163

Составитель В.Чижов

Редактор М.Лысогорова Техред A.À÷

Корректур Н. Бабинец

Заказ 5159/78 Тираж 988

ВНИИПИ Государственного ксмитета СССР по делам изобретений и открытий

1130 35, Москва, Ж-35, Раушская наб.,д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 вход через инвертор соединен со счетным входом выходного триггера и

;с первым входом дополнительного триг- гера .второй вход которого подключен к выходу блока совпадения.

Источники информации, принятые во внимание при экспертизе а

1. Авторское свидетельство СССР

9 569000 кл. Н 03 D 13/00, 1974 .