Синхронный д-триггер

Иллюстрации

Показать всеРеферат

« ;,„„„..1 .

Московский ордена Трудового Красного Знамени инженернофизический институт (7I) Заявитель (54) СИНХРОННЫЙ О-ТРИГГЕР

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в быстродействующих цифровых микросхемах.

В цифровой технике широко используются Ьинхронные2 -триггеры, поS строенные на логических элементах

И-НЕ, ИЛИ-НЕ. Эти триггеры содержат две бистабильные ячейки. Под действием синхросагнлта информация из пер-,, вой бистабильной ячейки передается во вторую, выходы которой служат выходами триггеров f11.

Недостатком этих триггеров является большая потребляемая мощность, значительная площадь, занимаемая. на ,кристалле при изготовлении в интеграль- ных микросхемах, а также низкое быстродействие.

Наиболее близким техническим реше- 20 кием к предлагаемому является схема синхронного О-триггера, состоящая .из, двух бистабильных ячеек (БЯ),выход ной и управля10щей, каждая из которых содержит два перекрестно соединенных инвертора. Входы выходной БЯ соединены с выходами инверторов, входы управляющей БЯ соединены с выходами инверторов. Выходы ннверторов подключены к выходам Я и Q триггера. Вход 9 соединен с первым выходом инвертора, реализуя логическую операцию "Проводное И", и подключен ко входу инвертора. Второй выход инвертора соединен со вторым выходом инвертара, реализуя логическую операцию "Проводное И", и подключей ко входу инвертора. Один из выходов инвертора соединен с первым выходом инвертора синхросигналов, реализуя, операцию

"Проводное И" и подключен ко входу инвертора. Один иэ выходов инвертора соединен со вторым выходом инвертора, реализуя операцищ "Проводное И", и подключен ко входу инвертора, Вход инвертора соединен со входом синхронизации С-триггера, а его третий выход подключен ко входу ннвертора. Макси843176 мальная рабочая частота триггера—

l/7t, где t - задержка инверюакс тора 523.

Недостатком данного триггера является малое быстродействие, Цель изобретения — повышение быстродействия триггера, Указанная цель достигается тем, что в синхронный Э -триггер на инверторах, содержащий ведущий и ведомый щ триггеры с двумя входами и двумя выходами, в каждом триггере первые выходы первого и второго инверторов подключены соответственно к первому и второму выходам, а вторые выходы †15 ро входам этих инверторов перекрест.ными связями, вход пятого инвертора соединен с .входом С, первый и второй выходы — с первым и вторым входами ведущего триггера, с .входами третьего gp и четвертого инвертора этого триггера и с третьим выходом четвертого инвертора и ДвходомЗ -триггера, соответственно, а третий выход — с входом шестого инвертора,первый и второй выходы 25 которого подключены к первому и второ— му входам ведомого триггера, к входам третьего и четвертого инверторов этого триггера,в каждом триггере первый и второй выходы третьего и четвертого 5в инверторов соединены попарно с первым . и вторым выходами первого и второго инверторов соответственно.

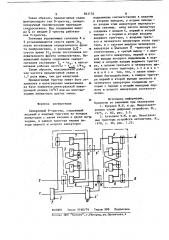

Схема синхронного)3 -триггера при35 ведена на чертеже.

Триггер содержит многбвыходные инверторы с 1-10. Выходы Я и Я триггера подключены соответственно к первым выходам инверторов 1, 5, 2 и 6, соединенных для реализации операции

"Проводное И". Вторые выходы инверторов 1 и 5, 2 и 6 соединены между собой, реализуя операции "Проводное И" и подключены с@ответственно ко входам

45 инверторов 2 и 1. Первые выходы инверторов 3, 7, IO соединены между

Собой, реализуя операцию "Проводное И" и подключены ко входу инвертора 5. Первые выходы инверторов 4, 8 и второй выход инвертора IO аналогич50 ным образом подключены ко входу инвертора 6. Вторые выходы инверторов 3 и 7, 4 и 8 соединены между собой, реализуя операции "Проводное И", и под«55 ключены ко входам 4 и 3 инверторов соответственно.

2 †. триггер работает следующим образом.

Еслибы =1, то при поступлении на вход С отрицательного фронта синхросигнала переключаются инверторы 9 и 1О в состояние С = 1, С = О. На вход инвертора 8 поступает логическая 1, которая устанавливает его в

I состояние О. Сигнал С = О устанавливает инверторы 5 и 6 в состояние I так что они не оказывают влияние на состояние выходов. Q u Q триггера.

Инверторы З..и 7, на входы которых поступает логический О, устанавливаются в состояние I, что приводит к установке инвертора 4 в состояние О. При этом установление управляющих сигназТов R, S, выходной БЯ осуществляется за время 2t>.. При поступлении иа вход С положительного:фронта синхросигнала переключается инвертор 9, на выходах которого устанавливается сигнал С = О, который переключает инверторы 8 и 10 в состояние 1. Состояние инверторов 3, 4 и 7 при этом не меняется. Так как сигнал С = 1, то на

1 входы инверторов 5 и 6 поступают уп! I равляющие сигналы S = I,R = О. Инверторы 5 и 6 устанавливаются в состояние О и l. соответственно, формируя на выходе триггера сигнал Q = О.

Инвертор 2, на вход которого поступает логический О, переходит в состояние 1, при этом на выходе триггера устанавливается сигнал Q = 1, и переводит инвертор 1. в состояние О. Состояние выходов триггера окончательно устанавливается за время 2 t3 после установки С = I.

Если 0 = 3, то при поступлении сигнала С = О инверторы 9 и 10 устанавливаются в состояние 1 и О соответственно. Инвертор 8 устанавливается в состояние 1, что приводит к установке инвертора 7 в состояние О, а инверторов 4 и 3 соответственно в состояние 1 и О. Состояние выходов Q и О триггера при этом не изменяется. При поступлении сигнала С = 1 инверторы 9 и IO устанавливаются в состояние С =0

С = 1. Инвертор 8 сохраняет состояI ние 1. На входы инверторов 5 и 6 not ступают сигналы S = SC = 0 и RI

RC = 1, которые устанавливают инI верторы 5 и 6 в состояния 1 и О соответственно, при этом Я = О. Инвертор 1, на вход которого поступает логический О, переключается в состояние 1, при этом Q = I а затем инвертор 2 переходит в состояние 0.

5 8431

Таким образом, предлагаемая схема функционирует как О-триггер, синхронизируемый положительным перепадом синхросигнала. При соединении выхода Я, со входом 0 триггер работает как Т-триггер.

Значения управляющих сигналов R u

5 устанавливаются спустя время 2t после поступления отрицательного фронта синхросигнала, а значения Q,Q - 1О спустя время 2t после поступления положительного фронта синхросигнала. Ми-. нимальный период следования синхросигналов составляет T .= 4t>, а максимальная рабочая частота — t = 1/4t>. 15 макс

Таким образом, максимальная рабочая частота предлагаемой схемы в

1,7 раза выше, чем для известной.

Предлагаемый триггер может быть реализован в интегральных микросхемах 20 на базе элементов интегральной инжекционной логики (И Л).или на многовыходных инверторах других типов.

76 6 подключены соответственно к первому ,и второму выходам, а вторые выходыко входам этих инверторов перекрестными связями,. вход пятого инвертора соединен с входом С, первый и второй выходы — с,первым и вторым входами ведущего триггера, с входами .третьего и четвертого инверторов этого триггера, и с третьим выходом четвертого инвертора и Звходом Р -триггера соответственно, а третий выход - с входом шестого инвертора, первый и второй выходы которого йодключены к первому и второму входам ведомого триггера, к входам третьего и четвертого ин-. верторов этого триггера, о т л и ч аю шийся тем, что, с целью повышения быстродействия, в каждом триггере первый и второй выходы третьего и четвертого инверторов соединены попарно с первым и вторник выходами первого и второго инверторов соответственно.

Формула изобретения

ВНИИПИ Заказ 51бО/79 Тираж 988 Подписное

Филиал ППП "Патент",r.ужгород,ул.Проектная,4

Синхронный D-триггер, содержащий ведущий и ведомый триггеры на четырех инверторах с двумя входами и двумя вы-рб ходами, в каждом триггере первые выходы первого и второго инверторов

Источники информации, принятые во внимание при экспертизе

1. Букреев И.И. и др. Микроэлектронные схемы цифровых устройств. М., 1975, с. 82, рис. 3.3.

2. Агаханян Т.М. и др. Интегральные триггеры устройств автоматики. М., 1978, с. 30, рис. 1.23.