Устройство для формирования задержкии длительности импульса

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцмалнстнчесимх

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к BBT. свид-ву (22) Заявлено 08.08.79(21) 2807376/18-21 (51)M. Кл.

Н 03 К 5/04

Н 03 К 5/13 с присоединением заявки №

Государственный комитет (23) Приоритет ио делам изобретений и открытий

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 30.06.81 (53) УДК 621.373. .5(088.8) (72) Авторы изобретения

А.А.Лоскутов, Г.И.Тенис и Н.Г.Бесова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ЗАДЕРЖКИ И ДЛИТЕЛЬНОСТИ

ИМПУЛЬСА

Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах..

Известны устройства формирования за« держки импульса, содержащие логические элементы и .интегрирующие R C - цепочки.

5 11.

Однако известные устройства содержат большое количество. элементов и имеют ограниченные функциональные возможности, 1 О так как формируют или задержки, или длительность импульса.

Известно устройство, в котором осуществляется и задержка, и формирование длительности импульса, обеспечиваемые т5 триггером с раздельными.входами, ждущими мультивибратором и промежуточным клапаном с тремя входами, к одному из которых подключен через конденсатор анод .диода и один иэ выкодов триггера, один из раздельных входов которого подключен к выкоду ждущего мультивибратора, второй вход и выход подключены к двум входам промежуточного клапайа, к выхо-.ду которого подключен вход ждущего муль тивибратора L2$.

Это устройство характеризуется ограниченными функциональными возможностями устройства формирования, не позволяющими работать с входными импульсами, длительность которых меньше времени задержки, отсутствиям диода и конденсатора на входе, что ухудшает помехоустойчивость при приеме сигналов с линии связи, большим количеством интегральнык схем (клапанов).

Цель изобретения - упрощение устрой ства и расширение его функциональных возможностей;

Укаэанная цель достигается тем, что в устройстве для формирования задержки и длительности импульса, содержащем блок задержки и блок формирования длительности импульса, блок задержки выполнен на двухвходовом логическом элементе

И - НЕ к входам которого соответственно подключены две к С - цепочки, другими концами подключенные к обшей шине источника питания, а блок формирования дли3 8432 тельности импульса, вход которого соединен с выходом блока задержки, содержит последовательно соединенные РС - цепочку и элемент И - HE.

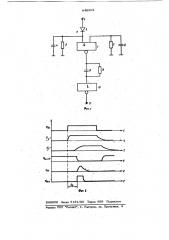

На фиг . 1 представлена принципиальная электрическая схема устройства.цля

5 формирования задержки и длительности, импульса; на фиг. 2 — временные диаграммы его работы.

Устройство формирования задержки и 10 длительности импульса соцержит элемент

И вЂ” HE 1, к одному из входов которого через диод 2 подключен вхоц устройства

3, и R С вЂ” цепочка, состоящая из конденсатора 4 и резистора 5. Ко второму 15 вхоцу элемента И - НЕ подключена RCцепочка, состоящая из конденсатора 6 и резистора 7. Выход элемента И - НЕ 1 через R C — цепочку, состоящую из конденсатора 8 и резистора 9,. подключен ко вхоцу элемента И вЂ” НЕ 10, выход которого. является выходом 11 устройства.

Устройство работает следующим образом.

04

4 та И вЂ” HE 1 станет равным нулю. Величина сопротивления этого резистора выбирается с таким расчетом, чтобы, вопервых, при незаряженном конценсаторе

6 можно было обеспечить уровень логического нуля на этом входе инвертора и, во — вторых, чтобы время разряца конценсатора 6 через этот резистор было не больше интервала следования вхоцных импульсов. Резистор 9 предназначен для разряда конценсатора 8 и выбирается таЛ ким, чтобы при открытом выходном транзисторе элемента И вЂ” HE 1 обеспечить1 уровень логической ециницы за счет собственного входного вытекающего тока;

Предлагаемое устройство формирования задержки и длительности импульса по сравнению с известными является более экономичным, обладает большими функциональными возможностями и позволяет довольно просто формировать импульс определенной длительности, задержанный относительно переднего фронта входного импульса и не зависящий в определенных пределах от его длительности.

На один из входов элемента И вЂ” НЕ 1 через диод 2 подается входной импульс, который заряжает конденсатор 4, К второму вхоцу этого элемента подключен конденсатор 6 и резистор 7. После того, как кон30 ценсатор 4 заряжен, входным вытекающим током заряжается конденсатор 6. Время заряца этого конденсатора определяется его величиной и сопротивлением резистора в базовой цепи мйогоэмиттерного транзистора микросхемы. Величина емкости конденсатора 6 выбирается с таким расчетом, чтобы время заряда этого конденсатора цо напряжения Ц равнялось цлительности задержки. После того, как кон- 0 ценсатор 6 заряцится, срабатывает элемент И вЂ” HE 1, и на входе его значение логического :"0", что обеспечивает возможность протекания тока заряда через конденсатор 8. Длительность протекания 45 этого тока определяет длительность стробирующего импульса. Резистор 5 предназначен цля расширения входного импульса до величины, перекрывающей время за.держки Ь,, а резистор 7 .предназначен 50 для разряда конденсатора 6 после того, как напряжение на втором входе элеменФормула изобретения устройство цля формирования зацержки и цлительности импульса, содержащее блок формирования цлительности импульса, о т л и ч а ю щ е е с я reM, что, с целью упрощения и расширения его функциональных возможностей, блок aaqepKKH выполнен на цвухвходовом логическом элементе И вЂ” HE,. к входам которого соответственно подключены две R С вЂ” цепочки, цругими концами подключенные к общей шине источника питания, а блок формирования длительности импульса, вход которого соединен с выходом блока задержки, соцержит последовательно соединенные 9.С - цепочку и элемент И - HE.

Источники информации, принятые во внимание при экспертизе

1. Заявка ФРГ No.2533427, кл. Н 03

К 5/23, 04.08.77.

2. Авторское свицетельство СССР

М 501474, кл. Н 03 К 5/13, 05.04.76 (прототип) .

848204

slue, Ug ф е

Ф

UAI14t

ВНИИПИ Заказ 5161/80 Тираж 988 Подписное

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4