Амлитудный ограничитель импульсов

Иллюстрации

Показать всеРеферат

< 643205

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свид-ву (22) Заявлено 01.10.79(21) 2849790/18-24 (51)lVL. Кл.

Н 03 К 5/08 с присоединением заявки РЙ

Геаудерстеенный камнтет

СССР (23) Приоритет (53) УДК 681.327 (088.8) Опубликовано 30.06.81. Бюллетень % 24

Дата опубликования описания 30.06.81 па делам нэабретеннй н аткрытнй (72) . Авторы изобретения

Г, Г.Тарасов и А. В. Киселев (7I) Заявитель (54) АМПЛИТУДНЫЙ ОГРА НИЧИТЕЛ Ь

HM ПУЛ ЬСОВ

Изобретение относится к импульсной технике и может быть использовано в усилителях воспроизведения запоминающих устройств, измерительных усилиях и т.п.

Известен амплитуцный ограничитель импульсов, который содержит выпрямитель, балансный каскад и источники напряжения

Г13.

Недостаток . этого устройства - низкая надежность.

Наиболее близкое к предлагаемому устройство, содержащее балансный каскад, соединенный соответствующим образом с выходом выпрямителя, и имеющее регулируемый порог срабатывания, устанавливаемый внешним источником напряжения 21.

Нецостаток известного устройстванизкая надежность вследствие зависимости порога срабатывания от источника. питания и малая амплитуда сигнала на выходе выпрямителя. Мф»

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в амплитудный ограничитель импуль-, сов, содержащий выпрямитель, первый эмиттерный повторитель и выходной каскад, выполненные на транзисторах одного типа проводимости, и элементы согласоаани на резисторах, причем базы транзисторов выпрямителя являются входами устройства„ коллекторы подключены к первой шине питания, а эмиттеры через первый резистор — ко второй шине питания, коллектор транзистора первого эмиттерного повтори.теля соецинен с шиной потенциала, а эмиттер через второй резистор - co второй шиной питания и через третий резистор - с базой одного. из транзистрров выходного блока, коллектор которого подключен к шине нулевого потенциала, а эмиттер - к эмиттеру другого. транзистора выходного

- блока и через четвертый резистор ко вто- . рой шине питания, коллектор цругого транзистора выходного блока является выходом устройства, введены второй эмиттерный повторитель и усилитель, выполненные на з 8432 транзисторах другого типа проводимости, диоды, пятый, шестой и седьмой реэис( торы, причем база транзистора второго эмиттерного повторителя соецинена с эмит- ° тером транзисторов выпрямителя, коллек5 тор поцключен ко второй шине питания, & эмиттер - к базе другого транзистора

Ъ выхоцного блока и через пятый резистор к шине нулевого потенциала, катоды циодов соединены сЬответственно с базами транзисторов выпрямителя, а аноды — с базой транзистора первого эмиттерного повторителя и через шестой резистор с первой шиной питания, база транзистора усилителя подключена к шине нулевого потен15 циала, коллектор транзистора усилителя соединен с базой одного из транзисторов выходного блока, а эмиттер через седьмой резистор соединен с третьей шиной питания.

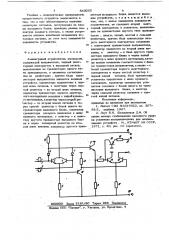

На чертеже изображена принципиальная . с хема. пре дла га емо го уст ройства.

Устройство имеет вхоцы 1 и 2 и содержит выпрямитель, выполненный на тран-25 зисторах 3 и 4,. первый резистор 5, диоды

6 и 7, втооой резистор 8, первый 9 и второй 10 эмиттерные повторители, третий 11, четвертый 12 и пятый 13 резис-i торы,,транзисторы 14 и 15 выходного кас- 0 каца, выполненного в виде баланс ого каскацаь усилитель 16, шестой 17 и седьмой

18 резисторы, первую 19,,вторую 20 и третью 21 шины питания. На чертеже обозначены также источники напряжения U

U< и U>, которые подключаются соответственно к первой 19, третьей 21 и второй 20 шинам питания. Базы транзисторов

3 и 4 выпрямителя являются входами 1 и

2 устройства соответственно, коллекторы 4о подключены к первой шине питания 19, а эмиттеры через первый резистор 5 - ко . второй шине питания 20. Коллектор тран. зистора первого эмиттерного повторителя

9 соединен с шиной нулевого потенциала, 45 а эмиттер через второй резистор 8 - со второй шиной питания 20 и через третий резистор 1 1 с базой одного иэ транзисторов 14 выкодного блока, коллектор которого подключен к шине нулевого потенциа-5о ла а эмиттер - к эмиттеру другого транзистора 15 выходного блока и через четвертый резистор 12 ко второй шине питания, Коллектор другого транзистора 15 выходного блока является. выходом устройства. База транзистора второго эмиттерного повторителя 10 соединена с эмиттерами транзисторов 3 и 4 выпрямителя, кол05 4 лектор подключен ко второй, шине питания.

20, а эмиттер — к базе другого транзистора

15 выходного .блока и через пятый резистор

13 к шине нулевого потенциала. Катоды диодов 6 и 7 соединены соответственно с базами транзисторов 3 и 4 выпрямителя, аноды - с базой транзистора первого амит» терного повторителя 9 и через шестой резистор 17 с первой шиной питания 19 .

База транзистора усилителя 16 подключена к шине нулевого потенциала, коллектор транзистора усилителя 16 соединен с базой одного иэ транзисторов 14 выходного блока, а эмиттер через седьмой резистор

18 соединен с третьей шиной питания 21.

Устройство работает следующим образом.

B исходном состоянии потенциалы на входах 1 и 2 токи диодов 6 и 7 и транзисторов 3 и 4 и потенциалы на эмиттерах транзисторов змиттерных повторителей

9 и 10 равны. При помощи источника U устанавливается эыиттерный ток транзистора усилителя 16, что определяет коппекторный ток этого транзистора и, следовательно, падение напряжения на третьем. резисторе 1 1, которое определяет порог срабатывания транзисторов 14 и 15 выходного блока. Ток коллектора 15 в том случае либо отсутствует, либо имеет допустимую величину, принимаемую эа логический "0".

При появлении на вкодак 1 и 2 дифференциального сигнала с полярностью, указанной на .чертеже, происходит перераспределение токов межцу циодами 6 и

7 и между транзисторами 3 и 4 . В результате этого происходит изменение потенциалов баз транзисторов эмиттерных повторителей 9 и 10, причем потенциал базы транзистора первого эмиттерного повторителя 9 повторяет потенциал входа 2, а потенциал базы транзистора второго эмиттерного повторителя 10 повторяет потенциал вкода 1. В результате амплитуды сигналов на эмиттерах транзисторов эмиттерных повторителей 9 и 10, которые поцводятся к транзисторам 14 и

15 выходного блока, примерно равны амплитуде входного сигнала. Стабильность порога срабатывания цостигается за счет устранения влияния изменений напряжения источника U+ на падение напряжения на третьем резисторе 1 1, которое определяется коллекторным током транзистора усилителя 16, который, в свою очередь зависит только от величины напряжения источника и величины. сопротивления седьмого резйстора 18.

5 843205 6

Технико — экономическое преимуществе зистора выходного блока является выхопредлагаемого устройста заключается в дом устройства, о т л и ч а ю т и и с я том, что в нем обеспечивается величина тем, что, с целью повышения надежности амплитуды сигналов, поступаюших на вхо- . ограничителя, он содержит второй эмитды выходного блока, примерно равная ам- 5 терний повторитель и усилитель, выполнен плитуде входного сигнала, а также устра- ные на транзисторах цругого типа проводи1 няется влияние колебаний напряжения ис- мости, диоды, пятый, шестой и седьмой точника питаниЯ, за счет чего повышаетсЯ резисторы, причем база транзистора втонадежность устройства. рого эмиттерного повторителя соединена с эмиттерами транзисторов выпрямителя, коллектор подключен «о второй шине пиФ о Р .м У л а и з о б Р е т е н и Я тания, а эмиттер - к базе другого транзистора выходного блока и через пятый

AMwtHTynHbia огРаничитель импУльсов, резистор к шине нулевого потенциала,катосодержащий выпРямитель, пеРвый эмит- 15 аы диодов соединены соответственно с базатерный повтоРитель и выходной каскад, ми транзисторов выпрямителя, а аноды - с выполненные на транзисторах одногО ти- . базой транзистора первого эмиттврного па приводимости, и эламенты согласова повторителя и через шестой Резистор с

1 ния на резисторах, причем базы тран- первой шиной питания, база транзистора зисторов выпрямителя являются входами >о усилителя подключена к шине нулевого устройста, коллекторы подключены к пер- потенциала, коллектор транзистора усивой шине питания, а эмиттеры через пер- . лителя соединен с базой одного из транвый резистор — ко второй шине питания, зисторов выходного блока, а эмиттер коллектор транзистора первого эмиттер- через сецьмой резистор соединен с тре- ного повторителя соединен с шиной иулево- тьей шиной питания.

25 го потенциала, а эмиттер через второй ре- Источники информации, .

)зистор — со второй шиной питания и че- принятые во внимание при экспертизе рез третий резистор с базой одного из . 1. Патент США %3316422, кл. 307транзисторов выходного блока, коллектор 88,5, опублик. 1967. транзистора . которого подключен к шине ЗО 2, Лаут В.H.. Шапошников Q.Ô. Об нулевого потенциала, а эмиттер - к эмит- одном, метоце стабилизации выходного уровтеру цругого транзистора выхоцного бло- ня усилителя воспроизведения для запомика и через четвертый резистор ко вто-. нающих устройств . М., ИТМиВТ АН СССР, рой шине питания, коллектор другого тран- 1971, с. 40, рис. 10 (прототип).

ВНИИПИ Заказ 6161/80 Т аж 988 Подписное

Филиал ППП Патент . r. Ужгород, ул. Проектная, 4