Двоично-десятичное пересчетноеустройство

Иллюстрации

Показать всеРеферат

ОП ИСАИ И Е

И ЗО6РЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскмх

Социалистлческмк

Реслубллк (1843248 (61) Дополнительное к авт. свид-ву № 746947 (22) Заявлено 05.03.79 (21) 2734744II18-21 с присоединением мявки №вЂ” (23) Приоритет—

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 (51) М. Кл.

Н 03 К 23/02

Гееудерстееииые иемитет

СССР (53) УДК 621.374..32 (088.8) llo лелем изебретеиий и аткрытий (72) Авторы изобретения

Н. И. Сементовский, Н. И. Алексееенко и В. Н. Гущина (71) заявители (54) ДВОИЧНО-ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ

УСТРОЙСТВО

Изобретение относится к электронной и вычислительной технике и может быть использовано в цифровых системах автоматического контроля и управления.

По основному авт. св. № 746947 извест-. но двоично-десятичное пересчетное устройство, содержащее двоичный реверсивный счетчик, дешифратор и формирователь, счетный вход двоичного реверсивного счетчика соединен со счетным входом двоично-десятичного пересчетного устройства, управляющий вход которого соединен с управляющим входом двоичного реверсивного счетчика, прямь1е выходы второго и четвертого разрядов которого соединены с входами дешифратора, выход ..которого соединен с первым входом формирователя, выход которого соединен с установочными входами второго и третьего разрядов двоичного реверсивного счетчика, вспомогательный вход формирователя соединен с управляющим входом двоич но-десятичного пересчетного устройства, счетный вход которого соединен с входом инвертора, выход которого соединен с дополнительным входом формирователя, вспомогателььный выход которого соединен с установочными входами первого и четверто го разрядов двоичного реверсивного счетчика. Формирователь содержит триггер и элемент И-НЕ, входы и выход которого соединены соответственно с вспомогательным входом формирователя, прямым выходом триггера и вспомогательным выходом формирователя, дополнительный вход и выход которого соединены соответственно с первым управляющим входом и инверсным выходом триггера, второй управляющий вход которого соединен с первым входом формирователя (1) .

Недостаток известного устройства — снижение быстродействия устройства в целом из-за необходимости применять в формирователе триггер с быстродействием более низким, чем быстродействие триггеров двоичного реверсивного счетчика, поскольку при высоком быстродействии триггера, он реагирует на импульсы с выхода дешифратора, возникающие при переходных процессах в триггерах счетчика с последовательным переносом.

20 Цель изобретения — повышение быстродействия.

Для достижения этой цели в двоичнодесятичном пересчетном устройстве, содер843248 жащем двоичный реверсивный счетчик, дешифратор, инвертор и формирователь, дополнительный вход дешифратора соединен с инверсным выходом счетного триггера первого разряда двоичного реверсивного счетчика, выход переполнения по вычитанию .которого подключен ко второму дополнительному входу формирователя.

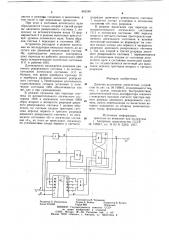

На чертеже представлена структурная электрическая схема двоично-десятичного пересчетного устройства.

Двоично-десятичное пересчетное устройство содержит двоичный реверсивный счетчик 1, дешифратора 2, формирователь 3 и инвертор 4, Счетный вход двоичного реверсивного счетчика 1 соединен со счетным входом 5 двоично-десятичного пересчетного устройства. Управляющий вход б устройства соединен с управляющим входом двоичного реверсивного счетчика I.

Прямые выходы второго и четвертого и инверсный выход первого разрядов счетчика 1 соединены с входами дешифратора 2.

Выход дешифратора 2 соединен с первым входом 7 формирователя 3.

Шина 8 импульсов переполнения по вычитанию двоичного реверсивного счетчика I соединена со вторым дополнительным входо м 9 фор м и рова теля 3.

Первый 7 и второй 9 дополнительный входы формирователя 3 соединены со вторым управляющим входом триггера 10 на

его многовходовой схеме И-НЕ 11.

Выход 12 формирователя 3 соединен с установочными входами второго и третьего разрядов двоичного реверсивного счетчика 1.

Вспомогательный вход 13 формирователя 3 соединен с управляющим входом б двоично-десятичного пересчетного устройства.

Счетный вход 5 устройства соединен с входом инвертора 4. Выход инвертора 4 соединен с дополнительным входом 14 формирователя 3, вспомогательный выход 15 которого соединен с установочными входами первого и четвертого разрядов двоичного реверсивного счетчика 1.

Двоично-десятичное пересчетное устройство работает следующим образом.

В исходном состоянии двоичный реверсивный счетчик I находится в состоянии логического нуля и на выходах всех разрядов этого счетчика нулевые логические состояния. Н а входе 5 — устройства — еди ни ч н ы и логический сигнал, а триггер 10 находится в нулевом логическом состоянии.

Устройство изменяет свое состояние от нуля до девяти и от девяти до нуля в режимах соответственно сложения и вычитания, как обычный двоичный реверсивный счетчик благодаря сложению или вычитанию, осуществляемому двоичным реверсивным счетчиком 1.

В режиме сложения десятый импульс переводит двоичный реверсивный счетчик 1 из логического состояния 1001 во вспомо50

5

45 гательное логическое состояние 1010, при этом на все три входа дешифратора 2 поступают уровни логической единицы. Подобный набор сигналов на входах дешифратора

2 больше не появляется ни в режиме вычитания, ни в режиме сложения, в том числе и при переходных процессах.

С выхода дешифратора 2 поступает на первый вход 7 формирователя 3 сигнал установки триггера 10 в состояние логической единицы. При этом на первом управляющем входе триггера 10 в это время присутствует сигнал, не мешающий установке триггера

10 в состояние логической единицы.

С инверсного выхода триггера 10 уровень логического нуля поступает через выход !2 формирователя 3 на установочные входы второго и третьего разрядов двоичного реверсивного счетчика 1, устанавливая их в состояние логического нуля.

Одновременно уровень логической единицы с прямого выхода триггера !О и вспомогательного входа 13 обуславливает на выходе элемента И-НЕ 11 уровень логического нуля, который обеспечивает установку в «О» первого и четвертого разрядов двоичного реверсивного счетчика l. Таким образом, в режиме сложения сразу же после достижения вспомогательного логического состояния 1010 устройство переходит в логическое состояние 0000. Длительность нахождения счетчика 1 в логическом состоянии 1010 не больше, чем суммарное время срабатывания дешифратора 2, переброса триггера IO срабатывания элементов И-НЕ 11 и переброса разрядов двоичного реверсивного счетчика 1, Триггер 10 хранит состояние логической единицы до прихода паузы между входными импульсами, которая обеспечивает на входе триггера 10 . сигнал установки его в исходное состояние логического нуля. Таким образом, обеспечивается вполне достаточная длительность существования сигнала установки счетчика I в логическое состояние 0000.

В режиме вычитания двоичный реверсивный счетчик 1 переходит после прихода первого импульса из исходного логического состояния 0000 во вспомогательное логическое состояние 1111, при этом дешифратор 2 не выдает сигнал на изменение состояния триггера 10, так как íà его входе присутствует сигнал Q1 равный логическому нулю.

В режиме вычитания изменение состояния триггера 10 осуществляется импульсом, полученным диффренцированием перепада из «1» в «О» на инверсном выходе старшего счетного триггера двоичного реверсивного счетчика 1, т.е. установка триггера 0 в состояние логической единицы осуществляется в режиме вычитания от шины 8 выходных диффренцированных импульсов переполнения по вычитанию двоичного реверсивного счетчика. Подобный сигнал больше не появ843248

1 в разрядов двоичного реверсивного счетчика

I подается сигнал установки в логическое состояние «О» этих разрядов.

В режиме вычитания при переходе из вспомогательного логического состояния

Illl в логическое состояние 1001 переход второго и третьего счетных триггеров из единичного логического состояния в нулевое логическое состояние не формирует на счетных входах сигнал для первого и четвертого разрядов двоичного реверсивного счетчика

1, так как второй и третий разряды двоичного реверсивного счетчика 1 переключаются

О по установочным входам от состояния логического нуля к состоянию логической единицы, т.е. осуществляется несчетный для вычитания переход триггеров второго и третьего разрядов.

Формула изобретения ляется в режимах сложения и вычитания, том числе и при,переходных процессах.

При этом в состояние логического нуля сбрасываются только второй и третий разря ды двоичного реверсивного счетчика I, по скольку на вспомогательном входе 13 фор мирователя 3 в режиме вычитания присутст вует уровень логического нуля. Таким обра зом счетчик 1 переходит в состояние 1001.

Устройство реагирует в режиме вычита ния на последующие импульсы вплоть до де сятого как двоичный вычитающий счетчик

На одиннадцатом импульсе повторяется цикл перехода из рабочего логического 000 через вспомогательное логическое состояние !

ill в рабочее 1001.

Длительность нахождения разрядов дво ичного реверсивного счетчика 1 во вспомо гательном логическом состоянии 1111 не больше, чем время переброса триггера 10 и переброса разрядов двоичного реверсивного счетчика 1. Необходимая длительность существования сигнала установки в логическое состояние 1001 обеспечивается так же, как и при суммировании.

В режиме сложения при переходе счет- чика из вспомогательного логического состояния 1010 в логическое состояние 0000 . сброс второго и четвертого разрядов двоичного реверсивного счетчика должен обеспечить по счетным входам триггеров счетчика переход первого и третьего разрядов двоичного реверсивного счетчика 1 из логического состояния «О» в логическое состоя- 30 ние «1», но этого не происходит, поскольку на установочные входы первого и третьего

Двоично-десятичное пересчетное устройство по авт. св. № 746947, отличающееся тем, что, с целью повышения быстродействия, дополнительный вход дешифратора соединен с инверсным выходом счетного триггера первого разряда двоичного реверсивного счетчика, выход переполнения по вычитанию которого подключен ко второму дополнительному входу формирователя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 746947, кл. Н 03 К 23/02, !977.

Составитель В. Чернышев

Редактор Л. Пчелинская Техред А. Бойкас Корректор В. Бутяга

Заказ 5164 82 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035., Москва, % — 35, Раушская наб., д. 4/5

Филиал ППП «Патент»; г. Ужгород, ул. Проектная, 4