Устройство защиты от ошибок

Иллюстрации

Показать всеРеферат

Союз Советсимк

Социалистические республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii)843267 (б1) Дополнительное к аит. свид-ву (22) Заявлено 30.08. 79 (21) 2813510/18-09 с присоединением заявки № (23) Приоритет

Опубликовано 30.06.81, Бюллетень ¹ 24 (51)M. Кл.

Н 04 L 1/.10

Государственные комитет по «елем необретеннй и открытнй (5З) УДК 621. 395. .664 (088.8) Дата опубликования описания 30 .06.81 (72) Авторы изобретения

А.Г. Дотолев, А.П.Кивачицкий, В.В.К

Всесоюзный научно-исследовательский комплексной автоматизации мелиорати (7l) Заявитель (54) УСТРОЙСТВО ЗАЩИТЫ ОТ ОНИБОК

Изобретение относится к технике связи и может использоваться в аппаратуре передачи данных для защиты от ошибок.

Известно устройство зашиты от ошибок, содержащее приемник, .выход .

5 двоичных сигналов которого подключен ко входу первого и-разрядного регистра сдвига, и выходов которого подключены к соответствующим входам блока проверки на четность, второй и-разрядный регистр сдвига, вход которого соединен с выходом детектора качества, вход которого соединен с другим выходом приемника, а и выходов первого и-разрядного регистра сдвига подключены к соответствующим входам блока запрета с0.

Однако известное устройство имеет низкую достоверность принимаемой информации.

Цель изобретения - повышение достоверности принимаемой информации.

Для этого в устройство защиты от ошибок, содержащее приемник, вы-, ход двоичных сигналов которого подключен ко входу первого и-разрядного регистра сдвига, и выходов которого подключены к соответствующим входам блока проверки на четность, второй и-разрядный регистр сдвига, вход которого соединен с выходом детектора качества, вход которого соединен с другим выходом приемника, а и выходов первого п разрядного регистра сдвига подключены к соответствующим входам блока запрета, введены и трехвходовых элементов совпадения, (и+1) двухвходовых элементов совпадения, пороговый элемент и инвертор, при этом первый выход блока проверки на четиость подключен к объединенным первым входам (и+1) двухвходовых элементов совпадения, вторые входы и которых объединены с соответствующими входами блока запрета и входами порогового элемента, а выходы — под843267 ф ключены к соответствующим входам первого п-разрядного регистра сдвига, второй выход блока проверки на четI ность подключен к объединенным первым входам трехвходовых элементов совпадения,-вторые входы которых соединены с соответствующими выходами первого и-разрядного регистра сдвига, третьи входы объединены и соединены с выходом инвертора, вход которого соединен с объединенным выходом порогового элемента и с выходом (и+1) двухвходового элемента совпадения, другой вход которого соединен с выходом блока запрета.

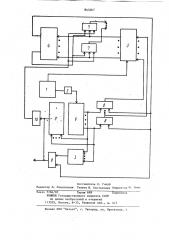

На чертеже представлена структурная электрическая схема устройства.

Устройство защиты от ошибок содержит приемник 1 с детектором 2 качества, блок 3 запрета, блок 4 про- . верки на четность, первый и второй

tl-разрядные регистры 5 и 6 сдвига соответственно, и трехвходовых элементов 7 совпадения, (п+1) двухвходовых элементов 8 совпадения, пороговый элемент 9, инвертор 1О.

Устройство работает следующим образом.

В исходном положении на выходе инвертора 10, связанного с третьими входами и-трехвходовых элементов 7 совпадения, подан разрешающий импульс

Принимаемая кодовая комбинация из приемника I в и-разрядном двоичном коде записывается в первый и-разрядный регистр 5 сдвига, а с детектора

2 качества во второй и-разрядный регистр 6 сдвига — вектор ошибки.

Из первого п-разрядного регистра 5 сдвига кодовая комбинация поступает на проверку в блок 4 проверки на четность, в результате которой он вырабатывает либо сигнзл "Правильно", либо — "Ошибка". Сигнал "Правильно" . поступает на вторые входы трехвходовых элементов 7 совпадения, которые при наличии разрешающего сигнала инвертора 10 в параллельном коде выдают информацию потребителю. Если принятая кодовая комбинация определе" на блоком 4 проверки на четность как недостоверная, он вырабатывает сигнал "Ошибка" и подает его на вто.рые входы двухвходовых элементов 8 совпадения, одна из которых, на ко.торую поступает импульс ошибочной ! ячейки .второго п-разрядного регистра

Формула изобретения

Устройство защиты от ошибок, содержащее приЕмник, выход двоичных сигналов которого подключен ко входу первого и-разрядного регистра сдвига, п выходов которого подключены

45 к соответствующим входам блока проверки на четность, второй и-разрядный регистр сдвига, вход которого соединен с выходом детектора качества, вход которого соединен с другим

50 выходом приемника, а и выходов первого и-разрядного регистра сдвига подключены к соответствующим входам блока запрета, о т л и ч а ю ц е—

55 е с я тем, что, с целью повышения достоверности принимаемой информации, введены и трехвходовых элементов совпадения, (n+1) двухвходовых эле-, ментов совпадения, пороговый элемен1

I0

6 сдвига, вырабатывает на ошибочной ячейке первого и-разрядного регистра сдвига. 5 исправляющий импульс.

Исправленная комбинация из ячеек первого и-разрядного регистра сдвига

5 проверяется блоком 4 проверки на четкость и выдается потребителю.

При наличии во втором и-разрядном регистре сдвига 6 двух и более ошибок последний заставляет срабатывать пороговый элемент 9, выходной сигнал которого инвертирует сигнал на входе инвертора 10 запрещающий выдачу информации, и формирует запрос на повторение кодовой комбинации. При необнаружении ошибки детектором качества 2 второй п-разрядный регистр

6 сдвига содержит нулевой вектор ошибки и при наличии сигнала Ошибка" блока 4 блок 3 запрета через (n+1) двухвходовый элемент совпадения 8 подает сигнал на вход инвертора 10, запрещающий выдачу информации потребителю, и формирующий запрос на повтор ение по сылки .

Таким образом, предлагаемое устройство позволяет исправлять одиночные ошибки, не меняя надежности работы устройства с блоком проверки на четность и детектором качества, и повышает скорость передачи информации, так как вследствие исправления одиночных ошибок, составляющих большой процент в кодовых комбинациях различной длины, значительно сокращается суммарное время на переспросы.

84326 и инвертор, при этом первый выход блока проверки на четность подклю-, чен к объединенным первым входам (и+1) двухвходовых элементов совпадения, вторые входы и которых объединены с соответствующими входами блока запрета и входами порогового элемента, а выходы — подключены к соответствующим входам первого 0-разрядного регистра сдвига, второй выход 10 блока проверки на четнасть подключены к объединенным первым входам трехвходовых элементов совпадения, вторые входы которых соединены с соответствующими выходами первого и-разрядного 15

7 6 регистра сдвига, третьи входы объединены и соединены с выходом инвертора, вход которого соединен с объединенным выходом порогового элемента и с выходом (и+1)-двухвходового элемента совпадения, другой вход которого соединен с выходом блока запрета.

Источники информации, принятые во внимание при экспертизе

1. Котов П.А. Повышение достовер" ности передачи цифровой информации.

M., "Связь", 1966, с.137-139 (прототип). 843267

Составитель E. Голуб

Редактор Л. Пчелинская Техред Ж. Кастелевич Корректор M. 11o+o

Заказ 5166 83 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4