Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Реслублик

О Il И С А Н И Е ()843271

ИЗЬВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 1L09 79 (21) 2824659/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

Н 04 L 7/02

ГееКдарстееииые кемитет

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 (53) УДК 621.394.

662 (088 8) по делам изобретеиий и еткрмтий (72) Авторы изобретения

Ю. В. Шевченко, Л. Ф. Кузнецов и С. Н. Внук

Одесский электротехнический институт связи 1 им. А. С. Попова (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к электросвязи и может использоваться для выделения колебаний тактовой частоты в системах передачи данных с амплитудно-фазовой модуляцией.

Известно устройство тактовой синхронизации, содержащее реверсивный счетчик и последовательно соединенные задающий генератор, блок добавления-вычитания и первый делитель частоты (1) .

Однако известное устройство характеризуется недостаточной помехоустойчивостью.

Цель изобретения — повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройство тактовой синхронизации, содержащее реверсивный счетчик и последовательно соединенные задающий генератор, блок добавления-вычитания и первый делитель частоты, введены анализатор межсимвольных искажений (МСИ) преобразователь, два коммутатора сигналов, второй делитель частоты, блок формирования импульсов установки и считывания, блок памяти и блок формирования отстающих и опережающих стробимпульсов, при этом выход анализатора МСИ через .преобразователь подключен к одному из входов первого коммутатора сигналов, два выхода которого подключены к соответствующим входам реверсивного счетчика, установочный вход которого соединен с одним из входов блока формирования импульсов установки и считывания, другой выход которого подсоединен к одному из входов блока памяти, второй вход которого соединен с выходом реверсивного счетчика, а выход блока памяти соединен с одним из входов блока добавления — вычитания, к управляющему входу которого и к управляющим входам первого и второго коммутаторов сигналов и блока формирования импульсов установки и считывания подключен выход второго делителя частоты, к входу которого подключе1з ны вход блока формирования отстающих и опережающих стробимпульсов и выход первого делителя частоты, который одновременно является выходом устройства, при этом выходы блока формирования отстающих и опережающих стробимпульсов подключены к соответствующим входам второго коммутатора сигналов, выход которого подключен к второму входу анализатора МСИ.

843271

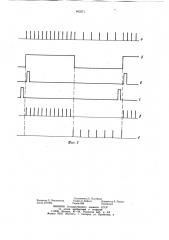

На фиг, I представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит анализатор 1 МСИ, преобразователь 2, коммутаторы 3 и 4 сигналов, делитель 5 частоты, блок 6 формирования импульсов установки и считывания, реверсивный счетчик 7, блок 8 памяти, блок

9 формирования отстающих и опережающих стробимпульсов, делитель 10 частоты, блок

11 добавления-вычитатания и задающий генератор 12.

Предлагаемое устройство работает следующим образом.

Входной сигнал в виде глазковой диаграммы поступает в анализатор 1. Последний представляет собой устройство, определяющее мощность интерференционной помехи, либо Е-критерий. Сигнал с выхода анализатора 1 МСИ подключается к преобразователю 2, а выход последнего подается на сигнальный вход коммутатора 4.

Ко второму коммутирующему входу коммутатора 4 подключается сигнал с выхода делителя 5 частоты. Коммутатор 4 работает таким образом, что полпериода сигнала на выходе делителя 5 импульсы с выхода преобразователя 2 коммутируются на один выход коммутатора 4 и подлючаются ко входу «Добавление» реверсивного счетчика 7, а последующие полпериода сигнала на выходе делителя 5 импульсы с выхода преобразователя 2 коммутируются на второй выход коммутатора 4 и подключаются ко входу «Вычитание» реверсивного счетчика 7.

При этом на установочный вход реверсивного счетчика 7 подключается сигнал с одного из выходов»Установка» блока 6 формирования импульсов установки и считывания, вход которого соединен с выходом делителя 5. Другой выход «Считывание» блока 6 формирования импульсов установки и считывания подключается к блоку 8 памяти, на второй вход которого подключается сигнал с выхода последнего разряда реверсивного счетчика 7. В начале периода сигнала с выхода делителя 5 частоты (фиг. 2 б) формирует с помощью блока 6 импульс установки (фиг. 2 в), который устанавливает реверсивный счетчик 7 в центральное положение (последний разряд в «1«, а все остальные в «О»). Затем импульсы с выхода преобразователя 2 (фиг. 2 а), первые полпериода сигнала с выхода делителя 5 частоты (фиг. 2 б) подаются с помощью коммутатора 4 на вход «Добавление» реверсивного счетчика 7 (фиг. 2д), а вторые полпериода сигнала (фиг. 2 б) — на вход

«Вычитание» (фиг. 2 е). В конце периода сигнала с выхода делителя 5 (фиг. 2б) происходит считывание состояния реверсивного счетчика 7 с помощью импульсов считывания (фиг. 2г) и блока 8 памяти, который

55 запоминает состояние последнего разряда реверсивного счетчика 7 до следующего прихода импульса считывания. В качестве блока 8 может использоваться D-триггер. Рассмотренные процессы повторяются на каждом периоде сигнала с выхода делителя 5 частоты. Таким образом, можно определить знак разности количества импульсов с выхода преобразователя 2 на первом и втором полупериодах сигнала на выходе делителя 5 частоты.

Сигнал иа выходе блока 8 памяти подключается к управляющему входу блока 11 добавления-вычитания, с помощью которого вставляются либо исключаются импульсы от задающего генератора 12. Этот процесс происходит с частотой сигнала, поступающего на блок 11 добавления-вычитания от делителя 5 частоты. Таким образом с помощью сигнала с выхода блока 8 памяти можно управлять приращения фазы сигнала на выходе делителя 10 частоты.

Сигнал с выхода делителя 10, который является одновременно и выходным сигналом устройства, подключается ко входам делителя 5 и блока 9 формирования отстающих и опережающих стробимпульсов, оба выхода которого подключаются к сигнальным входам коммутатора 3. сигналов, коммутирующий вход которого соединен с выходом делителя 5. Выход коммутатора 3 подключен к одному из входов анализатора.

1 МСИ.

Блок 9 формирования отстающих и опережающих стробимпульсов формирует на своих выходах две последовательности стробимпульсов с частотой тактового колебания, сдвинутые по отношению к выходному колебанию (выход делителя 10) на интервал

+ At. Эти две последовательности импульсов пОдаются через коммутатор 3 на анализатор 1, так что первые полпериода колебания на выходе делителя 5 поступают импульсы со двигом + At, а вторые полпериода импульсы со сдвигом - At.

Предлагаемое устройство необходимо для отслеживания минимального значения величины среднеквадратичной погрешности, определяемого анализатором 1 МСИ. Этот минимум отслеживается следующим образом.

Анализатор 1 МСИ определяет среднеквадратичную ошибку в момент прихода стробимпульса с выхода коммутатора 3.

Поскольку коммутаторы 3 и 4 работают синхронно, то величина среднеквадратичной ошибки, полученная в момент стробимпульсов со сдвигом + At, и преобразования в частоту импульсов на выходе преобразователя 2 поступает на вход «Добавление», реверсивного счетчика 7, а в момент стробирования со сдвигом - At на вход «вычитание» реверсивного счетчика. После этого с помощью блока 8 определяется знак при843271

Формула изобретения

5 ращения величины среднеквадратичной ошибки. С помощью знака приращения фаза местного генератора (блоки 10 — 12) изменяется таким образом, что фаза выходного сигнала стремится к точке минимального значения величины среднеквадратичной ошибки.

Таким образом, поскольку устройство тактовой синхронизации отслеживает минимальное значение величины среднеквадратичной погрешности, то оно является более помехоустойчивым к линейным искажениям, существующим в канале, причем этот минимум отслеживается всегда и независимо от характера линейных искажений.

Устройство тактовой синхронизации, содержащее реверсивный счетчик и последовательно соединенные задающий генератор, 2о блок добавления-вычитания и первый делитель частоты, отличающееся тем, что, с целью повышения помехоустойчивости, введены анализатор: межсимвольных искажений, преобразователь; два коммутатора

25 сигналов, второй делитель частоты, блок формирования импульсов установки и считывания, блок памяти и блок формирования отстающих и опережающих стробимпульсов, при этом выход анализатора МСИ через

6 преобразователь подключен к одному из входов первого коммутатора сигналов, два выхода которого подключены к соответствующим входам реверсивного счетчика, установочный вход которого соединен с одним из выходов блока формирования импульсов установки и считывания, другой выход которого подсоединен к одному из входов блока памяти, второй вход которого соединен с выходом реверсивного счетчика, а выход блока памяти соединен с одним из входов блока добавления-вычитания, к управляющему входу которого и к управляющим входам первого и второго коммутаторов сигналов и блока формирования импульсов установки и считывания подключен выход второго делителя частоты, к входу которого подсоединены вход блока формирования отстающих и опережающих стробимпульсов и выход первого делителя частоты, который одновременно является выходом устройства, при этом выходы блока формирования отстающих и опережающих стробимпульсов подключены к соответствующим входам второго коммутатора сигналов, выход которого подключен к второму входу анализатора МСИ.

Источники информации пРинятые во внимание при экспертизе

1. Тамм Ю. А. Адаптивная коррекция сигнала ПД. М., «Связь», 1978, с. 7Р; рис. 3.2 (прототип) .

zuzrrmr

puz. r

843271

Составитель Е. Погиблов

Редактор Л. Пчелииская Техред А. Бойкас Корректор Е. Рошко

Заказ 5167/84 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, % — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4