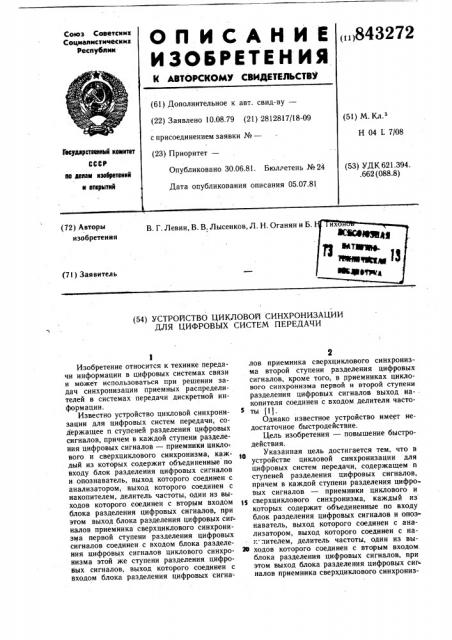

Устройство цикловой синхронизации дляцифровых систем передачи

Иллюстрации

Показать всеРеферат

ИСАНИЕ

Союз Советсккк

Соцмалмстическик

Реслублик

< >843272

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (51) М Кл з (22) Заявлено 10.08.79 (21) 2812817/18-09

Н 04 L 7/08 с присоединением заявки №вЂ”

Гвсударстееннмй кемнтет

СССР (23) Приоритет—

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 (53) УДК 621.394..662 (088.8) IN делам нзебретеннй к еткрмтнй (72) Авторы изобретения

В. Г. Левин, В. В. Лысенков, Л. Н. Оганян и Б. (71) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

ДЛЯ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ

Изобретение относится к технике передачи информации в цифровых системах связи и может использоваться при решении задач синхронизации приемных распределителей в системах передачи дискретной информации.

Известно устройство цикловой синхронизации для цифровых систем передачи, содержащее и ступеней разделения цифровых сигналов, причем в каждой ступени разделения цифровых сигналов — приемники цикло-.. вого и сверхциклового синхронизма, каждый из которых содержит объединенные по входу блок разделения цифровых сигналов и. опознаватель, выход которого соединен с анализатором, выход которого соединен с накопителем, делитель частоты, один из выходов которого соединен с вторым входом блока разделения цифровых сигналов, при этом выход блока разделения цифровых сигналов приемника сверхциклового синхронизма первой ступени разделения цифровых сигналов соединен с входом блока разделения цифровых сигналов циклового синхронизма этой же ступени разделения цифровых сигналов, выход которого соединен с входом блока разделения цифровых сигналов приемника сверхциклового синхронизма второй ступени разделения цифровых сигналов, кроме того, в приемниках циклового синхронизма первой и второй ступени разделения цифровых сигналов выход на- . копителя соединен с входом делителя частоты (1).

Однако известное устройство имеет недостаточное быстродействие.

Цель изобретения — повышение быстродействия.

Указанная цель достигается тем, что в устройстве цикловой синхронизации для цифровых систем передачи, содержащем и ступеней разделения цифровых сигналов, причем в каждой ступени разделения цифровых сигналов — приемники циклового и д сверхциклового синхронизма, каждый из которых содержит объединенные по входу блок разделения цифровых сигналов и опознаватель, выход которого соединен с анализатором, выход которого соединен с нак-пителем, делитель частоты, один из вы26 ходов которого соединен с вторым входом. блока разделения цифровых сигналов, при этом выход блока разделения цифровых сигналов приемника сверхциклового синхрониз843272 ма первой ступени разделения цифровых сигналов соединен с входом блока разделения цифровых сигналов приемника циклового синхронизма этой же ступени разделения цифровых сигналов, выход которого соединен с входом блока разделения цифровых сигналов приемника сверхциклового синхронизма второй ступени разделения цифровых сигналов, кроме того, в приемниках циклового синхронизма первой и второй ступени разделения цифровых сигналов выход накопителя соединен с,входом делителя частоты, в приемник циклового синхронизма первой ступени разделения цифровых сигналов введены формирователь сигналов блокировки и блок управления, входы которого соединены с выходами накопителей приемников циклового и сверхциклового синхронизма, а выход — с входом формирователя сигналов блокировки, выход которого подключен к соответствующему входу блока разделения цифровых сигналов, при этом выходы накопителей приемников сверхциклового синхронизма первой и второй ступеней разделения цифровых сигналов соединены с входами соответствующих делителей частоты и с вторыми входами накопителей приемников циклового синхронизма соответствующих ступеней разделения цифровых сигналов, кроме того, в приемник сверхциклового синхронизма второй ступени разделения цифровых сигналов введен приемник сигнала блокировки, вход которого объединен с входом блока разделения цифровых сигналов прием ника сверхциклового синхронизма второй ступени разделения цифровых сигналов, а выход — с вторым входом накопителя приемника сверхциклового синхронизма.

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит сгупени 1 и 2 разделения цифровых сигналов, каждая из которых включает приемник 3 сверхциклового и приемник 4 циклового синхронизма, каждый из которых содержит опознаватель 5, анализатор 6, накопитель 7 и делитель 8 частоты. Кроме того, приемник 4 циклового синхронизма ступени 1 содержит блок

9 управления, формирователь 10 сигналов блокировки, а приемник 3 сверхциклового синхронизма ступени 2 содержит приемник

11 сигнала блокировки, а каждый из приемников 3 и 4 первой и второй ступени содержит блоки 12 и 13 разделения цифровых сигнлов.

Устройство работает следующим образом

В устройстве контроль за состоянием синхронизма осуществляется с помощью опознавателей 5 и анализаторов 6 в каждом при емнике 3 и 4, а процесс восстановления синхронизма происходит вначале в приемнике

3 сверхциклового синхронизма после заполнения накопителя 7 по выходу синхронизма этого приемника 3, а затем в приемФормула изобретения

Устройство цикловой синхронизации для цифровых систем передачи, содержащее п ступеней разделения цифровых сигналов, причем в каждой ступени разделения цифровых сигналов — приемники циклового и сверхциклового синхронизма, каждый из которых содержит объединенные по входу блок разделения цифровых сигналов и опознаватель, выход которого. соединен с анализатором, выход которого соединен с накопителем, делитель частоты, один из выходов которого соединен с вторым входом блока разделения цифровых сигналов, при этом выход блока разделения цифровых сигналов приемника сверхциклового синхронизма первой ступени разделения цифровых сигналов соединике 4 циклового синхронизма. Это достигается тем, что один из выходов накопителя

7 по выходу из синхронизма приемника 3 связан с выходом «сброс» накопителя 7 приемника 4. Поэтому при нарушении фаS зы входного цифрового сигнала, последовательно срабатывают приемник 4 сверхциклового синхронизма, а затем приемник 4 циклового синхроизма. Если нарушается фаза только цикла, то соответственно срабатывает только приемник по циклам.

1О

Таким образом, в предлагаемом устройстве исключается возможность повторного поиска синхронизма, что сокращает среднее время отсутствия циклового синхронизма в каждой ступени. Кроме того, в предлагаемом устройстве исключается возможность размножения сбоя циклового синхронизма в низшую ступень разделения цифровых потоков, т. е. осуществление процесса поиска в приемниках 4 циклового синхро20 низма первой ступени разделения цифровых сигналов не приводит к ложному началу поиска во второй ступени разделения. Это обеспечивается тем, что одновременно с началом поиска синхронизма в любом из приемников 3 или 4 первой ступени разделения цифровых сигналов по команде с выходов заполненных накопителей 7 включается формирователь 10 сигналов блокировки и сигнал блокировки передается во вторую, низшую ступень разделения, где зп принимается приемником 1! сигнала блокировки, блокируя оба приемника низшей ступени через цепи «сброс« соответствующих накопителей. Тем самым сокращается общее время отсутствия циклового синхронизма в рассматриваемой двухступенчатой

З5 системе передачи и, следовательно повышается быстродействие устройства по сравнению с известным.

При необходимости, предлагаемую схему устройства можно распространить и на цифровую систему передачи с числом ступеней разделения более двух.

843272

Составитель Е. Погиблов

Редактор Ю. Ковач Техред А. Бой кас Корректор М. Шароши

Заказ 5167/84 Тираж 698 Подписное

ВНИИПИ . Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ж — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 нен с входом блока разделения цифровых сигналов приемника циклового синхронизма этой же ступени разделения цифровых сигналов, выход которого соединен с входом блока разделения цифровых сигналов приемника сверхциклового синхронизма второй ступени разделения цифровых сигналов, кроме того, в приемниках циклового синхронизма первой и второй ступени разделения цифровых сигналов выход накопителя соединен с входом делителя частоты, отличающееся тем, что, с целью повышения быстродействия, в приемник циклового синхронизма первой ступени разделения цифровых сигналов введены формирователь сигналов блокировки и блок управления, входы которого соединены с выходами накопителей приемников циклового и сверхциклового синхронизма, а выход — с входом формирователя сигналов блокировки, выход которого подключен к соответствующему входу блока разделения цифровых сигналов, при этом выходы накопителей приемников сверхциклового синхронизма первой и второй ступеней разделения цифровых сигналов соединены с входами соответствующих делителей частоты и с вторыми входами накопителей приемников циклового синхронизма соответствующих ступеней разделения цифровых сигналов, кроме того, в приемник сверхцнклового синхронизма второй ступени разделения цифровых сигналов введен приемник сигнала блокировки, вход которого объединен с входом блока разделения цифровых сигналов приемника сверхциклового синхронизма второй ступени разделения цифровых сигналов, а выход — с вторым входом накопителя приемника сверхциклового синхронизма.

Источники информации, принятые во внимание при экспертизе

1. Лопушнян Ю. Г. и др. Аппаратура вторичной ЦСП ИКМ вЂ” 120, «Электросвязь», 1977, № 12, (прототип). го