Стартстопное приемное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОВРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Социалистических

Республик ()843283 (61) Дополнительное к авт. свид-ву № 544170 (22) Заявлено 08.10.79 (21) 2827502/18-09 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 (51) М. Кл.

Н 04 L 17/16

Гааударетееиимй камитет (53) УДК 621.394..6 (088.8) ло делам изебретеиий и етирытий

Е. Н. Борисов, В. Г. Дорохов, Г. Т. Новиков, С. М. Перескоков,, С. М. Сидоренко и В. Б. Шумский, -т 1

В;, I (72) Авторы изобретения (71) Заявитель (54) СТАРТСТОПНОЕ ПРИЕМНОЕ УСТРОИСТВО!

Изобретение относится к телеграфии, и может использоваться для приема и регистрации телеграфных сообщений.

По основному авт. св. № 544170 известно стартстопное приемное устройство, содержащее входной блок, цикловой триггер, генератор тактовых импульсов, выход которого соединен с входом делителя частоты, элементы и блок дешифрации и печати, последовательно-параллельный преобразователь кода и элемент задержки, причем выход входного блока соединен с одним входом цик- 1О лового триггера непосредственно, а с другим входом — через последовательно соединенные последовательно-параллельный преобразователь кода и элемент задержки, выход циклового триггера соединен с соответствующими входами последовательно-параллельного преобразователя кода непосредственно и через делитель частоты, а информационные выходы последовательно-параллельного преобразователя кода соединены через элементы И с входами блока дешифрации и печати, причем другие входы элемента И 6 соединены с входом элемента задержки (1).

Однако известное устройство имеет недостаточную помехозащищенность.

Цель изобретения — повышение помехозащищенности.

Поставленная цель достигается тем, что в стартстопное приемное устройство, содержащее входной блок, цикловой триггер, генератор тактовых импульсов, выход которого соединен с входом делителя частоты, элементы И и блок дешифрации и печати, последовательно-параллельный преобразователь кода и элемент задержки, причем выход входного блока соединен с одним входом циклового триггера непосредственно, а с другим входом — через последовательно соединенные последовательно-параллельный преобразователь кода и элемент задержки, выход циклового триггера соединен с соот-,. ; ветствующими входами последовательно-= параллельного преобразователя кода непосредственно и через делитель частоты, а информационные выходы последовательнопараллельного преобразователя кода соединены через элемент И со входами блока дешифрации и печати, причем другие входы элементов И соединены с входом эл сита задержки, введены дополнительный элемент И, два элемента ИЛИ, счетчик, блок совпадения, стартовый триггер и дополни4 тивном случае — состояние «С». Состояние на выходе счетчика 9 соответствует значению посылки. С выхода делителя 4 импульс, соответствующий концу посылки, поступает на вход последовательно-параллельного преобразователя 7 и записывает в него соответствующее значение посылки в обратном коде, а также — на второй блок 13 совпадения. Если в момент прихода с выхода делителя 4 первого импульса на прямом выходе счетчика 9 — состояние «1» (т. е. стартовая посылка не принята), на первый вход блока 13 совпадения поступает разрешающий потенциал, ее выходной сигнал через второй элемент ИЛИ 15 устанавливает цикловой триггер 2 в нерабочее состояние. При этом запрещается работа делителя 4, последовательно-параллельного преобразователя 7, устанавливается в исходное состояние счетчик 9. Выходной сигнал с делителя 4 через элемент 11 задержки устанавливает в исходное состояние стартовый триггер 10 и через первый элемент ИЛИ 14 — счетчик 9. Если в момент прихода с выхода делителя 4 первого импульса на прямом выходе счетчика 9 — состояние «О», то блок 13 совпадения закрыт по первому входу и цикловой триггер 2 остается в рабочем состоянии. В последовательно-параллельный преобразователь 7 записываются посылки знака. Выходной сигнал с последовательно-параллельного преобразователя 7 через элемент 8 задержки и второй элемент ИЛИ 15 переводит цйкловой триггер

2 в нерабочее состояние, а также осуществляет выдачу знака в блок дешифрации и печати через элементы И 5.

Следовательно, предлагаемое приемное стартстопное устройство обеспечивает выделение каждого знака по стартстопному переходу, защиту от ложного запуска при длительности импульсных помех менее то/2, принятие решения о значении посылки методом интегрального приема. При этом посылка принимается правильно, если суммарная длительность помех в ее пределах менее

Формула изобретения

843283 тельный элемент задержки, причем выход входного блока блока через последовательно соединенные дополнительный элемент И и счетчик соединен с соответствующим входом последовательно-параллельного преобразователя кода, выход элемента задержки через первый элемент ИЛИ соединен сдру= гим входом циклового триггера, выход которого через стартовый триггер соединен с первым входом блока совпадения, второй и третий входы которого соединены соответственно с выходом делителя частоты и другим выходом счетчика, другой вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом циклового триггера, а второй вход — с выходом дополнительного элемента задержки, соединенного также с другим входом стартового триггера, вход дополнительного элемента задержки соединен с выходом делителя частоты, вход которого соединен с другим входом дополнительного элемента

И, при этом выход блока совпадения соединен с другим входом первого элемента ИЛИ.

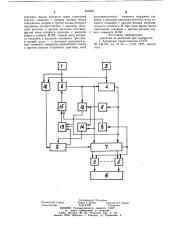

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит входной блок 1, цикловой триггер 2, генератор 3 тактовых импульсов, делитель 4 частоты, элементы

И 5, блок 6 дешифрации и печати, последовательно-параллельный преобразователь 7 кода, элемент 8 задержки, счетчик 9, стартовый триггер 10, дополнительный элемент 30

11 задержки, дополнительный элемент И 12, блок 13 совпадения и элементы ИЛИ 14 и 15.

Устройство работает следующим образом

Перед началом приема телеграфного сообщения цикловой триггер 2 находится в нерабочем состоянии и его выходной сигнал запрещает работу делителя 4 частоты, последовательно-параллельного преобразователя 7 кода и устанавливает в исходное состояние через первый элемент ИЛИ 14 счет- 40 чик 9. При поступлении перехода от стопа к старту из входного блока 1 цикловой триггер 2 переходит в рабочее состояние и его выходной сигнал разрешает работу делителя 4 частоты, последовательно-параллельного преобразователя 7, счетчика 9, а так- 4> же перебрасывает стартовый триггер 10 в единичное состояние, при этом на третий вход блока 13 совпадения поступает разрешающий потенциал. Счетчик 9 осуществляет счет импульсов, поступающих с элемента И 12, на входы которого поступают сигналы со входного блока 1 и генератора 3 тактовых импульсов. Частота генератора 3 тактовых импульсов равна f = -, гр — длительность посылкй; и — число целое. 55

Если на вход счетчика 9 поступает и/2 или более импульсов, то на его прямом выходе устанавливается состояние «1», в проСтартстопное приемное устройство по авт. св. № 544170, отличающееся тем, что, с целью повышения помехозащищенности, введены дополнительнь и элемент И, два элемента ИЛИ, счетчик, блок совпадения, стартовый триггер и дополнительный элемент задержки, причем выход входного блока через последовательно соединенные дополнительный элемент И и счетчик соединен с соответствующим входом последовательнопараллельного преобразователя кода, выход элемента задержки через первый элемент

ИЛИ соединен с другим входом циклового

843283

Составитель Е. Погиблов

Редактор Ю. Середа Техред А. Бойкас Корректор Е. Рошко

Заказ 5167 84 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, r. Ужгород, ул. Проектная, 4 триггера, выход которого через стартовый триггер соединен с первым входом блока совпадения, второй и третий входы которого соединены соответственно с выходом делителя частоты и другим выходом счетчика, другой вход которого соединен с выходом второго элемета ИЛИ., первый вход которого соединен с выходом циклового триггера, а второй вход — с выходом дополнительного элемента задержки, соединенного также с другим входом стартового триггера, вход дополнительного элемента задержки соединен с выходом делителя частоты, вход которого соединен с другим входом дополнительного элемента И, при этом выход блока совпадения соединен с другим входом первого элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР № 544170, кл. Н 04 1 17/16, 1975 (прототип) .