Устройство для выбора и идентификацииизмерительных каналов

Иллюстрации

Показать всеРеферат

Союз Советских

Ссщналнстнческих

Реслублик

ОП ИСАНИЕ ()843309

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 10.04.79 (21) 2750169/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

Н 04 („1 9/14

Гасударственный комитет

Опубликовано 30.06.81. Бюллетень № 24

Дата опубликования описания 05.07.81 (53) УДК 621 395. 632 (088.8) по делам нэебретеннй и еткрмтий (72) Автор изобретения

О. Г. Светников (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫБОРА И ИДЕНТИФИКАЦИИ

ИЗМЕРИТЕЛЬНЫХ КАНАЛОВ

Изобретение относится к радиотехнике и может использоваться для ввода телеметрической информации в системы обработки данных и в системы регистрации телеметрической информации.

Известно устройство для выбора и идентификации измерительных каналов, содержащее п узлов выделения каналов, содержащих последовательно соединенные регистр фазы, блок сравнения и счетчик адреса, вход которого соединен с входом регистра фазы,п регистров начального адреса, выходы которых соединены со вторыми входами соответствующих счетчиков адреса, выходы которых соединены с адресной шиной, соединенной с первым входом блока памяти, первый выход которого соединен со вторыми входами регистров фазы, причем вторые входы блоков сравнения соединены с выходами приемного блока (1).

Однако быстродействие известного устройстваа не вы соко.

Цель изобретения — повышение быстродействия.

Для этого в известное устройство для выбора и идентификаации измерительных каналов введены последовательно соединен2 ные блок пересчета фаз, формирователь номера низкоопросных каналов и сумматор, второй вход которого соединен со вторым выходом блока памяти, третий и четвертый выходы которого соединены соответственно с входом блока пересчета фаз и вторым входом формирователя номера низкоопросных каналов, второй выход которого соединен со вторым выходом блока памяти, третий вход которого соединен со вторым выходом блока пересчета фаз, причем выход сумматора соединен с адресной шиной.

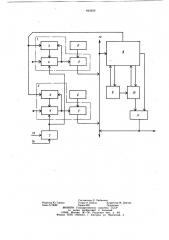

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство для выбора и идентификации измерительных каналов содержит и узлов

15 выделения каналов 1 и 2, каждый из которых содержит регистр 3 фазы, блок 4 сравнения, счетчик 5 адреса, устройство содержит также и регистров 6 начального адреса, приемный блок 7, блок 8 памяти, блок 9 пересчета фаз, формирователь 10 номера низкоопросных каналов, сумматор ll и адресную шину 12, причем приемный блок 7 имеет входы 13 и 14.

Устройство работает следующим образом.

843309

На вход 14 приемного блока 7 поступает маркер цикла, который устанавливает его в начальное состояние и разрешает дальнейшее функционирование устройства, а на вход

13 поступают канальные импульсы. На выходе приемного блока 7 формируется номер канального импульса в цикле, который поступает на входы блоков 4 узлов выделения каналов 1 и 2. При совпадении номера канального импульса с фазой, записанной в регистре 3, срабатывает соответствующий блок 4, формирующий сигнал сравнения, поступающий на входы регистра 3 и счетчика 5. В результате содержимое счетчика 5 по адресной шине 12 передается в блок 8, в котором по данному адресу выбирается управляющее слово первого типа, в состав которого входит фаза, определяющая местоположения канального импульса следующего измерительного канала данной частотной группы, идентификатор измерительного канала или адрес управляющего слова второго типа в зависимости от признака адреса и признака конца массива. Фаза записывается в регистр 3 того узла выделения каналов 1 и 2, в котором сработал блок 4 сравнения. Если признак адреса имеет нулевое значение, то идентификатор измерительного канала транс— лируется через сумматор 11 на выход устройства. Если признак адреса имеет единичное . значение, то осуществляется обращение в блок 8 памяти за управляющим. словом второго типа, путем передачи адреса управляющего слова второго типа, через сумматор 11 зо на адресную шину 12. Одновременно производится увеличение содержимого счетчика 5 на единицу, если признак конца массива имеет нулевое значение, или в счетчик 5 переписывается содержимое регистра 6, если признак конца массива имеет единичное зна- З5 чение.

Управляющее слово второго типа передается в блок 9, формирователь 10 и сумматор 11.

Признаки выделения низкоопросных ка- 4п налов задаются кодом. Каждому разряду кода соответствует измерительный канал, опросность которого в К раз ниже, чем опросность каналов, выделяемых соответствующим узлом выделения каналов 1 и 2. Если в данной позиции установлена единица, то 4 соответствующий низкоопросный канал выбирается. В блоке 9 осуществляется формирование кода текущей фазы низкоопросных каналов, который поступает в формирователь !О, где устанавливается соответствие между кодом текущей фазы и выделяемым низкоопросным измерительным каналом. Если низкоопросный канал выделяется, то формируется его порядковый номер, который в сумматоре 11 складывается с базовым идентификатором. В результате на выход поступает идентификатор низкоопросного канала, который не совпадает ни с одним из других идентификаторов выделяемых каналов разной опросности.

Работа устройства повторяется каждый раз с приходом канального импульса на вход 13.

Применение предлагаемого устройства позволяет увеличить количество выделяемых и идентифицируемых измерительных каналов и повысить быстродействие устройств.

Формула изобретения

Устройство для выбора и идентификации измерительных каналов, содержащее п узлов выделения каналов, содержащих последовательно соединенные регистр фазы, блок сравнения и счетчик адреса, вход которого соединен с входом регистра фазы, и регистров начального адреса, выходы которых соединены со вторыми входами соответствующих счетчиков адреса выходы которых соединены с адресной шиной, соединенной с первым входом блока памяти, первый выход которого соединен со вторыми входами регистров фазы, причем вторые входы блоков сравнения соединены с выходами приемного блока, отличающееся тем, что, с целью повышения быстродействия, введены последовательно соединенные блок пересчета фаз, формирователь номера низкоопросных каналов и сумматор, второй вход которого соединен со вторым выходом блока памяти, третий и четвертый выходы которого соединены соответственно со входом блока пересчета фаз и вторым входом формирователя номера низкоопросных каналов, второй выход которого соединен со вторым входом блока памяти, третий вход которого соединен со вторым выходом блока пересчета фаз, причем выход сумматора соединен с адресной шиной.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 559465, кл. Н 04 Q 9/14, 1975.

843309

Редактор Ю. Середа

Заказ 5178/86

Составитель Е. Любимова

Техред А. Бойкас Корректор М. Демчик

Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4