Двойной балансный смеситель

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТИЙЬСТВУ

<11845263. (б1) Дополнительное к авт. сеид-ву (22) Заявлено 220377 (21) 2467385/18-09 с присоединением заявки М (23) Приоритвт

Опубликовано 07,0781. оюллетеиь N9 25, Дата опубликования описания 070781 (51)М. Кл з

Н 03 0 7/14

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 372; .622(088.8) (72) Автор изобретения

A.A. Биленко (71) Заявитель (54) ДВОИНОЙ БЛЛЛНСНЫЙ СМЕСИТЕЛЬ

Изобретение относится к радиотех-т нике, предназначено для преобразования частоты с одной несущей на другую может быть использовано в радиоприемных устройствах СВЧ.

Известен двойной балансный смеситель, состоящий из входных гибридных соединений (сумматоров и делителей мощностиУ н четырех диодов f1J.

Недостатком этого смесителя является невысокий коэффициент трансформации импедансов у входных гибридов, что затрудняет согласование последних с диодами, а пересечение линий передачи, соединяющих диоды с гибри- 15 дами, приводит к значительным трудностям в конструировании таких смесителей в СВЧ диапазоне.

Наиболее близок к предлагаемому двойной балансный смеситель, содер- 26 жащий синфаэно-противофаэный делитель с двумя входами, четыре диода, включенных по мостовой схеме, и выхо ной с ато у 4 р

25 . С помощью синфазно-противофазного делителя и выходного сумматора в известном устройстве обеспечивается подача на диоды напряжений сигнала и гетеродина с определенными фазами Щ и выделение сигнала промежуточной частоты (21. Для обеспечения необходимых фазовых соотношений на диодах их включают по мостовой схеме, что требует пересечения линий передач, соединяющих диоды с гибридами.

Такое включение приводит к параэитному влиянию одного диода на дру1 гой и возникновению комбинационных составляющих на выходе смесителя.

Целью изобретения является улучшение подавления комбинационных составляющих на выходе смесителя в широкой полосе частот.

Для этого в двОйной балансный смеситель, содержащий,синфаэно-противофазный делитель мощности с двумя входами, первый вход которого подключен к сдной из входных клемм смесителя, четыре диода и выходной сумматор, введены два противофазных делителя мощности, выходы которых соответственно соединены через диоды, включенные в одном направлении, с входами первого и второго синфазных сумматоров мощности, причем выходной сумматор выполней противофазным, входы первого и второго протнвофазных делителей подключены соответ;-.твенно к синфазному

845263 и противофазному выходам синфаэнопротивофазного делителя, второй вход" которого соединен с другой входной клеммой смесителя, выходы первого и второго синфаэных сумматоров подклю- . чены соответственно к синфазному и противофаэному входам выходного сумматора.

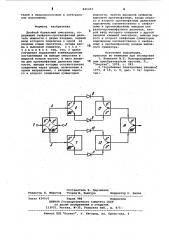

На чертеже представлена блок-схема йредлагаемого двойного. балансного смесителя.

Двойной балансный смеситель содержит синфаэно-противофаэный делитель 1 с входами 2 и 3, синфазным 4 и противофазным 5 выходами, противофазные делители б и 7, диоды 8-11, синфазные сумматоры 12 и 13, выходной сумма- 15 тор 14.

8 9

Оо 180 оо

О 1В0" 18 О" 0 с г

Здесь Ч вЂ” фаза напря>кения сигнала;

V< — фаза напряжения гетеродина.

Известно, что вольт-амперная характерису ика.смесительного диода мо>кет описываться рядом:

ig =ао+а. е,+а, е + (1) где i — ток диода;, ао, а„, а ..., - постоянные ко- 35 эффициенты; е — напряжение на диоде.

К Ыа>кдому.диоду прикладывается по два напряжения входных сигналов с различными фазами, и суммарное напря>кение еа на каждом диоде

40 е - — "je сов(ау - )+e cos(uu„t+ vÄ)j, где е - е — амплитуды входных напряжес ний сигнала и гетеродина. 45

С учетом фаз Ч и Ч„, приведенных в таблице, напряжения на диодах 8-11:

50 (2) i„4=2 ce„cosu>ct- cos u Äa i... =е,е асов(а -ю„)ь+

55 +cos (uuc+uu )a)+

Подставив напря>кения иэ (2) в (1), получим значения токов соответственно для каждого диода:

ДВ=аО -"(Р СОЗ(ЮС +Е„СОЭЮ„ )+ 4 (Е,сОЭ uu t+

+2å Е созе - соэси,. +е .соРю„Е)+..

1,>в=аΠ— (-Е COS uuct- Е,.СОЭЫ> t)i<(e cOS + б0

à = — "(e cosuu +e cosuurt)

Е = (-е cosuu <-е cosuu„t) е „о= " (е, cos uu t - e„cos uu 4) е =- (-е cosuu t+e соэм t)

Д 1

Напря>кения сигнала и гетеродина подаются на входы 2 и 3 делителя 1, причем безразлично, какое из них подается на вход 1, а какое — на вход 2.

Один из этих входов (например, 2)) делит входной сигнал синфаэно, а другой — противофазно. Пусть для определенности сигнал подается на синфаэный вход 2, а гетеродин - на противофазный вход 3

В результате этого напряжение сигнала подается на противофазные делители б и 7 с одинаковыми фазами, а напряжение гетеродина — с противоположными. После противофазного деления в делителях б и 7 эти напряжения поступают на диоды с относительными фазами, приведенными в таблице. — .+ 2е,e„cosuuct cosuurt. е1cos ш,ь) ... а1 2

1 =co — (e cosu>e- e,cosuu„t>4(eicos ñþ t— 2е е,соэ о у cos ю,. +е cgs>u>rt)+... (>) а„ а

1 „„= ко+ — (- eicos uu tie„cosa,цi — д(РсоР. t с

- 2 Р е „сов а . co< м,t+e„cos uu,t)+., Так как сумматоры 12 и 13 синфазные, а сумматор 14 — противофазный, то токи !*в, складываются синфазно, токи iAao и i* синфазно, а токи (i s+ i> ) и (i*„+ i ) — противофаэно.

Отсюда: п4 = Ае+ )да дно -4А„„, (4) где i — ток промежуточной частоты

114 на выходе 15 сумматора 14.

Подставив в (4) значения токов из (3), получим

Предложенный. двойной балансный смеситель имеет лучшее согласование в широкой полосе частот, более широкую полосу рабочих частот. В предложенном смесителе устранено пересе- чение линий передачи, соединяющих диоды с гибридами, в результате чего появляется возможность практической реализации двойных балансных смеси845263

Формула изобретения

Составитель Б. Дарчинянц

Редактор Б. Федотов Техред М, Коштура Еорректор О. Билак

Заказ 4209/6 Тирам 988 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 телей в микрополосковом и интегральном исполнении.

Двойной балансный смеситель, содержащий синфаэно-противофаэный делитель мощности с двумя входами, первый вход которого подключен к одной из входных клемм смесителя, .четыре диода и выходной сумматор, о т л ич а ю шийся тем, что, с целью улучшения подавления комбинационных составляющих на выходе смесителя в широкой полосе частот, в него введены два противофазных делителя мощности, выходы. которых соответственно соединены через диоды, включенные в одном направлении, с входами первого и второго синфазных сумматоров мощности, причем выходной сумматор выполнен противофаэным, входы первого и второго противофаэных делителей подключены соответственно к синфаэному И противофаэному выходам син фазно-противофазного делителя, второй вход которого соединен с другой входной клеммой смесителя, выходы первого и второго синфазных сумматоров подключены соответственно к синфазному и противофаэному входам выходного сумматора. !

Источники информации, принятые во внимание при экспертизе

1. Мовшович М.Е. Полупроводнико"

t5 вые преобразователи частоты, Л., "Энергия", 1974, с. 245.

2."Зарубежная электронная техника, 1975, Р 19, с. 6, рис. 1 (в) (прототип).