Устройство сравнения

Иллюстрации

Показать всеРеферат

Союз Советских

Социапнстичесних

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТЕЛЬСТВУ

<»845277 (61) Дополнительное к авт. свид-ву— (22) Заявлено 030439 (21) 2745501/18-21

Р1,,(„з

Н 03 К 5/22

G 05 В 1/01 с присоединением заявки М

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет (53) УДК 621. 374. .5 (088.8) Опубликовано 070781.Бюллетень Йо 25

Дата опубликования описания 070781 (54) УСТРОЙСТВО СРАВНЕНИЯ

Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях, пороговых устройствах обнаружения сиг- 5 налов, дискретных следящих систем.

Известен компаратор АМ685, содержащий два дифференциальных усилителя, стробируе лый триггер, выходной эмиттерный повторитель t13. Этот компаратор обладает недостаточно высокой динамической чувствительностью.

Известно также Устройство сравнения, содержащее дифференциальный усилитель, прямой выход которого через усилитель-инвертор соединен с RS-триг-15 гером f 2) .

Целью изобретения является повыаение динамической чувствительности устройства сравнения.

Для достижения этого в устройство сравнения, содержащее дифференциальный усилитель, прямой выход которого через усилитель-инвертор соединен с RS-триггером, введены переходная

RC-цепь, вентиль, резистор и накопительный конденсатор, причем между инверсным выходом дифференциального усилителя и дополнительным S-входом

RS-триггера через переходную RC-цепь включен вентиль, дополнительный вход ЗО

RS-триггера соединен через резистор с источником питания и через накопительный конденсатор с общей шиной.

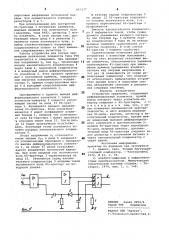

На чертеже представлена функциональная схема устройства сравнения. .Устройство сравнения содержит последовательно включенные дифференциальный усилитель 1, усилитель-инвертор 2, RS-триггер 3. Между инверсным выходом дифференциального усилителя

1 и дополнительным входом 52 RS-триггера 3 через переходную RC-цепь, конденсатор 4 и резистор 5 включен вентиль-диод 6, кроме того, дополнительный вход 52 соединен через резистор

7 с источнйком питания 8 и через накопительный конденсатор 9 — с общей шиной.

При входном напряжении U> меньшим

Уоо на прямом выходе дифференциально го усилителя 1 действует низкий уровень напряжения, а на выходе усилителя-инвертора 2 — высокий, близкий к уровню логической единицы RS-триггера 3. С помощью сигнала "Уст 0" RSтриггер 3 предварительно установлен в исходное (нулевое) состояние. Через диод б и резистор-5 протекает ток, создающий на входе S2 RS-триггера 3 напряжение, несколько превосходящее

845277

КИПИ Заказ 4209/б раж 988 Подписное пороговое напряжение логической единицы. Это осуществляется подбором резисторов 5 и 7.

При использовании для построения

RS-триггера 3 логических элементов, имеющих входной ток логического нуля (например, типа ТТЛ), резистор 7 мож.но исключить. В этом случае ток, протекающий через диод б и резистор 5, является током логического нуля, а выбор соответствующего напряжения осуществляется только за счет изменения сопротивления резистора 5.

Работа устройства для случая применения логических элементов типа ТТЛ заключается в следующем. При превышении напряжения U> над Uo происходит 15 разряд накопительного конденсатора 9 через диод б, переходной конденсатор

4 и инверсный выход дифференциального усилителя 1. Этот процесс происходит с постоянной времени, определяе- 2О мой емкостью наквпительного конденсатора 9, прямым сопротивлением диода б и выходным сопротивлением дифференциального усилителя 1.

Одновременно с прямого выхода дифференциального усилителя 1 через усилитель-инвертор 2 подается управляющий сигнал на вход 51 RS-Tp rгера 3. Начинается процесс переключения RS-т >иггера. Если усилительинвертор 2 имеет коэффициент усиления больше 1, входной ток логического нуля RS-триггера 3 будет протекать в основном через вход 51. Ток по входу 52 будет практически отсутство- 3S вать. Благодаря этому улучшаются условия разряда накопительного конденсатора 9.

Когда напряжение U>; становится вновь меньше Ор„ и диод б закрывает- 40 ся положительным перепадом с инверсного выхода дифференциального усилителя 1, на входе S7 вновь устанавливается напряжение логической единицы. При этом входной ток логического нуля, RS-триггера 3 переключается на вход 52. Начинается заряд накопительного конденсатора 9 входным током логического нуля RS-триггер,". до исходного уровня.

В течение заряда конденсатора 9 на входе S2 RS-триггера сохраняется условие логического нуля, т.е. процесс переключения RS-триггера 3 продолжается.

Емкость накопительного конденсатора 9 выбирается такой, чтобы сумма времени превышения входного сигнала

U над опорным 0оп и времени заряда конденсатора 9 была бы не леньше времени задержки срабатывания устройства сравнения. В этом случае

RS-триггер 3 надежно сработает.

Сравнительные испытания данного устройства с известным показывают, что за счет включения указанных выше .элементов, обеспечивается надежное срабатывание RS-триггера при уменьшении времени превышения входного сигнала над опорным напря>кением в

3-6 раз (в зависимости от серии используемых элементов) . Это позволяет использовать предлагаемое устройство прежде всего в пороговых схемах обнаружения сигналов и дискретных следящих системах.

Формула изобретения

Устройство сравнения, содержащее дифференциальный усилитель, прямой выход которого через усилитель-инвертор соединен с RS-триггером, о тл и ч а ю щ е е с я тем, что, с целью повышения динамической чувствительности, в него введены переходная RC-цепь, вентиль, резистор и накопительный конденсатор, причем между инверсным выходом дифференциального усилителя и дополнительным Sвходом RS-триггера через переходную

RC-цепь включен вентиль, дополнительный вход RS-триггера соединен через резистор с источником питания и через накопительный конденсатор с общей шиной.

Источники информации, принятые во внимание при экспертизе

1. Джейлз, Силз. Точный быстродействующий компаратор. †"Электроника", 1972, Р 21, с. 59.

2. Аналого-цифровые и цифроаналоговые преобразователи. Межвузовский тематический научный сборнйк. — Таганрог, 1974, вып. 1, с. 168. илиал ППП "Патент", ".Óæãîpoä,óë.ÏðîåêòíàR,4