Делитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТВЛЬСТВУ

< я845291 (61) Дополнительное к авт. саид-ау(22) Заявлено 160779 (21) 2796169/18-21 с присоединением заявки Йо— (23) Приоритет—

Опубликовано 070781. Бюллетень N9 25 (5!)М. Кл.з

Н 03 К 23/02

Государственный комитет

СССР по делам изобретений и открытий (33) УДК 621. 374. .4(088.8) Дата опубликования описания 0 70781 (72) Авторы изобретения

В.C. мочалов, В.Л. Лысенко и В.Я. Колесников .):у,: . тг;т,. (71) Заявитель (54) ДЕЛИТЕЛЬ ЧДСТОТЦ

Изобретение относится к автомати-, ке н вычислительной технике и может быть использовано в устройствах, где необходимо деление частоты импульсов на 7,5 и на 15. 5

Известны делители частоты, каждый разряд которых содержит триггеры памяти, коммутационные триггеры и схемы

И-НЕ.

Известно устройство, содержащее разряды, каждый иэ которых состоит из триггера памяти и коммутационного триггера, и элементы И-HE 111.

Наиболее близким к изобретению является устройство, содержащее эле- 15 мент И-НЕ и четыре разряда, каждый из которых состоит иэ триггера памяти .и двух коммутационных триггеров, причем в каждом разряде к единичному входу первого коммутационного тригге- 20 ра и к нулевому входу второго подключена входная шина, единичный выход первого коммутационного триггера соединен с нулевыми входами триггера памяти и второго коммутационного тригге-!5 ра, нулевой выход которого подключен к единичному входу триггера памяти, единичный вход — к единичному выходу триггера памяти, а единичный выход — к нулевому входу первого ком- 30 мутационного триггера, при этом нулевой выход первого коммутационного триггера первого разряда соединен с нулевым и единичным входагли второго коммутационного триггера второго разряда, нулевой выход первого коммутационного триггера второго разряда — с нулевым и единичным входом второго коммутационного триггера третьего разряда, а нулевой выход первого коммутационного триггера третьего разряда — с нулевым входогл второго коммутационного триггера четвертого разряда, причем единичный, выходы первого и второго коммутационных триггеров четвертого разряда подключены к нулевым входам втордго коммутационного триггера первого разряда, а входы схемы И-НЕ соединены с нулевым выходом второго коммутационного триггера третьего разряда и с единичным выходом второго коммутационного триггера четвертого разряда (2f.

Однако известное устройство не позволяет делить частоту импульсов на

7,5 и на 15 °

Целью изобретения является расширение функциональных возможностей устройства.

845291

Достигается это тем, что в делитель частоты, содержащий элемент

И-HE и четыре разряда, каждый из которых состоит из триггера памяти и двух коммутационных триггеров, причем в каждом разряде к единичному входу первого коммутационного триггера и к нулевому входу второго подлючена входная шина, единичный выход первого коммутационного триггера соединен с нулевыми входами триггера памяти и второго коммутационно- 1О го триггера, нулевой выход которого подключен к единичному входу триггера памяти, единичный вход — к единичному выходу триггера памяти, а единичный выход к нулевому входу первого коммутационного триггера, при этом нулевой выход первого коммутационного триггера первого разряда соединен с нулевым и единичным входами второго коммутационного триггера второго разряда, нулевой выход rервого коммутационного триггера второго разряда — с нулевым и единичным входами второго коммутационного триггера третьего разряда, а нулевой выход первого коммутационного триггера

25 третьего разряда — с нулевым входом второго коммутационного триггера четвертого разряда, введен второй элемент И-HL, причем первые три входа первого элемента И-HE соединены с со- 30 ответствующими единичными выходами триггеров памяти второго, третьего и четвертого разрядов, а четвертый вход первого элемента И-НŠ— с нулевым выходом первого коммутационного 3 триггера первого разряда, выход первого элемента И-НЕ соединен с одним из входов второго элемента И-НЕ, а также с второй выходной шиной и с единичным входом первого коммутационного триггера первого разряда, при этом второй вход второго элемента И-НЕ, выход которого соединен с первой выходной шиной, соединен с нулевым выходом второго коммутационного триггера четвертого разряда, а единичный выход первого коммутационного триггера четвертого разряда соединен с единичным входом первого коммутационного триггера первого разряда. 5Î

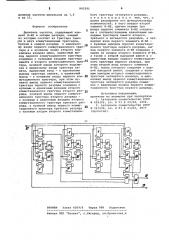

На чертеже представлена схема делителя частоты.

Устройство содержит коммутационные триггеры на элементах И-НЕ 1-16, 55 триггеры памяти на элементах И-НЕ

17-24, первый элемент И-HE 25, второй элемент : -НЕ 26, входную шину 27, первую выходную шину 28, вторую выходную шину 29.

Устройство работает следующим образом

В исходном состоянии триггер памяти первого разряда находится в единичном состоянии, а триггеры памяти остальных разрядов — в нулевом состоянии.

Под действием входного сигнала в счетчике осуществляется обычный пересчет поступающих импульсов в двоичном коде.

При этом осуществляется следующая последовательность схемы состояний триггеров памяти.

0 0001

1 0010

2 0011

3 0100

4 0101

5 0110

6 0111

7 1000

8 1001 °

9 1010

10 1011

11 1100

12 1101

13 1110

14 1111

15 0001

Из этого следует, что с приходом седьмого по счету входного импульса на выходе элемента И-HE 15 появляется сигнал, равный логическому нулю, который устанавливает триггер памяти четвертого разряда в единичное состояние и который через элемент

И-HE 26 поступает на первую выходную шину 28 устройства. Далее осуществляется обычный пересчет входных импульсов, и с приходом четырнадцатого импульса в счетчике устанавливается код 1111. После окончания действия четырнадцатого импульса на выходе элемента И-HE 1 появляется сигнал, равный логической единице, который открывает элемент И-HE 25. Сигнал, равный логическому нулю, с выхода элемента И-HE 25 одновременно поступает на вход элемента И-НЕ 2, на вторую выходную шину 29 устройства и через элемент И-НЕ 26 — на первую выходную шину 28 устройства.

С приходом пятнадцатого входного импульса откроются элементы И-НЕ 6, 10 и 14, в результате чего триггеры памяти соответственно второго, третьего и четвертого разрядов установятся в нулевое состояние, элемент И-НЕ

25 закрывается и прекращается формирование выходных сигналов. Триггер памяти первого разряда не меняет своего состояния, поскольку элемент И-НЕ

2 сначала закрыт сигналом, равным логическому нулю с выхода элемента И-НЕ

25, а затем сигналом с выхода элемента И-HE 14. После окончания действия пятнадцатого импульса схема возвращается в исходное состояние 0001.

Таким образом, на 15 входных импульсов схема выдает два импульса на первую выходную шину 28 устройства и один импульс на вторую выходную шину 29 устройства, T..å. происходит

845291

ВНИИПИ Заказ 4209/б Тираж 988 Подписное

Филиал ППП "Патент", г.ужгород, ул.Проектная,4 (. деление частоты импульсов на 7,5 и на 15.

Формула изобретения

Делитель частоты, содержащий элемент И-НЕ и четыре разряда, каждый из которых состоит из триггера памя-! ти и двух коммутационных триггеров, причем в каждом разряде к единичному входу первого коммутационного триггера и к нулевому входу второго подключена входная шина, единичный выход первого коммутационного триггера соединен с нулевыми входами триггера памяти и второго коммутационного триг-" гера, нулевой выход которого подключен к единичному входу триггера памяти, единичный вход — к единичному выходу триггера памяти, а единичный выход — к нулевому входу первого ком- 20 мутационного триггера, при этом нулевой выход первого коммутационного триггера первого разряда соединен с нулевым и единичным входами второго коммутационного триггера второго раз- yg ряда, нулевой выход первого коммутационного триггера второго разряда— с нулевым и .единичным входами второго коммутационного триггера третьего раз- ряда, а нулевой выход первого коммутационного триггера третьего разряда с нулевым входом второго коммутационного триггера четвертого разряда, отличающийся тем, что, с целью расширения его функциональных возможностей, в него введен второй элемент И-НЕ, причем первые три входа первого элемента И-НЕ соединены с соответствующими единичными выходами триггеров памяти второго, третьего и четвертого разрядов, а четвертый вход первого элемента И-НЕ— с нулевым выходом первого коммутационного триггера первого разряда, выход первого элемента И-НЕ соединен с одним из входов второго элемента И-НЕ, а также с второй выходной шиной и с единичным входом первого коммутационного триггера первого разряда, при этом второй вход второго элемента

И-НЕ, выход которого соединен с первой выходной шиной, соединен с нулевым выходом второго коммутационного триггера четвертого разряда, а единичный выход первого коммутационного триггера четвертого разряда соединен с единичным входом первого коммутационного триггера первого разряда.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 42б326, кл. Н 03 К 23/24„ 1972.

2. Авторское свидетельство СССР

9 561299, кл. Н 03 К 23/02, 1977 (прототип).