Преобразователь двоичного кода вдвоично-десятичный

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик по 847318 (63) Дополнительное к авт, свид-sy (22) Заявлено 26. 02. 79 (21) 2729173/18-24 (51)М. Кл.з С ПРИСОЕДИНЕНИЕМ ЗаЯВКИ Hо

G 06 F 5/02

Государственный комитет

CCC P по делам изобретений и открытий (23) Приоритет

Опубликовано 150781. Бюллетень No 26 (53) УДК 681. 325 (088.8) Дата опубликования описания 15. 07. 81 (72) Автор изобретения

А.П. Алексеев (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах вывода информации в ЦВМ.

Известен преобразователь двоичного кода в двоично-десятичный,содержащий двоично-десятичный сумматор, дешифратор, декадный счетчик пере полнений, блоки управления и поразрядного умножения, коммутатор lip .

Недостаток данного устройства состоит в сложности управления и низком быстродействии.

Наиболее близким к предлагаемому по технической сущности является преобразователь двоичного кода в двоично-десятичный, содержащий блок управления, вычитанием, тактирующий вход которого соединен с шиной тактовых импульсов, блок формирования управляющих сигналов, установочный вход которого соединен с шиной начала преобразования, входы номера десятичного разряда блока формирования управляющих сигналов соединены с вы.ходами блока управления вычитанием, а выходы соединены со входами номера десятичного разряда блока управления вычитанием, блок анализа знака, вход опроса которого соединен с выходом сигнала продолжения преобразования блока формирования управляющих сигналов, счетчик, группа элементов И и статический регистр, входы которого соединены с выходами группы элементов И, первые входы которых соединены с выходами счетчика, а вторые входы группы элементов

И соединены с выходами блока управления вычитанием, вход счетчика соединен с выходом положительного знака блока анализа знака, выход отрицательного знака которого соединен со входом изменения номера десятичного

15 разряда блока управления вычитанием (2Д.

Недостаток данного преобразователя двоичного кода в двоично-десятичный состоит в том, что кон- .

20 станты вычитания порядков определяются при условии равенства младшего разряда преобразуемого кода еди.. нице. При этом отсутствует возможность преобразования кода с учетом любого заданного коэффициента масштабирования, определяемого ценой младшего разряда, что ограничивает диапазон применяемости устройства.

В накапливающем сумматоре происхоЗО дит восстановление отрицательных

847318 остатков, которое усложняет управление сумматором и понижает быстродействие преобразователя.

Цель изобретения — повышение быстродействия и расширение функциональных воэможностей, заключающихся в преобразовании кода с заданным коэффициентом масштабирования.

Поставленная цель достигается тем, что в преобразователь двоичного кода .в двоично-десятичный, содержащий блок управления вычитанием, тактирующий вход которого соединен с шиной тактовых импульсов, блок формирования управляющих сигналов, установочный вход которого соединен с шиной начала преобразования, входы номера, десятичного разряда блока формирования управляющих сигналов соединены с выходами блока управления вычитанием, а выходы соединены со входами номера десятичного разряда блока управления вычитанием, блок анализа знака, вход опроса которого соединен с выходом сигнала продолжения преобразования блока формирования управляющих сигналов, счетчик, группу элементов И и статический регистр, входы которого соединены с выходами группы элементов И, первые входы которых соединены с выходами счетчика, а вторые входы группы элементов И соединены с выходами блока управления вычитанием, вход счетчика соединен с выходом положительного знака блока анализа знака, выход отрицательного знака которого соединен со входом изменения номера десятичного разряда блока управления вычитанием, введены регистр масштабного коэффициента, блок формирования масштабируемых двоичных эквивалентов, комбинационный сумматор и регистр остатка, информационные входы которого соединены с. выходами комбинационного сумматора, вход разрешения записи которого соединен с выходом положительного знака блока анализа знака, а выходы регистра остатка соединены с первой группой входов комбинационного сумматора, вторая группа входов которого соединена с выходами блока масштабируемых двоичных эквивалентов, а знаковый выход комбинационного сумматора соединен со знаковым входом блока анализа знака, выходы регистра масштабного коэффициента соединены со входами масштабирования блока масштаби руемых двоичных эквивалентов, входы номера десятичного разряда которого соединены с выходами блока формирования управляющих сигналов.

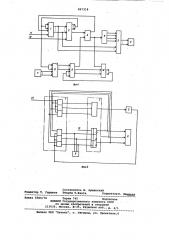

На фиг. 1 и 2 представлен предлагаемый преобразователь двоичного кода в двоично-десятичный.

Преобразователь содержит блок 1 управления вычитанием, выходы которого соединены со входами блока 2 формирования управляющих сигналов, Временная диаграмма работы преобразователя определяется импульсами, З0 поступающими с шины 11 тактовых импульсов, соединенной с одноименным входом блока 1 управления вычитанием, и с шиной 12 начала преобразования (12), соединенной с одноименным входом блока 2 формирования управляющих сигналов.

Блок 8 масштабируемых двоичных эквивалентов формирует константы, 40

-10

1 Р

Я

И блок 3 анализа знака, выход отрицательного знака которого соединен со входом блока 1 управления вычитанием, а выход положительного знака соединен со счетным входом счетчика, выходы которого через группу элементов И соединены со входами соответствующих тетрад статического регистра б, регистр 7 масштабного коэффициента, выходы которого через блок 8 формирования масштабируемых двоичных эквивалентов соединены со входами первого слагаемого комбинационного сумматора 9, а выходы комбинационного сумматора 9 через регистр 10 остатка, запись которого осуществляется по заднему фронту импульса записи, соединены со входами второго слагаемого комбинационного сумматора 9, знаковый выход которого соединен с первым входом блока 3 анализа знака числа, а второй вход блока 3 анализа знака числа соединен с одним из выходов блока 2 формирования управляющих сигналов, другие выходы соединены со входами блока 1 управления вычитанием и другими входами блока 8 масштабируемых двоичных эквивалентов. величина которых огределяется по формуле где р = О, 1 1, + 2, ° .. — порядок преобразуемого числа; m — масштабный коэффициент, вводимый через регистр

7 масштабного коэффициента. Блок 8 масштабируемых двоичных эквивалентов содержит й+К разрядов, причем и — разряды формируют целую часть константы, а К вЂ” разряды - дробную.

Количество N — разрядов соответствует разрядности преобразуемого кода, а

K — разрядов — точности набора дробной части константы.

Преобразователь работает следующим образом.

В N — - разряды регистра 10 остатка вводится преобразуемое число. С приходом сигнала на шину "Начало преобразования" на одном из выходов блока 2 формирования управляющих сигналов появляется сигнал, который в зависимости от масштабного коэффициента посредством блока 8 формирования масштабируемых двоичных эквивалентов формирует в дополнительном

847318 коде, позволяющим операцию вычитания заменить операцией сложения, константу старшего порядка, которая вводится в комбинационный сумматор

9. Если знак остатка комбинационного сумматора 9 положительный, то тактовый импульс с одноименной шины

11, через блок 1 управления вычита- нием, блок 2 формирования управляющих сигналов, блок 3 анализа знака числа поступает на вход четырехразрядного двоичного счетчика 4 и вход записи регистра 10 остатка. В четырехраэрядный двоичный счетчик 4 записывается единица, а в регистр 10 остатка— содержимое комбинационного сумматора 9, при этом на выходе комбинационного сумматора 9 формируется новый остаток, и если его знак положительный, то процесс повторяется.

Если знак остатка комбинационного сумматора 9 отрицательный, то такто- 20 вый импульс, с выхода блока 3 анализа знака числа через блок 1 управления вычитанием, поступает на вход блока 2 формирования управляющих сигналов, который вырабатывает для блока 8 формирования масштабируемых двоичных эквивалентов сигнал формирования константы следующего порядка (на единицу меньшего). Одновременно тактовый импульс, с соответствующего выхода блока 1 .управления вычитанием через соответствующую группу элементов И 5, записывает в тетраду старшего порядка статического регистра 6 содержимое четырехразрядного двоичного счетчика 4, Процесс, аналогичный описанному, повторяется до тех пор, пока из четырехраэрядного двоичного счетчика 4 не будет передан результат, характеризующий младший порядок преобразуемого двоичного 40 кода.

Использование изобретения позволяет осуществлять непосредственный цифровой контроль за аналоговыми величинами, оцифровка которых произво- 4 дится устройствами, имеющими определенные величины масштабных коэффициентов °

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий блок управления вычитанием, тактирующий вход которого соединен с шиной тактовых импульсов, блок формирования управляющих сигналов, установочный вход которого соединен с шиной начала преобразования, входы номера десятичного разряда блока формирования управляющих сигналов соединены с выходами блока управления вычитанием, а выходы соединены со входами номера десятичного разряда блока управления вычитанием, блок анализа знака, вход опроса которого соединен с выходом сигнала продолжения преобраЗования блока формирования управляющих сигналов, счетчик, группу элементов И и статический регистр, входы которого соединены с выходами группы элементов И, первые входы которых соединены с выходами счетчика, а вторые входы группы элементов И соединены с выходами блока управления вычитанием, вход счетчика соединен с выходом положительного знака блока анализа знака, выход отрицательного знака которого соединен со входом изменения номера десятичного разряда блока управления вычитанием, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и расширения функциональных воэможностей, заключающихся в преобразовании кода с заданным коэффициентом масштабирования, в него введены регистр масштабного коэффициента, блок формирования масштабируемых двоичных эквивалентов, комбинационный сумматор и регистр остатка, информационные входы которого соединены-с выходами комбинационного сумматора, вход разрешения записи которого соединен с выходом положительного знака блока анализа знака, а выходы регистра остатка соединены с первой группой входов комбинационного сумматора, вторая группа входов которого соединена с. выходами блока масштабируемых двоичных эквивалентов, а знаковый выход комбинационного сумматора соединен со знаковым входом блока анализа знака, выходы регистра масштабного коэффициента соединены со входами масштабирования блока масштабируемых двоичных эквивалентов, входы номера десятичного разряда которого соединен с выходами блока формирования управляющих сигналов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 525945 кл. G 06 F 5/02, 1974.

2. Авторское свидетельство СССР

Р 437069, кл. G 06 F 5/02, 1972 (прототип).

847318 фиа1

qual

Составитель М. варшавский

Редактор Т. Гыршкан Техред 3.фанта, КорректорН. Швед

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5500/76

;I филиал ППП "Патент", r. ужгород, ул. Проектная,4