Устройство для логарифмированиямассивов двоичных чисел

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Ф

«

К АВТОРСКОМУ СВИ ИТИЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 30.11. 79 (21) 2862892/18-24 (51)Hl Л. с присоединением заявки 89

G 06 F 7/556

Государственный комитет

СССР по делам изобретений н открытий

{23) Приоритет

Опубликовано 150781. Бюллетень Йй 26

Дата опубликования описания 15 ° 07. 81 (53) УДК 681. 3 (088.8) (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ

МАССИВОВ ДВОИЧННХ ЧИСЕЛ

2сэ 6+ 2t +

Изобретение относится к вычислительной технике и предназначено для использования в универсальных и специализированных ЦВМ при обработке больших массивов информации.

Известно устройство для вычисления логарифма числа электрических импульсов, содержащее счетчик вычисления мантиссы и характеристики, регистры сдвига и памяти на триггерах, ключи, одновибратор, матричную схему определения поправок и распределитель импульсов Г1).

Однако данное устройство имеет низкое быстродействие.

Наиболее близким к предлагаемому является устройство, содержащее входной регистр, три блока памяти, блок синхронизации, первый сумматор и выходной регистр, вход которого соединен с выходом первого сумматора, первый вход которого соединен с выходом первого блока памяти, первый и второй выходы блока синхронизации соединены с управляющими входами входного и выходного регистров,коммутатор, триггер, двигатель и блок управления двигателем. 30

Быстродействие устройства не превышает где t b, — время выборки из памяти; время суммирования двух см чисел; ссдв - время сдвига.

Если данное устройство построено на элементах 155 серии и используется для обработки 16-разрядных двоичных чисел, то т в„,в 100 нс

100 нс H t дв 100 нс

-Т 2.100+2-100+100 500 нс

В этом случае требуется объем памяти ч = 10623 бит Г2(.

Недостаток устройства — низкое быстродействие и большой объем памяти.

Цель изобретения — повышение быстродействия и уменьшение объема памяти устройствА.

Поставленная цель достигается тем, что в устройство, содержащее входной регистр, три блока памяти, блок синхронизации, .первый сумматор и выходной регистр, вход которого соединен с выходом. первого сумматора, первый вход которого соединен с выхо847319 дом первого блока памяти, первый и второй выходы блока синхронизации соединены с управляющими входами входного и выходного регистров,дополнительно введены шесть Регистров второй сумматор, блок возведения в квадрат и блок умножения, причем выходы К старших разрядов входного регистра соединены со входом второго блока памяти и входом первого регистра, управляющий вход которого соединен с третьим выходом блока синхронизации и управляющим входом второго регистра, входы которого соединены с выходами второго сумматора, первый вход которого соединен с выходом входного регистра, второй вход второго сумматора соединен с выходом второго блока памяти, выходы первого и второго регистров соединены соответственно со входом третьего и через блок возведения в квадрат со входом четвертого регистров, управляющие входы которых соединены с четвертым выходом блока синхронизации, пятый выход которого соединен с управляющими входами пятого и шестого регистров, входы которых .соединены соответственно с выходами третьего регистра и блока умно- жения, первый вход которого через четвертый регистр соединен с выходом блока возведения в квадрат, второй вход блока умножения через третий блок памяти соединен с выходом третьего регистра, выход шестого регистра соединен со вторым входом первого сумматора, выход пятого регистра соединен со входом первого блока памяти.

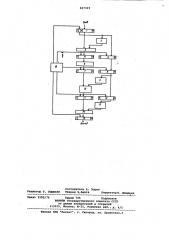

На чертеже представлена блок-схема устройства.

Устройство содержит входной регистр 1, блок 2 памяти, сумматор 3, регистры 4 и 5, блок 6 возведения в квадрат, регистры 7 и 8, блок 9 памяти, блок 10 умножения, регистры

11 и 12, блок 13 памяти, сумматор

14, регистр 15, блок 16 синхронизации.

Программируемые постоянные запоминающие устройства.2,9 и 13 служат для хранения констант, которые используются в процессе вычисления логарифма числа. Емкость блоков памяти зависит от требуемой точности вычисления. Адресация осуществляется по К старшим разрядам числа, над которым производится операция.

Регистры 4,5,7,8,11 и 12 устройства служат для промежуточного запоминания результатов вычислений,а также для обеспечения конвейерного способа обработки данных, причем регистры 4,7,11 и .15 - л-разрядные, а регистры 5,8 и 12 - К-разрядные.

Устройство предназначено для обработки нормализованных данных, представленных в формате с фиксированной запятой.

Вычисление функции Y = log Х производится на основе метода сегментной аппроксимации выражением

А + W(X + В), где константы

А, В и W выбираются из условия минимизации абсолютной погрешности.

Диапазон изменения аргумента

2

1) разбивается на интервалы, колн1О. чество которых определяется требуемой точностью, причем границы интервалов выражаются К старшими двоичными разрядами аргумента.

На равных интервалах константы имеют различные значения. Константы

В хранятся в блоке 2, константы W— в блоке 9 и константы A — - в блоке 13.

Адресация к каждому блоку памяти осуществляется по К старшим разрядам

20 аргумента, которые определяют, в каком интервале находится аргумент.

Устройство работает следующим образом.

Аргумент X поступает во входной

2 регистр 1, а иэ него — на сумматор 3.

Одновременно иэ блока 2 по адресу, указанному К старшими разрядами аргумента Х выбирается константа В и также поступает на сумматор 3. В сумматоре 3 производится выработка суммы, которая через регистр 4 поступает на блок 6 возведения в квадрат, в котором формируется выражение (X+8), а иэ него оно поступает на регистр 7. Одновременно старшие К разрядов аргумента Х проходят через регистры 5 и 8, поступают на регистр 12 и в блок 9, из которого считывается константа W; соответствующая интервалу, указанному К

40 старшими разрядами аргумента. Выражение иэ регистра 7 и константа W из блока 9 поступают на блок умножения 10, в котором формируется выражение W(X+8), поступающее на

4 РегистР 11, а иэ него — на сумматор

14. Из блока 13 памяти по адресу, указанному кодом as регистра 12 считывается константа А и подается на сумматор 14, в котором формируется требуемое выражение A+W(X+8)>, которое через регистр 15 подается иа выход. Выработка управляющих сигналов производится в блоке 16 синхронизации.

Работа устройства рассматривается на примере.

В первом такте на входной регистр

1 поступает нормализованное 15-разрядное число, равное

Х=(0,57331), =(0,100100101100010)2,.

1Щ При делении диапазона изменения аргумента Х .на интервалы учитывается то обстоятельство, что граница каждого интервала отличается от другого по пяти старшим разрядам. Поэтому, Я по поступающим иэ входного регистра

847319

1 пяти старшим разрядам из блока 2 считывается константа В, соответствующая данному интервалу, равная

В = (-1,001100111110100)1

Аргумент Х из входного регистра1 и константа В иэ блока 2 подаются на сумматор 3, в котором формируется выражение X+B, равное (-0,101000010010010) .

Во втором такте выражение поступает на регистр 4,.а из него на блок б возведения .в квадрат, где формируется вйражение (X+B ),т.е. (0,011001010110111) . Также во втором такте пять старших двоичных разрядов аргумента (10010) поступают на регистр 5.

В третьем такте число из регистра

5 поступает на регистр 8, из него— на вход блока 9 памяти. Величина имеет два значения †.1 и -2, по которым 20 происходит сдвиг в блоке 10 на один разряд влево или пропускается число из регистра 7 без сдвига. В данном примере в блоке 10 осуществляется сдвиг на выходе получается число 5

W(X+B), равное (-0,1100101011011104

В четвертом такте число поступает на регистр 11, а из него на сумматор 14. Одновременно на регистр 12 поступает число из регистра 8 и по укаэанному им адресу иэ блока 13 считывается константа A равная

A = (-0,000000101001101)

Эта константа также поступает на сумматор 14 и на его выходе получаем выражение A+W(X+B) равное (-110011010111011)g .

В пятом такте число поступает на регистр 15 и из него на выход. Это и есть вычисленный !age 0,57331.

Найденный по таблице логарифм равен 40 (-0,8026155) о=(-0,110011010111100)

Как видно, ошибка не превышает младшего разряда числа, т.е. меньше 2 .

Данное устройство работает по конвейерному принципу. В каждом так- 4g те в него вводится новый операнд.

Наиболее времяеМКим узлом в .устройстве является блок б возведения в квадрат, поэтому такт конвейерной обработки массива данных равен време- 0 ни возведения в квадрат Т . Это и есть быстродействие устройства при обработке массивов данных . При построении устройства для возведения в квадрат на элементах 155 Т„ = 165 нс.

Предлагаемое устройство отлича ется от известного. При обработке массивов данных быстродействие увеличивается в

Т 500 нс

T„ 165 = 3 р =. 60

Для хранения таблицы констант потребуется память объемом Q„= 800бит

По сравнению с известным — выигрыш в объеме памяти в

Q 10623 бит .

800 бит

Формула изобретения

Устройство для логарифмирования массивов двоичных чисел, содержащее входной регистр, три блока памяти, блок синхронизации, первый сумматор .и выходной регистр, вход которого соединен с выходом первого сумматора, первый вход которого соединен с выходом первого блока памяти, первый и второй выходы блока синхронизации соединены с управляющими входами входного и выходного регистров, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены шесть регистров,второй сумматор, блок возведения в квадрат, блок умножения, причем выходы К старших разрядов входного регистра соединены со входом второго блока памяти и входом первого регистра, управляющий вход которого соединен с третьим выходом блока синхронизации и управляющим входом второго регистра, входы которого соединены с выходами второго сумматора, первый вход которого соединен с выходом входного регистра, второй вход второго сумматора соединен с выходом второго блока памяти, выходы первого и второго регистров соединены соответственно со входом третьего и через блок возведения в квадрат со входом четвертого регистров, управляющие входы которых соединены с четвертым выходом блока синхронизации, пятый выход которого соединен с управляющими входами пятого и шестого регистров, входы которых соединены соогветственно с выходами третьего регистра и блока умножения, первый вход которого через четвертый регистр соединен с выходом блока возведения в квадрат, второй вход блока умножения через третий блок памяти соединен с выходом третьего регистра, выход шестого регистра соединен со вторым входом первого сумматора, выход пятого регистра соединен со входом первого блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 235395, кл. G 06 F 7/38, 1968.

2. Авторское свидетельство СССР

9 593212, кл. G 06 F 7/38, 1978 (прототип).

847319

Заказ 5500/76

Тираж 745 Подписное

ВНИИЙИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент", г. ужгород, ул. Проектная,4

Составитель A.. Зорин

Редактор T. Гырвкан Техред З,Фанта КорректорН. Швыдкая

Д.