Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ 847377

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (51)М. Кл;

{22) Заявлено 23. 07. 79(21) 2799849/18-24

6 11 С 29/00 с присоединением заявки,%—

Воударствонный комитет

СССР (23) Приоритет— ао йелои изобретений и открытий

Опубликовано 15.07.81, Бюллетень ¹26

Дата опубликоваиия описания 17.07.81 (5З УД K 681. 327 (088.8) с

Г.К. Алдабаев, Г.И. Белов, Л.В. Дербунович. К.И. Диденко, Г.И. Загарий, А.Н. Кокарев, А.И. Литкевич и А.Ъ.Ручцрский

Специальное конструкторское бюр систем автоматического управления и Харьковский ордена Ленина политехниче кий институт им. В.И. Ленина (72) Авторы изоб1,етеии я (71) Заявители (54 ) ЗАПОИИНАЮ111ЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство, в котором, каждое слово содержит три контрольных разряда, в один из которых записывается дополнение до не5 четности кода информационных разрядов записываемого числа, а в два других— прямой и обратный код остатка от деления кода адреса ячейки на три Г1 1.

Недостатком этого устройства является его низкая надежность.

Наиболее близким техническим решением к предлагаемому является запо-. минающее устройство, содержащее регистр адреса, входы которого соединены с адресной шиной устройства, выходы старших разрядов — с входами дешифратора и управляющими входами первого коммутатора, а выходы младших разрядов с адресными входами накопителя, стробирующие входы которого подключены к соответствующим выходам дешифратора, а выходы - к соответствующим информационным входам пер. вого коммутатора (2 1.

Недостатком этого устройства является отсутствие контроля операции записи, адресации при считывании, контроля усилителей считывания и неисправностей в накопителе, что обуславливает низкую надежность запоминающего устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее регистр адреса, дешифратор, накопитель и первый коммутатор, причем входы регистра адреса соединены с адресными шинами уст-. ройства, одни иэ выходов — со входами дешифратора и управляющими входами первого коммутатора, а другие выходыс адресными входами накопителя, стробирующие входы которого подключены к соответствукхцим выходам дешифратора, а выходы — к информационным входам

847377

Д та РАВНОЗНАЧНОСТЬ 6, выход которого соединен с первым входом элемента

ИЛИ 7. Выходы второго коммутатора 9 подключены к информационным входам формирователя 10 контрольных сигналов, адресные входы которого соединены с адресными входами накопителя

3, а выход подключен к первым входам элемента И 8 и регистру инфор10 мации 5. Второй вход регистра 5 информации подключен ко второму входу второго коммутатора 9 и информационному входу 14 устройства, а третий вход — к управляющей шине 13 устройства, третьему входу второго коммутатора 9 и входу элемента 11 задержки.

Выход элемента )1 задержки соецинен с управляющими входами накопителя 3, вторым входом элемента РАВНОЗНАЧНОСТЬ

6 и вторым входом элемента И 8, выход которого подключен ко второму входу элемента ИЛИ 7, выход которого является контрольным выходом 16 устройства. Выход регистра 5 информации соединен с третьим входом элемента

РАВНОЗНАЧНОСТЬ 6 и информационными входами накопителя 3.

Устройство работает следующим образом.

При внешнем обращении к запоминаю30 щему устройству на адресных шинах

12 устанавливается адрес выбираемой ячейки, на управляющей шине 13— код операции (запись или считывание). на информационном входе 14 — записываемая информация. При выполнении операции записи информация заносится в регистр 5 информации по второму входу и, кроме того, через второй

P вход второго коммутатора 9, стро" бируемого кодом операции "Запись", поступает на второй вход формирователя 10 контрольных сигналов, на первый вход которого подаются одновременно младшие разряды кода адре4 са с регистра 1 адреса. первого коммутатора, выход которого является информационным выходом устройства, введены регистр информации, формирователь контрольных сигналов, второй коммутатор, элемент РАВНОЗНАЧНОСТЬ, элемент И и элемент ИЛИ, причем первый вход второго коммутатора подключен к выходу первого коммутатора и первому входу элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом элемента ИЛИ, выходы второго коммутатора подключены к информационным входам формирователя контрольных сигналов, адресные входы которого соединены с адресными входами накопителя, а выход подключен к первым входам элемента И и регистра информации, второй вход которого подключен ко второму входу второ го коммутатора и информационному входу устройства, а третий вход — к упра ляющей шине устройства, третьему входу второго коммутатора и входу элемен та задержки, выход которого соединен с управляющими входами накопителя, вторым входом элемента РАВНОЗНАЧНОСТЬ и вторым входом элемента И, выход которого подключен ко второму входу элемента ИЛИ, выход которого является контрольным выходом устройства, выход регистра информации соединен с третьим входом элемента РАВНОЗНАЧНОСТЬ и информационными входами накопителя

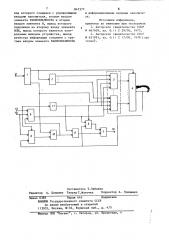

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит регистр 1 адр са, дешифратор 2, накопитель 3, первый коммутатор 4, регистр 5 информации, элемент РАВНОЗНАЧНОСТЬ 6, элеме

ИЛИ 7, элемент И 8, второй коммутато

9, формирователь 10 контрольных сиги лов, элемент ll задержки, адресную

12 и управляющую 13 шины. Устройство имеет информационные вход 14 и выход

15 и контрольный выход 16. Входы регистра 1 адреса соединены с адресными шинами 12 устройства, одни из выходов — со входами дешифратора 2 и управляющими входами первого коммутатора 4, а другие выходы — с адресными входами накопителя 3. Стробирующие 50 входы накопителя 3 подключены к соответствующим выходам дешифратора 2, а выходы — к информационным входам первого коммутатора 4, выход которого является информационным выходом 15 устройства. Первый вход второго коммутатора 9 подключен к выходу первого коммутатора 4 и первому входу элеменФормирователь 10 контрольных сигналов представляет собой схему свертки, например, по модулю 2, и формирует два контрольных разряда для записываемой или считываемой информации в младших разрядах кода адреса. Выбор функции (четность или не-. четность) определяется технической реализацией накопителя 3. Если невыбранный кристалл накопителя 3 формирует на выходе первого коммутатора

4 слово с единицами во всех разрядах

847377 4 или слово с нулями во всех разрядах, то присутствует ошибка адресации при считывании и формирователь 10 контрольных сигналов формирует сигнал четности при четном и сигнал нечетности при нечетном числе информационных разрядов, поступающих в режиме считывания с выхода первого коммутатора 4 через первый вход второго коммутатора 9 на информационный вход 10 формирователя 10 контрольных сигналов. Таким образом по заданному закону формируются контрольные разряды, которые заносятся по первому входу в регистр 5 информации и проис- !5 ходит формирование информационного слова, записываемого в выбранную ячейку накопителя 3. При этом запись в накопитель 3 производится но сигналу с управляющей шины 13, постунающе-20 му чере= .элемент 1! задержки на управляющие входы накопителя 3. Элемент

ll задержки осуществляет задержку управляющего сигнала на время формирования информационного слова ь регист- 25 ре 5 информации. При этом, при правильном функционировании устройства на выходе первого коммутатора 4 появляется одновременно информация, инверсная записываемой. Зта информация ЗО поступает на первый вход элемента

РАВНОЗНАЧНОСТЬ 6, на третий вход которого подается записываемая информация с выхода регистра 5 информации. Элемент РАВНОЗНАЧНОСТЬ 6 стробируется 35 по второму входу сигналом "Запись" и формирует сигнал "1" в случае совпадения сравниваемых сигналов а в слуи чае несовпадения формирует сигнал 0

Таким образом, если в процессе за 40 писи в информационном или адресном тракте есть неисправность, то она обнаруживается элементом РАВНОЗНАЧНОСТЬ 6, сигнал ошибки с выхода которого поступает через элемент. ИЛИ 7 С5 на контрольный выход 16 устройства.

При записи элемент И 8 закрыт сигналом "Запись" с управляющей шины 13, проходящей через элемент 11 задержки.

При выполнении операции считывания 50 аналогично режиму записи выполняется контроль наличия неисправностей в ячейках накопителя 3 и в адресном тракте.

Правильность адресации к кристаллу накопителя 3 проверяется первым коммутатором 4. Если в режиме считывания дешифратор 2 не правильно указал адрес выбираемого кристалла накопителя 3, то на выходе первого коммутатора 4 появляется информация, при которой формирователь контрольных сигналов выдает сигнал ошибки, поступающий через элемент И 8 и элемент ИЛИ 17 на контрольный выход 16 устройства. На втором входе элемента

И 8 при этом установлен разрешающий сигнал кода операции считывания °

Технико-экономическое преимущество предложенного устройства заключается в его повышенной по сравнению с известным надежности, так как в нем контролируется правильность адресации и наличие неисправностей в накопителе в режимах записи и считывания.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее регистр адреса, дешифратор, накопитель и первый коммутатор, причем входы регистра адреса соединены с адресными шинами устройства, одни из выходов — со входами дешифратора и управляющими входами первого коммутатора, а другие выходы с адресными входами накопителя, .стро

f бирующие входы которого подключены к соответствующим выходам дешифратора, а выходы — к информационным вхо дам первого коммутатора выход которого является информационным выходом устоойства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит регистр информации, формирователь контрольных сигналов, второй коммутатор, элемент РАВНОЗНАЧНОСТЬ, элемент И и элемент ИЛИ, причем первый вход второго коммутатора подключен к выходу первого коммутатора и первому входу элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом элемента

ИЛИ, выходы второго коммутатора подключены к информационным входам формирователя контрольных сигналов, адресные входы которого соединены с адресными входами накопителя, а выход подключен к первым входам элемента И и регистра информации; второй вход которого подключен ко второму входу второго коммутатора и информационному входу устройства, а третий вход — к управляющей шине устройства, третьему входу второго коммутатора и входу элемента задержки, вы7 847377 ход которого соединен с управляющими входами накопителя, вторым входом элемента РАВНОЗНАЧНОСТЬ и вторым входом элемента И, выход которого подключен ко второму входу элемента

ИЛИ, выход которого является контрольным выходом устройства, выход регистра информации соединен с третьим входом элемента РАВНОЗНАЧНОСТЬ

8 и информационными входами накопителя.

Ис то ч ники и нфор ма ции, принятые во внимание при экспертизе

Авторское свидетельство СССР

М 467409, кл. Ci 11 С 29/00, !975. . 2. Авторское свидетельство СССР

Р 63 !991, кл. 5 11 С 17/00, 1978 (про тотип) .

Составитель Т.Зайцева

Редактор А. Долинич Техред Т. Маточка Корректор А. Гриценко

Заказ 6385 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4