Декодер

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистических

Рестгублик

ОГ ИСАНИЕ

ИЗЬЬРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«ii847509 (61) Дополнительное к авт. свид-ву— (22) Заявлено 30.05.79 (21) 2774179/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл з

Н 03 К 13/24

Гесударстненный кемнтет ло делам изобретений и открытий (53) УДК 681.32 (088.8) Опубликовано 15.07.81. Бюллетень №26

Дата опубликования описания 25.07.81 (72) Автор изобретения

В. В. Кацман (71) Заявитель (54) ДЕКОДЕР

Изобретение относится к автоматике.

Наиболее близким техническим решением к изобретению является декодер, содержащий селектор второго импульса, входы которого соединены с входными шинами, а выход подключен к одному из входов элемента ИЛИ вЂ” НЕ, выход которого соединен с выходной шиной, а другой вход — с инверсным выходом второго разряда двухразрядного регистра сдвига, а также триггер и два формирователя (1) .

Недостаток известного устройства сложность конструкции.

Цель изобретения — упрощение декодера.

Указанная цель достигается тем, что в декодере, содержащем селектор второго импульса, входы которого соединены с входными шинами, а выход подключен к одному из входов элемента ИЛИ вЂ” НЕ, выход которого соединен с выходной шиной, а другой вход — с инверсным выходом второго разряда двухразрядного регистра сдвига, а также триггер и два формирователя, первая и вторая входные шины соединены соответственно с единичным и нулевым входами триггера, единичный и нулевой выходы ко2 торого через формирователи объединены и подключены ко входу двухразрядного регистра сдвига.

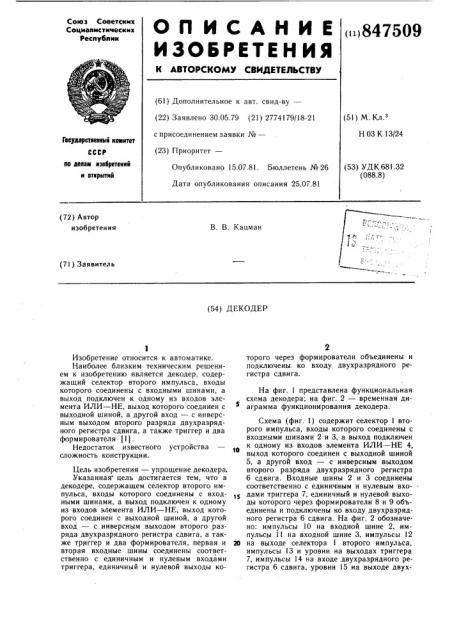

На фиг. 1 представлена функциональная схема декодера; на фиг, 2 — временная диаграмма функционирования декодера.

Схема (фиг. 1) содержит селектор 1 второго импульса, входы которого соединены с входными шинами 2 и 3, а выход подключен к одному из входов элемента ИЛИ вЂ” НЕ 4, выход которого соединен с выходной шиной

5, а другой вход — с инверсным выходом второго разряда двух разрядного регистра

6 сдвига. Входные шины 2 и 3 соединены соответственно с единичным и нулевым входами триггера 7, единичный и нулевой выходы которого через формирователи 8 и 9 об ьединены и подключены ко входу двухразрядного регистра 6 сдвига. На фиг. 2 обозначено: импульсы 10 на входной шине 2, импульсы 11 на входной шине 3, импульсы 12

10 на выходе селектора 1 второго импульса, импульсы 13 и уровни на выходах триггера

7, импульсы 14 на входе двухразрядного регистра 6 сдвига, уровни 15 на выходе двух847509 фиг !

11(1, (1(1 1 (((12 11 1(1 11 (1, 1 111 (1 1 I (! 1

11111(, 1 ! ! (11, 111, 11!

13 (!1(1(11 !! (! I ! (1(1! ((! (!

11 (! (111

И4 ( (1111 ! (111 (1

1 ! !

1 1 1

1! 1, 1 ((! 1 1 (1 1 1 (1 (1 1 1 1 1 !

ВНИИПИ Заказ 5527/85 Тираж 988 Подписное

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 разрядного регистра 6 сдвига, импульсы 16 на выходе элемента ИЛИ вЂ” НЕ 4.

Функционирование декодера осуществляется следующим образом.

Кодированная последовательность импульсов положительной и отрицательной полярности в коде СНДВ-2 поступает на входы селектора 1 второго импульса и триггера 7. На выходе селектора 1 второго импульса селектируется каждый второй импульс последовательности положительной и отрицательной полярности, а триггер 7 изменяет свое состояние при поступлении импульсов противоположной полярности. Формирователи 8 и 9 формируют импульсы в моменты, соответствующие изменению состояния триггера 7, которые поступают на вход двух разрядного регистра 6 сдвига, осуществляющего их задержку на два такта. С выхода двухразрядного регистра 6 сдвига задержанная последовательность импульсов поступает на один из входов элемента ИЛИ вЂ” НЕ 4, на второй вход которого поступает последовательность импульсов с выхода селектора

1 второго импульса. В результате этого на выходе элемента ИЛИ вЂ” НЕ 4 формируется декодированная последовательность импульсов.

Таким образом, предлагаемый декодер отличается от известного тем, что содержит меньшее число элементов и связей.

Формула изобретения

Декодер, содержащий селектор второго импульса, входы которого соединены с входными шинами, а выход подключен к одному из входов элемента ИЛИ вЂ” НЕ, выход которого соединен с выходной шиной, а другой вход — с инверсным выходом второго разряда двухразрядного регистра сдвига, а также триггер и два формирователя, огличающийся тем, что, с целью упрощения, первая и вторая входные шины соединены соответственно с единичным и нулевым входами триггера, единичный и нулевой выходы которого через формирователи объединены и подключены ко входу двухразрядного регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1. Alain Groisier, Compatible High-0епsi ty 6i pol ar Codes: An Unrest icted Transmission Plan for PCM Carries. 1ЕЕЕ Transact!ons on Communication Technology, чо!.

СОМ-18, п. 3, June 1970, р. 266, fig. 2 (прототип).! (111,1(((((11(1! н (! ! (11 111(11((11(1 (11! ()!

11, 111(1,,! (11