Пиковый детектор

Иллюстрации

Показать всеРеферат

О Л И С А Н И Е (1ц849083

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз -Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву 1Р 662875 (22) Заявлено 05 10,79 . (21) 2824500/18-21 с присоединением заявки М (23) Приоритет—

Опубликоваио23,07.81, Бюллетень М 27

Дата опубликования описания 23.07.81 (5l)M. Кл.

G 01 R 19/04

G 05 В 1/01

ГааударетаанныИ кюмнтет

СССР по данам изобретений и аткрытий (53) >B K 621.317.7 (088.8) P. М. Сабиров, С. В, Костюк, Ю. П. Миронычев и Г. М. Приезжев (72). Авторы изобретения (71) Заявитель (54) ПИКОВЫЙ ДЕТЕКТОР

Изобретение относится к электроизмеритель- ной технике, а точнее к устройствам, измеряющим амплитуду импульсного напряжения, к может приМеняться в радиотехнических установках различного назначения.

По основному авт. св. М 662875 известны пиковые детекторы, содержащие дифференциальный усилитель, повторитель, диодно-конденсаторную ячейку, входом соединенную с выходом усилителя, выходом — с входом повто. рителя, дополнительный дифференциальный

10 усилитель, диод и резистор, причем неинвертирующий вход дополнительного усилителя соединен с выходом пикового детектор», инвертирующий вход дополнительного усилителя соединен с выходом усилителя, анод диода соединен ,5 с выходом дополнителъного усилителя, а катод — с неинвертирующим входом усилителя, соединеннътм также через резистор с входом пикового детектора 111.

Недостатком известнъ х устройств является большая инерционность при уменьшении ампли- . туды входных импульсов, что уменьшает быстродействие.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в пиковь1й детектор, содержащий повторитель напряжения, дифференциальный усилитель постоянного тока, выход которого соединен с инвертирующим входом усилителя, диодно-конденсаторную ячейку, вход которой соединен с выходом усилителя, а выход — с входом повторителя напряжения,. дополнителъный дифференциальный усилитель постоянного тока, диод и резистор, причем неинвертирующий вход дополнительного усилителя соединен с выходом пикового детектора, инвертирующий вход дополнительного усилителя соединен с выходом усилителя, анод дйода соединен с выходом дополнительного усилителя, а катод — с неиивертирующим входом усилителя, соединенным также через резистор с входом пикового детектора, введены резистивный делитель, амплитудный выпрямитель, разрядный блок и. элемент сравнения с усилением, первый вход которого подключен к шине входных сигналов, второй вход — к выходу резистивного

849083 4 делителя, подсоединенного к выходу повтори.теля, а выход — через последовательно соеди. ченные амплитудный выпрямитель и разряд:ный блок к входу повторителя.

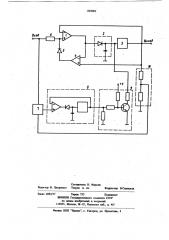

На чертеже представлена блок-схема предла гаемого устройства.

Пиковый детектор содержит последовательно соединенные основной усилитель 1, диодноконденсаторную запоминающую ячейку 2 и повторитель 3 напряжения. К выходам основного усилителя 1 и повторителя 3 подключены входы дополнительного усилителя 4, выход кото- рого через диод 5 и резистор 6 подключен к первому входу элемента сравнения с усилением 7, выходом подключенного через последовательно соединенные амплитудный выпрямитель 8 и разрядный блок 9 к входу повторителя 3, а второй вход — к выходу резистивг ного делителя 10.

В установившемся режиме импульсы положи- о тельной полярности с постоянной амплитудой поступают на вход пикового детектора. Конденсатор запоминающей ячейки 2 заряжен, а выходное-напряжение пикового детектора с определенной погрешностью равно амплитуде д входных импульсов пикового детектора. На элемент сравнения с усилением 7 поступают входные импульсы и часть выходного напряжения амплитудного детектора с резистивного делителя 10. Коэффициент деления резистив- зо ного делителя 10 выбран таким, чтобы в установившемся режиме напряжение на выходе резистивного делителя 10 было всегда меньше амплитуды входного импульса детектора на незначительную величину. Тогда на вы- з5 ходе элемента сравнения с усилением 7 в установившемся режиме будут присутствовать усиленныЕ разностные импульсы отрицательной полярности. Эти импульсы поступают на малоинерционный амплитудный выпрямитель 8, с вы-4р хода которого отрицательное напряжение поступает на разрядный блок 9 и запирает транзистор цепи разряда. Таким образом, разрядный блок 9 в установившемся режиме не будет влиять на работу собственно детектора.

Если в какой-то момент времени амплитуда входных импульсов детектора увеличится, то произойдет быстрый заряд конденсатора sanoминающей ячейки 2 через малое выходное сопротивление основного усилителя 1.

Транзистор разрядного блока 9 в это время также закрыт и цель разряда не оказывает влияние на процесс заряда. Через некоторое время устанавливается новое состояние равновесия, При уменьшении амплитуды входных им- 55 пульсов, в первый момент времени величина напряжения,.подаваемого с резистивного делителя 10, превышает амплитуду входных импуль1сов. Тогда импульсы на выходе элемента срав1 нения с усилением 7 отсутствуют. Конденсатор амплитудного выпрямителя 8 быстро разряжается и отрицательное напряжение на выходе амплитудного выпрямителя 8 быстро снижается практически до нуля. Для быстрого разряда конденсатора амплитудного выпрямителя 8 величина его емкости берется на несколько порядков ниже величины емкости конденсатора запоминающей ячейки 2. При этом уровень пульсаций выходного напряжения амплитудного выпрямителя 8 получается высоким, но это допустимо, поскольку не увеличивается уровень пульсаций выходного напряжения детектора, в то же время как быстродействие детектора существенно повышается. При отсутствии отрицательного напряжения на выходе амплитудного выпрямителя 8, транзистор разрядного блока 9 открывается и происходит быстрый разряд конденсатора запоминающей ячейки 2 через открытый транзистор до нового уровня напряжения, определяемого амплитудой входных импульсов детектора. При достижении равенства выходным напряжением детектора . нового значения амплитуды входных импульсов, разряд конденсатора запоминающей ячейки 2 прекращается, так как на выходе элемента сравнения с усилением 7 появляются импульсы отрицательной полярности и практически с первым же импульсом на выходе амплитудного выпрямителя 8 появляется отрицательное напряжение, которое запирает транзистор разрядного блока 9, прекращая разряд конденсатора sanoминаюшей ячейки 2. Следовательно, применение указанных связей и элементов позволяет увеличить быстродействие пикового детектора последовательности импульсов при уменьшении амплитуды входных импульсов детектора.

Формула изобретения

Пиковый детектор по авт. св. No 662875, отличающийся тем, что, с целью повышения быстродействия, в него введены резистивный делитель, амплитудный выпрямитель, разрядный блок и элемент сравнения с усилением, первый вход которого подключен к шине входных сигналов, второй вход— к выходу резистивного делителя, подсоединенного к выходу повторителя, а выход — через последовательно соединенные амплитудный выпрямитель и разрядный блок к входу повторителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 662875, кл. G 01 В 19/04, 14,02.75 (прототип).

849083

Составитель Н. Маркин

Редактор В. Лаэаренко Техред А. Ач Корректор В.Синицкая

Заказ 6084/57 тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

133035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4