Устройство для измерения амплитуднофазовых частотных характеристик

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Рвслублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТЕЛЬСТВУ н>849151 (61) Дополнительное к авт. свид-ву— (51)м. Кл.

G 05 В 23/OZ (22) Заявлено 110579 (21) 2765192/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Государственный комитет

СССР по дел ам изобретен и и и открытий

Опубликовано 2 gp 781.Áþëëåòåíü № 27 (53) УДК 62-50 (7 1 ) Заявитель

Днепропетровский ордена Трудового Красного Знамени горный институт им. Артема (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДНО-ФАЗОВЫХ

ЧАСТОТНЫХ ХАРАКТЕРИСТИК

Изобретение относится к автоматическому управлению и регулированию и предназначено для экспериментального исследования динамических характеристик линейных систем автоматического управления (САУ).

Известен анализатор спектра, основанный на вычислении ряда Фурье, содержащий генератор гармонических колебаний ортогональных функций (синусоидальных и косинусоидальных колебаний), блоки умножения, интеграторы и регистраторы. При определении амплитудно-фазовых характеристик этим анализатором система выводится на режим вынужденных колебаний, выходной сигнал системы умножается на синусоидальные и косинусоидальные колебания, а затем полученное произведение интегрируется на периоде. На выходах интеграторов получаются значения вещественной и мнимой составляющих амплитудно-фазовой характеристики Г13 .

Недостатками такого устройства являются длительность определения амплитудно-фазовых характеристик, так как точки амплитудно-фаэовой характеристики определяются путем последовательной подачи на вход системы ря- 30 да частот, а также сложность в реализации блоков умножения.

Наиболее близким к предлагаемому по технической сущности является устройство для определения амплитуднофазовых характеристик, содержащее генератор частоты, формирователь часто.ты, генератор функций Родемахера, блок дискретно-аналоговых генераторов, сумматор, преобразователь "напряжение-частота", задатчик интервала интегрирования, ключ, блок выделения знака, два блока логических элементов, два блока делителей частоты и два блока корреляторов, выходы которых соединены с соответствующими входами блоков регистрирующих приборов, выход блока выделения знака соединен с первыми входами блоков логических элементов (.2 .

Недостатком известного устройства является длительность определения амплитудно-фазовых характеристик при большом количестве точек.

Цель изобретения — повышение точности и быстродействия устройства.

Эта цель достигается тем, что в устройстве для измерения амплитуднофазовых частотных характеристик, содержащем последовательно соединенные

849151 задающий генератор, декадный делитель частоты, октавный делитель частоты, блок формирования полигармонического сигнала, последовательно соединенные регистр сдвига, первый элемент И, первый блок формирования ортогонального сигнала, первый блок умножения, первый цифровой интегратор, после:довательно соединенные второй блок формирования ортогонального сигнала, второй блок умножения, второй цифровой интегратор, причем входы блоков формирования ортогональных сигналов соединены, выход регистра сдвига подключен к первому входу второго элемента И, второй вход первого элемента И подключен к первому вхо- 1э ду третьего элемента И и к соответствующему выходу октавного Делителя частоты, второй вход второго элемента И подсоединен к соответствующему выходу программного блока, к друго- 20 му выходу которого подключен второй вход декадного делителя частоты, второй вход первого блока умножения подключен ко второму входу второго блока умножения и ко входу устройства, к выходу которого подключен выход блока формирования полигармонического сигнала, вход распределителя импульсов подключен к соответствующему выходу программного блока, первый выход блока сравнения кодов подключен к соответствующему входу блока регистрации, первый вход дешифратора подключен к соответствующему выходу программного блока, а также блок управления регистрацией, нуль-орган, вычислитель квадранта, четвертый элемент И, элемент ИЛИ, формирователь импульсов, выход первого цифрового интегратора подключен ко входу блока сравнения кодов и первому входу вы- 40 числителя квадранта, второй вход которого подключен к выходу второго цифрового интегратора и входу нульоргана, выход которого и второй выход блока сравнения кодов подключены ко входам четвертого элемента И, выход которого подключен к соответствующему входу программного блока, выход блока вычисления квадранта подключен через дешифратор ко входам ц счетчика фазы, выход первого блока формирования ортогонального сигнала через формирователь импульсов подсоединен, ко второму входу распределителя импульсов, первый выход которого подключен к первому входу элемента

ИЛИ,звторой выход подключен ко второму входу элемента ИЛИ и первому входу регистра сдвига, третий выход через третий элемент И подсоединен ко второму входу регистра сдвига, выход эле-46 мента ИЛИ подключен к соответствующему входу программного блока и вторым входам цифровых интеграторов, выход второго элемента И через вычитающий счетчик фазы подсоединен к соот- 45 ветствующему входу блока регистрации, один из входов которого через блок управления регистрацией подключен к выходу программного блока.

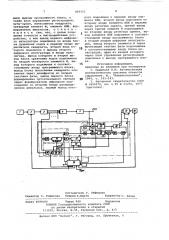

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит задающий генератор 1, декадный 2 и октавный 3 делители частоты, блок 4 формирования полигармонического сигнала, объект 5, канал 6 обработки октавной частоты,дискретный фазовращатель 7, блок

8 управления, измеритель 9 фазы, блоки 10 и 11 формирования действительной и мнимой составляющих, формирователь 12, регистр 13 сдвига, первый элемент И 14, второй элемент И 15, третий элемент И 16, распределитель

17, элемент ИЛИ 18, вычитающий счетчик 19 фазы, дешифратор 20, первый

21 и второй 24 блоки формирования ортогональных сигналов, первый 22 и второй 25 блоки умножения, первый

23 и второй 26 цифровые интеграторы„ блок 27 вычисления квадранта, нульорган 28, четвертый элемент И 29, блок 30 сравнения кодов, блок 31 регистрации, блок 32 управления регистрацией, программный блок 33.

Устройство работает следующим образом.

В исходном состоянии все интеграторы и счетчики находятся в нулевом состоянии, а распределитель 17 — в позиции 11!.

Процессы, происходящие в каждом из каналов обработки октавных частот, идентичны.

В одном из каналов по сигналу

"Пуск" программный блок 33 включает декадный делитель 2 на выдачу первой декады частот. Сигнал с делителя 2 поступает на вход ок авного делителя 3, с выхода которого сигналы поступают на входы блока формирования полигармонического сигнала и на входы каналов обработки октавных частот. В блоке 4 формируется полигармонический сигнал и подается на вход объекта 5 регулирования. Объем 5 выводится в режим вынужденных колебаний, с его выхода получаем сигнал

f (t).

По сигналу "Пуск" программный блок

33 переключает распределитель 17 в позицию 1. Сигнал с выхода распределителя 17 поступает на первый вход схемы ИЛИ 18 и с ее выхода поступает на входы цифровых интеграторов 23 и 26 и дает разрешение на их включение. Одновременно импульсы возбуждения октавной частоты через открытую схему 14 "Запрет" поступают на блоки 21 и 24 формирования ортогональных функций. Схема 14 "Запрет" работает по алгоритму С = AAB, где А — сигнал октавной частоты,  — сигнал регистра сдвига В.

849151

В блоке 21 происходит формирование сигнала cos wit, а в блоке 24 - sin wit.

Происходит процесс перемножения и интегрирования сигналов в блоках формирования действительной составляющей

10 и мнимой составляющей 11. По зна-. чащему моменту — окончанию первого полупериода функции cos wit — распределитель 17 формирователем 12 переключается в позицию 11, процесс интегрирования продолжается, а в регистре

13 сдвига заносится число, соответ-. ствующее единичному сдвигу фазы опор ного сигнала дЧ в процессе регулирования. После окончания второго полупериода распределитель 17 переключается .в позицию III, интеграторы отключаются от перемножителей через схему ИЛИ 18.

Число, записанное в интеграторе

23, переносится в блок 30 сравнения кодов, а по знакам сигналов интегра- 20 торов 23 и 26 блок 27 квадранта через дешифратор 20 квадранта заносит,в счетчик 21 начальное значение угла

М . Во время формирования полуперио— да через элемент И 16 на регистр 13 сдвига подаются тактовые импульсы, запрещающие передачу через схему 14 сигналов на блоки 21 и 24 формирования ортогональных функций. После освобождения регистра 13 схема "Запрет" Зц

14 отпирается, и продолжается форми— рование 3-ro полупериода функции.

Благодаря описанному процессу 3-й полупериод смещается на величину д У, что соответствует фазовому сдвигу опорного сигнала и составляющей данной частоты, содержащейся в сигнале

f(t). В 4-й и 5-й полупериоды действие схемы не отличается от описанного для 1-го и 2-ro полупериодов.

Когда распределитель снова переключа- @ ется в позицию III, то с выхода интегратора 23 на блок 30 поступает текущее значение действительной составляющей, которое сравнивается с предыдущим значением. 45

Такое сравнение по равенству кодов необходимо для того, чтобы зафиксировать поступление установившегося режима. При установившемся режиме коды равны, и с блока 30 сиг- у нал поступает на первый вход логической схемы И 29. В установившемся режиме процесс регулирования фазы длится до тех пор, пока нуль-орган

28 не определит равенство мнимой составляющей нулю, тогда совпадение сигналов установившегося режима и нуля мнимой составляющей на входах схемы

И 29 вызывает появление сигнала на выходе схемы И 29, который подается на программный блок 33 для разреше- Ф0 ния однократной регистрации значений амплитуды и фазы через блок 32 управления операцией регистрации в блоке

31 регистрации и индикации результатов, и последующее отключение данно- Я го октавного канала до перехода на следующую декаду частот. После окончания процессов регулирования и регистрации по всем октавным каналам программйое устройство 33 переключает делитель 2 на выдачу следующей декады частот и т.д. до завершения анализа во всей исследуемой области, Предлагаемое устройство осуществля ет автоматическое регулирование фазы опорных ортогональных .сигналов с целью получения нулевого значения мнимой составляющей амплитудно-фазовой частотной характеристики системы на заданной частоте в установившемся режиме объекта 5, дает на выходе блока 30 сравнения кодов сигнал, соответствующий амплитуде А, а суммарное значение фазового сдвига в процессе такого регулирования от начального значения дает на выходе вычитающего счетчика 19 значения сдвига фазы Ч, Предлагаемое устройство позволяет увеличить точность и сократить время измерения амплитудно-фазовой частотной характеристики системы регулирования на заданном частотном диапазоне. формула изобретения устройство для измерения амплитудно-фазовых частотных характеристик, содержащее последовательно соединенные задающий генератор, декадный делитель частоты, октавный делитель частоты, блок формирования полигармонического сигнала, последовательно соединенные регистр сдвига, первый элемент И, первый блок формирования орто-гонального сигнала, первый блок умножения,.первый цифровой интегратор, последовательно соединенные второй блок формирования ортогонального сигнала, второй блок умножения, второй цифровой интегратор, причем входы блоков формирования ортогональных сиг-. налов соединены, выход регистра сдвига подключен к первому входу второго элемента И, второй вход первого элемента И подключен к первому входу третьего элемента И и к соответствующему выходу октавного делителя частоты, второй вход второго элемента И подсоединен к.соответствующему выходу программного блока, к.другому выходу которого подключен второй вход декадного делителя частоты, второй вход первого блока умножения подключен ко второму входу второго блока, умножения и ко входу устройства, к выходу которого подключен выход блока формирования полигармонического сигнала, вход распределителя импульсов подключен к соответствующему выходу программного блока, первый выход блока сравнения кодов подключен к соответствующему входу блока регистрации, первый вход дешифратора подключен к соответствую849151

Составитель Г. Нефедова

Редактор С. Родикова Техред З.Фанта КоРРектоР О. Билак

Заказ 6090/60 Тираж 940 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 щему выходу программного блока, а такЖе блок управления регистрацией, нуль-орган, вычислитель квадранта, четвертый элемент И, элемент ИЛИ, формирователь импульсов, о т л и ч а— ю щ е е с я тем, что, с целью повышения точности и быстродействия устройства, в нем выход первого цифрового интегратора подключен ко входу блока сравнения кодов и первому входу вычислителя квадранта, второй вход ко-! торого подключен к выходу второго цифрового интегратора и входу нульоргана, выход которого и второй вы— ход бдока сравнения кодов подключены ко входам четвертсго элемента И, выход которого подключен к соответ- 35 ствующему входу программного блока, выход блока вычисления квадранта подключен через дешифратор ко входам счетчика фазы, выход первого блока формирования ортогонального сигнала Щ через формирователь импульсов подсоединен ко второму входу распределителя импульсов, первый выход которого подключен к первому входу элемента ИЛИ, второй выход подключен ко второму входу элемента ИЛИ и первому входу регистра сдвига, третий выход через третий элемент И подсоединен ко второму входу регистра сдвига, выход элемента ИЛИ подключен к соответствующему входу программного блока и вторым входам цифровых интеграторов, выход второго элемента И через вычитающий счетчик фазы подсоединен к соответствующему входу блока регистрации, один из входов которого через блок управления регистрацией подключен к выходу программного блока.

Источники информации, принятые во внимание при экспертизе

1. Ординцев Н.М. Автоматизация математического описания объектов управления. М., "Машиностроение", 1969, с. 141-143.

2. Авторское свидетельство СССР

Р 2454270, кл. 6, 05 В 23/02, 1977 (прототип).