Устройство для определения экстре-мальных значений последовательностичисел

Иллюстрации

Показать всеРеферат

Союз Советским

Соцналистическим

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ о>849200 (61) Дополнительное к авт. свид-ву (51) M. кл..з (22) Заявлено 30. 07.79 (21) 2801893/18-24 с присоединением заявки ¹

G 08 F 7/00

Государственный комнтет

СССР но делам нзобретеннй н ооткрытн и . (23) Приоритет

Опубликовано 23.0781, Бюллетень ¹ 27 (53) УДК 681. 325. 5 (088.8) Дата опубликования описания 23. 07. 81 (72) Авторы изобретения

В.Ф. Костарева, К.М. Одишария и Т.Э. Шараше идзе

Тбилисский научно-исследовательский институт приборостроения и средств автоматизации Научно-. производственного объединения "ЭЛВА"

° >

--.-1 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЭКСТРЕМАЛЬНЫХ

ЗНАЧЕНИЙ ПОСЛЕДОВАТЕЛЬНОСТИ ЧИСЕЛ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в информационноизмерительных системах и средствах автоматики.

Известно устройство для определе-; ния экстремальных значений, которое используется для выделения минимального или максимального числа из груп- о пы чисел, последовательно подаваемых на его вход. Устройство содержит ос новной регистр, имеющий несколько ступеней, который связан с источником числа. Число запоминающих ступеней укаэанного регистра равно наименьшему целому числу, большему, чем половина числа требуемых выработок группы. Кроме того, устройство содержит вспомогательные регистры, связан. ные с основным регистром через компаратор Bl .

Недостатком этого устройства является его сложность.

Наиболее близким к предлагаемому по технической сущности является устройство для определения экстремальных значений последовательности чисел, содержащее два входных регистра, схему для ввода цифровых значений в первый регистр, схему для передачи этих значений во второй регистр, схе.— му для сравнения содержимого первого, регистра со значением уже записанным во втором регистре, схему, срабаты- . вающую от выходного сигнала, схему для индикации содержимого второго регистра (искомого экстремального значения в последовательности цифровых величин, поступающих на первый регистр) и переключатель для задания условия — определение максимума или минимума (2(.

Недостаток известного устройства—

его низкое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройстве для определения экстремальных значений последовательности чисел, содержащем регистры, триггеры, схему сравнения, коммутатор, элементы И, ИЛИ, ИЛИ-НЕ, элементы задержки, причем выходы коммутатора соединены с первой группой входов схемы сравнения, первый и второй выходы которой подключены к первым входам первого и второго элементов И соответственно, выход первого элемента И соединен со входом установки в нулевое состояние первого триггера, 3

849200 выход второго элемента И подключен ко входу установки в единичное состояние первого триггера, инверсный выход первого триггера соединен со входом установки в единичное состояние второго триггера, прямой вы.ход которого подключен.к первому входу элемента ИЛИ-НЕ, прямой выход первого триггера соединен со входом устанонки в нулевое состояние третьего триггера, прямой выход которого подключен ко второму входу элемента

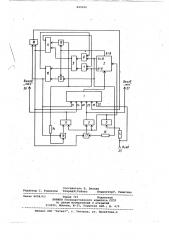

ИЛИ-НЕ, выход которого соединен с. первым управляющим входом коммутатора, инверсные выходы второго и третьего триггеров подключены ко вторым входам первого и второго элементов И. соответственно, третий выход схемы сравнения соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены соответственно ко второму и первому выхо- 20 дам схемы сравнения, прямой выход второго триггера соединен со вторым управляющим входом коммутатора и с первым входом третьего .элемента И, выход которого подключен к управляющему входу первого регистра, прямой выход третьего триггера соединен с третьим управляющим входом коммутатора и с первым входом четвертого элемента И, выход которого подключен к управляющему входу второго регистра, информационная шина устройства соединена с первой информационной шиной коммутатора и через первый элемент задержки — со входом третьего регист35 ра, выходы которого подключены ко второй группе входов схЬмы сравнения и к информационным входам первого и второго регистров, выходы которых соединены соответственно со второй и третьей информационными шинами ком- 40 мутатора, первый выход схемы сравнения через второй элемент задержки подключен ко второму входу третьего элемента И, второй выход схемы сравнения через третий элемент задержки 45 соединен со вторым входом четвертого элемента И, На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит коммутатор 1, 50 схему 2 сравнения, регистр 3, элемент 4 задержки, регистры 5 и б, элементы И 7 и 8, триггеры 9-11, элементы ИЛИ 12 и 13, элементы 14 и 15 задержки, элементы И 16 и 17, элементы ИЛЙ-НЕ 18, управляющие входы

19-21 коммутатора, информационные шины 22-24 коммутатора, информационная шина 25 устройства, выходные шины 26 и 27 устройства.

Устройство работает следующим 60 образом.

На информационную шину 25 устройства поступает последовательность чисел, наибольшее и наименьшее,значение которой надо определить. В 65 регистре 3 запсминается каждое предыдущее значение этой последовательности, которое сравнивается с каждым последующим в схеме 2 сравнения.

Результат сравнения регистрируется триггером 9, который сохраняет свое состояние от каждого предыдущего экстремума до последующего и меняет его после достижения экстремума, поэтому триггер 9.находится в единичном или нулевом состоянии, в зависимости от направления (увеличения или умень-. шения) изменения значения последовательности чисел.

В момент изменения состояния триггера 9 меняет нулевое состояние триггер 10 или 11, устанавливаясь в единичное. К схеме 2 сравнения подключа-. ются соответственно выходы регистров

6 или 5. Информация, записанная в этих регистрах, сравнивается с информацией, записанной в регистре 3, и на выходе схемы сравнения имеется высокий потенциал на одном из выходов A) В, А < В или A = В, после чего триггер 10 или 11 возвращается в исходное состояние,и на схему сравнения через коммутатор 1 поступает информация со входа устройства.

Если последовательность чисел изменяется в сторону увеличения, то имеется разрешение на управляющем входе 19 коммутатора 1 (за исключением интервала времени от момента изменения состояния триггера 9 в момент регистрации экстремального значения до момента выработки сигнала

"Сброс" элементами ИЛИ 12 и 13).

На выходе A (В схемы 2 сравнения имеется высокий потенциал. Триггер 9 находится в нулевом состоянии и продолжает оставаться в нем до момента, когда в регистре 3 запишется максимальное значение, на информационной шине устройства имеется величина

В, то на выходе А C В схемы сравнения высокий потенциал исчезает и появляется на выходе А ) В, и триггер 9 изменяет свое состояние на обратное. В этот момент взводится счетный триггер 10, и ввиду появления импульса на счетном входе дается разрешение на коммутацию выходов регистра б к схеме сравнения и отключается от схемы сравнения.

Предположим, что этот момент 1-ro экстремума, и поэтому в регистре б записан нуль, а в регистре 3 — максимальное значение. Тогда на схеме

2 сравнения имеем высокий потенциал на выходе А ) В, и дается разрешение на запись информации в регистр б, после чего триггер 10 возвращается в исходное нулевое состояние ввиду появления на выходе схемы сравнения

А=В высокого потенциала. Триггер 10 находится в нулевом состоянии до следующего экстремума. Одновременно с выхода элемента ИЛИ-НЕ 18 поступает

849200 разрешающий потенциал на управляющий вход 19 коммутатора 1 и исчезает разрешение с управляющего входа 21.

На схеме 2 сравнения опять сравниваI ется информация, поступающая со входа через ко утатор 1 и информация 5 записанная в регистре 3.. Триггер 9. продолжает оставаться в прежнем.состоянии до момента, когда в регистр 3 запишется минимальное значение, а на входы поступит число В . 10

В этот момент на выходе A с В схемы 2 .сравнения появляется высокий потенциал, триггер 9 меняет свое состеяние, взводится триггер. 11, а на выходе коммутатора 1 имеется информация, записанная в регистре 5, так как имеется разрешение на управляющем входе, 20 коммутатора 1, а входная информация отключается из-за отсутствия высокого потенциала на выходе элемента ИЛИ-НЕ 18. В схеме 2 сравнения 20 сравнивается информация, записанная в регистрах 3 и 5. Это первый экстремум, информация из регистра 3 записывается в регистр 5, и вновь появляется разрешение на управляющем 25 входе 19 коммутатора 1. В момент записи в регистре 3 информации сравнивается на схеме 2 сравнения максимальное значение и число, записанное в регистре б, оно перепишется из регистра 3 в регистр 6. В момент записи в регистре 3 минимального числа оно сравнивается на схеме сравнения с минимальным значением; записанным в регистре 5, и в регистре 5 остается записанная ранее величина. В виду того, что на выходе А < В схемы 2 сравнения не появляется высокий потенциал, элемент И 17 не выдает синхроимпульса, разрешающего перезапись информации из регистра 3 в регистр 5. 40

В этот же момент запрещается изменение состояния триггера 9 при помощи элемента И 7,.а в случае прихода на схему 2 сравнения следующего большего числа — элемента И 8. 45

Предлагаемое устройство может быть применено для сужения потока информации, поступающей от различных объектов в вычислительную машину, что дает возможность разгрузить ЭВМ и упростить алгоритмы управления.

Формула изобретения

Устройство для определения экстре55 мальных значений последовательности чисел, содержащее регистры, триггеры, схему сравнения, коммутатор, эле†мен И, ИЛИ, ИЛИ-НЕ, элементы задержки, причем выходы коммутатора Ь0 соединены с первой группой входов схемы сравнения, первый и второй вы ходы которой подключены к первым входам первого и второго элементов

И соответственно, выход первого элемента И соединен со входом установки в нулевое состояние первого триггера, выход второго элемента И подключен ко входу установки в единичное состояние первого триггера, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в нем инверсный выход первого триггера соединен со входом установки в единичное состояние второго триггера, прямой выход которого

*одключен к первому входу элемента

ИЛИ-НЕ, прямой выход первого триггера соединен со входом установки в нулевое состояние третьего триггера, прямой выход которого подключен ко второму входу элемента ИЛИ-НЕ, выход которого соединен с первым управляющим входом коммутатора, инверсные выходы второго и третьего триггеров подключены ко вторым входам первого и второго элементов И соответственно, третий выход схемы сравнения соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены соответственно ко второму и первому выходам схемы сравнения, прямой выход второго триггера соединен со вторым управляющим входом коммутатора и с первым входом третьего элемента И выход которого подключен к управляющему входу первого регистра, прямой выход третьего триггера соединен с третьим управляющим входом коммутатора и с первым входом четвертого элемента И, выход которого годключен к управляющему входу второго регистра, информационная шина устройства соединена с первой информационной шиной коммутатора и через первый элемент задержки со.входом третьего регистра, выходы которого подключены ко второй группе входов схемы сравнения и к информационным входам первого и второго регистров, выходы которых соединены соответственно со второй и третьей информационными шинами коммутатора, первый выход схемы сравнения через второй элемент задержки подключен ко второму входу третьего элемента И, второй выход схемы сравнения через третий элемент задержки соединен со вторым входом четвертого элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 486316, кл. G 06 F 7/06, 1974.

2. Патент Франции Р 2226704, кл. G 06 F 7/00, опублик. 1971 (прототип).

849200

Составитель В. Белкин

Редактор С. Родикова ТехредМ.Рейвес КорректорГ. Решетник

Заказ 6094/63 Тираж 745 Подписное

ВНИИПИ Государственного. комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ви

„m

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 ход П"