Устройство для моделированияраспределения частот

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()849279 (61) Дополнительное к авт. свид-ву— (22) Заявлено 30.11.79 (21) 2848566/18-12 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

G 09 В 9/00

G 09 В 19/26

Государственный комитет по делам нэооретеиий и открытий

Опубликовано 23.07.81. Бюллетень №27

Дата опубликования описания 28.07.81 (53) УДК 681.136..51 (088.8) (72) Автор изобретения

А. Ф. Веретенцев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ

РАСПРЕДЕЛЕНИЯ ЧАСТОТ

Изобретение относится к тренажерам операторов радиоэлектронной аппаратуры и может быгь использовано для обучения операторов-радиотелеграфистов.

Известно устройство для моделирования распределения частот, содержащее синхрогенератор, соединенный непосредственно и через блок управления с узлом моделей передатчиков, узлом моделей приемников и узлом моделирования полосы частот (1), Недостатком известного устройства яв- 1о ляется невысокая эффективность обучения.

Цель изобретения — повышение эффективности обучения.

Поставленная цель достигается тем, что устройство имеет узел элемента индикации и вычислителей, каждый из которых содержит логический блок, блок регулирования длительности импульса и группы блоков логической коммутации, при этом соответствующий выход узла моделей передатчиков подключен к первому входу блока регулирования длительности импульса и первым входам логического блока, выходы блока (регулирования длительности импульса связаны со входами логического блока, который через блоки логической коммутации подключен к соответствующим элементам индикации, информационные выходы узла моделирования, полосы частот подключены к входам блоков логической коммутации первой группы и второму входу логического блока, а информационные выходы узла моделей приемников связаны со входами блоков логической коммутации второй группы и вторым входом логического блока.

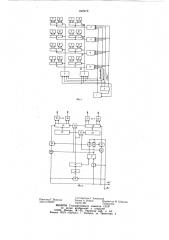

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — блок-схема вычислителя.

Устройство содержит синхронизатор 1, блок 2 управления, модели 3 передатчиков, модели 4 приемников, блоки 5 моделирования полосы частот, вычислители 6, элементы 7 и 8 индикации, логические элементы И 9, 10, 11, 12, 13, 14 и 15, одновибратор 16, триггер 17, интегратор 18, логические элементы ИЛИ 19, 20 и 21, регистры

22 и 23 сдвигающие, коммутатора 24 и 25, счетчики 26 и 27.

Позициями 28 обозначены информационные выходы узла моделирования полосы час849279

З5 о

55 тот, а позициями 29 — информационные выходы моделей приемников.

Информацио ные выходы 28 и 29 являются одновременно «Входами 2» вычислителя 6.

Логический блок имеет логические элементы И 9, 12, 13, 14, 15 и триггер 17.

Блок регулирования длительности импульса содержит одновибратор 16, интегратор 18 и логический элемент ИЛИ 19, Блок логической коммутации одной группы включает в себя логический элемент И 10, логический элемент ИЛИ 20, сдвигающий регистр 22, коммутатор 24 и счетчик 26. .Блок логической коммутации другой группы имеет логический элемент И 11, логический элемент ИЛИ 21, сдвигающий регистр 23, коммутатор 25 и счетчик 27.

Узел элементов индикации и вычисли телей содержит вычислители 6, элементы

7 и 8 индикации. Узел моделей передатчиков имеет модели 3 передатчиков.

Узел моделей приемников содержит модели 4 приемников. Узел моделирования полосы частот включает в себя блоки 5 моделирования полосы частот.

Устройство работает следующим образом.

По команде «Установка», подаваемой с помощью оператора с блока 2 управления, в модели передатчиков 3, в модели 4 прием- ников и блоки 5 передаются коды чисел, предварительно набранные оператором. Эти числа, соответственно, означают частоты настройки моделируемых радиопередатчиков и ширину полосы излучения как на основной, так и побочных частотах излучения, частоты настройки моделируемых приемников и ширину полосы пропускания как по основному, так и по по" î÷íûì каналам приема, запрещенные полосы частот (записываются в блоках 5) .

Через время задержки необходимое для выполнения команды «Установка», с блока 2 управления подается команда «Вычисление», в соответствии с которой в моделях передатчиков 3 вычисляются значения гармонических и интермодуляционных частот излучения, в моделях приемников 4 вычисляются значения частот каналов побочного приема.

По окончании выполнения команды «Вычисление» с блока 2 управления в синхронизатор 1 подается команда «Пуск», кото» рая вызывает генерацию синхроимпульсов в блоке 1. В момент подачи команды «Пуск» начинается процесс моделирования условий электромагнитной совместимости. В интервалы времени, соответствующие частотам излучения, синхроимпульсы проходят через модели передатчиков 3 и поступают на «Вход 1» вычислителя 6 (фиг. 1 и 2).

В интервалы времени, которые поставлены в соответствии с частотами приема и запрещенными частотами, с выходов моделей приемников 4 и блоков моделирова4 ния полосы, частот 5 синхроимпульсы поступают на «Вход 2» вычислителя 6.

Вычислитель 6 производит анализ условий электромагнитной совместимости моделируемых радиосредств, занимаемых передающими и приемными радиосредствами.

Синхроимпульсы, поступающие со «Входа 1» (фиг. 2), подаются на входы логических элемента И 13 и элемента ИЛИ 19.

Через открытый с помощью триггера 17 логический элемент И 13 синхроимпульсы

10 поступают на вход логического элемента

ИЛИ 21 и далее на вход коммутатора 25.

С выхода коммутатора 25 импульсные сигналы поступают на вход первого счетчика

27, в котором они записываются.

Поступление синхроимпульсов через логический элемент ИЛИ 19 на вход интегратора 18 ведет к образованию с помощью одновибратора 16 импульсного сигнала длительностью, равной времени прохождения серии синхроимпульсов. При этом задний ро фронт импульса, сформированного одновибратором 16 используется в качестве сигнала сброса. Указанный сигнал через открытый с помощью триггера 17 логический элемент И 14 поступает на вход коммутатора 25, с которого он проходит на вход сбро са первого счетчика 27, который при этом обнуляется. Схема остается в исходном состоянии, так как не произошло совпадения импульсов, соответствующих частотам излучения и приема.

Если в течение следования серии синхроимпульсов со «Входа 1» поступают импульсы со «Входа 2», то образуется сигнал совпадения в логическом элементе И 9, который переводит триггер 17 из состояния «1» в состояние «О». При этом открываются логические элементы И 11, 12, 15,. а логические элементы И 10, 13, 14 закрываются. В результате импульсы, поступающие со «Входа 1» на вход логического элемента ИЛИ 21, переключаются на вход логического элемента ИЛИ 20. Импульсы со

«Входа 2» вычислителя 6 проходят через открытый логический элемент И 11 на вход логического элемента ИЛИ 21. С выхода логического элемента ИЛИ 21 импульсные сигналы поступают через коммутатор 25 на счетный вход первого счетчика 27. В счетчике 27 производится суммирование импульсов, поступающих со «Входа 1» до момента их совпадения, и импульсов, поступающих со «Входа 2» после момента совпадения.

Функционирование блока, состоящего из схем 10, 20, 22, 24, 26 аналогично изложенному.

По окончании следования импульсов, как со «Входа 1», так и со «Входа 2», срабатывает одновибратор 16, который через открытый логический элемент И 15 передает сигнал продвижения в сдвигающие регистры 22 и 23. С регистров 22 и 23 передается сигнал управления на коммутаторы 24

849279 и 25, которые переключают входные шины к очередным счетчикам 26 и 27 соответственно. Одновременно по сигналу с одновибратора 16 триггер 17 переводится в исходное состояние.

При каждом очередном совпадении серий импульсов, поступающих со «Входов

1 и 2», в счетчиках 26 и 27 фиксируются соответствующие значения чисел.

Значения чисел со счетчиков 26 передаются в элементы 7 индикации, со счетчиков 27. — в элементы 8 табло индикации (фиг. 1).

В элементах 7 и 8, индикации, размещенных в i-ом столбце, отображается информация о-величинах частотного совпадения излучений i-го радиопередатчика с каналами приема моделируемых радиоприемников. В элементах 7 отображается значение необходимого увеличения частоты йриемника (уменьшения частоты передатчика), а в элементах 8 — значение необходимого увеличения частоты передатчика (уменьшения частоты приемника) для обеспечения условий совместимости моделируемых радиосредств.

В элементах 7 и 8 индикации, размещенных в j-ой строке, отображается аналогичная информация о j-ом моделируемом радиоприемнике.

В элементы 7 и 8 индикации, которые через вычислители 6 соединены с блоками

5 моделирования полосы частот, выводится информация о выполнении . или не выполнении частотных запретов на излучения, Отображаемая информация дает возможность судить о правильности распределения радиочастот или о необходимости увеличения частотных разносов для обеспечения совместимости радиоаппаратуры.

Применение предлагаемого устройства повышает эффективность обучения, так как позволяет проводить эффективное обучение технического персонала методом распределения и использования частотного ресурса- и контроль за правильностью назначения частот для радиоэлектронных средств.

Формула изобретения

Устройство для моделирования распределения частот, содержащее синхрогенера о тор, соединенныи непосредственно и через блок управления с узлом моделей передатчиков, узлом моделей приемников и узлом моделирования полосы частот, отличающееся тем, что, с целью повышения эффективности обучения, оно имеет узел элементов индикации и вычислителей, каждый из которых содержит логический блок, блок регулирования длительности импульса и группы блоков логической коммутации, при этом соответствующий выход узла моделей передатчиков подключен к первому входу блока регулирования длительности импульса и первым входам логического блока, выходы блока регулирования длительности импульса связаны со входами логического блока, который через блоки логической коммутации подключен к соответствующим элементам индикации, информационные выходы узла моделирования полосы частот подключены к входам блоков логической коммутации первой группы и второму входу логического

30 блока, а информационные выходы узла моделей приемников связаны со входами блоков логической коммутации второй группы и вторым входом логического блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ко 660080, кл. G 09 В 23/00, 1975.

849279

Составитель С. Алексанов

Редактор Г. Волкова Техред А. Бойкас

Заказ 6100 67 Тираж 484 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, % — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4