Резервированный делитель частоты

Иллюстрации

Показать всеРеферат

Oll.ИСАКИИ

ИЗОВРЕТИН ИЯ, К АВТОРСКОМУ СВИДВТВЛЬСТВУ (ii>849497

Союз Сове к«мх

Социалистических

Мсттубпии (61) Дополнительное к авт. свид-ву № 645282 (22)Заявлено 05.10. 79 (21) 2825246/18-21 с.присоединением заявки № (5 I) М. Кл .

Н 03 К 23/02

Гаеударстеавньй юарт

СССР в делам изабратанал н атмритвй (23) Приоритет

Опубликовано 23.07.81. Бюллетень ¹ 27

Дата опубликования описания 25 .07 . 81 (53) УДК621. .374(088.8) (54) РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к автомати- ке и выЧислительной технике и может найти применение в высоконадежных цифровых синхронизирующих устройствах.

По основному авт. св. ¹ 645282 известен резервированный делитель частоты, содержащий три канала, каждый из которых состоит из счетчика импульсов на 3К-триггерах (счетчика), счетный вход первого из которых соединен с входной шиной мажоритарного элемента, входы которого соединены с выходами счетчиков каждого канала и логического элемента эквивалентности, входы которого соединены с выходами счетчика и мажоритарного элемента данного канала, а выход подключен к 3 и К входам первого 3К-триггера счетчика каждого канала 1).

Недостатком известного устройства является низкая надежность, обусловленная потерей работоспособности канала делителя на время цикла пересчета, следующего за циклом, в котором произошел сбой, приводящий к отставанию одного из каналов.

Цель изобретения — повышение надежности деления.

Поставленная цель достигается тем, что в резервированный делитель частоты, содержащий три канала, каждый из которых состоит из счетчика импульсов, 10 мажоритарного элемента и логического элемента эквивалентности, каждый канал дополнительно содержит синхронный двухступенчатый 0-триггер, дополнительт5 ный мажоритарный элемент, дополнительный элемент логической эквивалентности и элемент ИЛИ-НЕ, прйчем входы 0 и С синхронного двухступенчатого

0-триггера соединены соответственно с выходом и входом счетчика данного канала, выход синхронного двухступенчатого. 0-триггера соединен со входом дополнительного мажоритарного элемента, другие входы которого соединены

849497

3 с аналогичными выходами синхронных двухступенчатых О-триггеров соседних каналов, выход дополнительного мажоритарного элемента соединен со входом дополнительного элемента логической эквивалентности, другой вход которого соединен с выходом мажоритарного элемента, выход дополнительного элемента логической эквивалентности соединен со входом элемента

ИЛИ-HE другой вход которого соединен с выходом элемента логической эквивалентности, а выход элемента HJIH-НЕ соединен с 3 и К входами последнего

3К-триггера и с R входом остальных

3 К-триггеров счетчика данного канала.

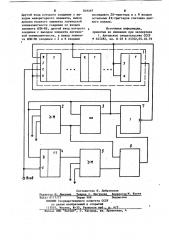

На чертеже изображена функциональная схема одного канала устройства.

Каждый канал состоит из счетчика 1, мажоритарного элемента 2, элемента 3 логической эквивалентности, синхронного двухступенчатого

D-триггера 4, дополнительного мажоритарного элемента 5, дополнительного элемента 6 логической эквивалентности, элемента 7 ИЛИ-НЕ.

Устройство работает следующим образом.

Если в результате сбоев в счетчике i одного из каналов последний разряд не изменяет своего состояния (недосчет), в то время как последние разряды с !етчиков 1 в двух других каналах изменяют свое состояние, элемент 3 логической эквивалентности в этом канале выдает блокирующий сигнал на первый триггер счетчика 1.

Выходы мажоритарного элеиента 2 и дополнительного мажоритарного элемента 5 различаются, так как выходы синхронных двухступенчатых О-триггеров 4 соответствуют состоянию последних разрядов счетчиков в предыдущем такте. Дополнительный элемент

6 логической эквивалентности также выдает блокирующий сигнал. В случае наличия двух блокирующих сигналов элемент 7 ИЛИ-НЕ выдает сигнал, разрешающий переключение последнего

3К-триггера и установку в "О" остальных 3К-триггеров счетчика 1 отстающего канала. Счетчики 1 всех трех каналов делителя приходят в идентичное состояние, блокирующий сигнал с выхода элемента 3 логической эквивалентности и сигнал сброса.и переключения с выхода элемента 7 ИЛИ-НЕ снимаются.

Таким образом, устройство повышает надежность деления за счет устранения сбоев, появившихся в одном из каналов, за время изменения состояния последнего разряда делителя, то есть в течение половины цикла пересчета.

В известном устройстве при блокировке счетчика 1 канала, в котором произошел сбой, он оста-!

О ется запертым до . тех пор, пока последние разряды счетчиков l двух других каналов вновь не изменят свое состояние.

После этого последний разряд счет-!

5 чика отставшего канала переходит в противоположное состояние раньше других, опять происходит блокировка счетчика 1 этого канала и только в момент последующего перехода послед20 них разрядов счетчиков 1 двух других каналов в новое состояние все три счетчика 1 приходят в идентичное состояние, т.е. в течение всего цикла пересчета, следующего за циклом, в

25 котором произошел сбой в одном из каналов, состояние этого канала отличается от состояния остальных каналов.

Если в течение этого цикла в одном из нормально функционирующих каналов

30 произойдет сбой, то изменится коэффициент деления резервированного делителя.

Формула изобретения

Резервированный делитель частоты по авт. св, У 645282, о т л и ч а юшийся тем, что, с целью повыше40 ния надежности деления, каждый канал дополнительно содержит синхронный двухступенчатый О-триггер, дополнительный мажоритарнь1й элемент, дополнительный элемент логической экви45 валентности и элемент HJIH-НЕ, причем входы О и С синхронного двухступенчатого О-триггера соединены соответственно с выходом и входои счетчика данного канала, выход синхронного.

50 двухступенчатого О-триггера соединен со входом дополнительного мажоритарного элемента, другие входы которого соединены с аналогичными выходами синхронных двухступенчатых О-.триг55 геров соседних каналов, выход дополнительного мажоритарного элемента соединен со входом дополнительного элемента логической эквивалентности, 5 849497 4 другой вход которого соединен с вы- последнего JK-триггера и с R входом ходом мажоритарного элемента, выход остальных 4К-триггеров счетчика дан-., дополн .тельного элемента логической ного канала. эквивалентности соединен со входом элемента ИЛИ-НЕ, другой вход которого Источники информации, соединен с выходом элемента логичес- принятые во внимание при экспертиэе кой эквивалентности, а выход элемен- 1. Авторское свидетельство СССР та ИЛИ-НЕ соединен с 2 и К входами У 645282, кл. Н. 03 К 23/02,05.10.79

Составитель Н. Дубровская

" давя М*

Заказ 6117/77 Тирак 988 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Ра ская наб. . 4/5 т „т л Хш т Я

Филиал ППП Патент г. Уллород, ул. Проектная, 4