Устройство для передачи и прие-ma дискретной информации

Иллюстрации

Показать всеРеферат

««849515

Сее» Советскик

Социалистических

Респубики

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОе СКОМУ СВИДЕТЕЛЬСТВУ

1 (61) Донолнительное к авт. свид-ву— (22)Заявлено 31.05.79 (21) 2772769/18-09

Э (5I )N. Кл:

Н 04 1. 1/10/1

Н 04 1. 3/02 с присоединением заявки.%Гееудееетееелые кемнтет

СССР (23) Прноритет— ае делам изебретеиий и етерытнй

Опубликовано 23,07 ° 81 ° Бюллетень И. 27

Дата опубликования описания 23.07.81 (53) Уд 621.394. .14 (088.8) (72) Автор изобретения

С.А.Осмоловский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА

ДИСКРЕТНОЙ ИНФОРМАЦИИ

Изобретение относится к связи и может использоваться при построении групповых устройств защиты от ошибок.

Известно устройство для передачи и приема дискретной информации, со5 держащее на передающей стороне последовательно соединенные регистр адреса, блок памяти, первый коммутатор, к управляющему входу которого подключен синхронизатор передачи и блок суммирования, к другому входу которого под ключен выход датчика параметров преобразования, а выход блока суммирования подключен к соответствующему входу регистра адреса» а на приемной сторо не — последовательно соединенные приемный регистр адреса, дополнительный блок памяти, второй коммутатор, управляющему входу которого подключен один из выходов синхронизатора приема, н блок вычитания, к другому входу ко-, торого подключен выход второго датчика параметров преобразования, а выход

>»: !ra вычитания блока подключен к соответствующему, входу приемного регистра адреса 11 .

Однако известное устройство обеспе чиваетт сравнительно невысокую достовер- ность передачи информации.

Цель изобретения — повышение досто.верности передачи .информации.

Для этого .в известное устройство на передающей стороне введены последовательно соединенные входной регистр исходной комбинации и. распределитель и последовательно соединенные регистр промежуточных результатов и блок свертки, при этом первый выход распределителя подключен к входу регистра адреса, второй выход ". к другому входу блока свертки, а к управляющему входу pacrtpeделителя подключен дополнительный выход синхронизатора передачи, дополнительный выход коммутатора подключен. к входу регистра промежуточных результатов, а на приемной стороне введены н=копительный регистр сдвига, выходы которого подключены к входам ключа

40

Формула изобретения

3 8495 и дополнительного блока суммирования, при этом выход дополнительного блока суммирования подключен к входу приемного регистра адреса, дополнительный выход второго коммутатора подключен к первому входу накопительного регистра сдвига, к управляющему входу которого и к управляющему входу ключа подключены соответствующие выходы синхронизатора приема. l0

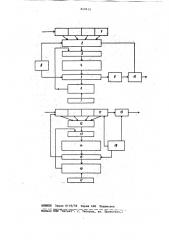

На чертеже приведена структурная электрическая схема пр едлагаемого уст- ройства.

Устройство для передачи и приема дискретной информации содержит на пе- 15 редающей стороне входной регистр 1 исходной комбинации, распределитель 2, регистр 3 адреса, блок памяти, первый коммутатор 5, блок 6 суммирования, датчик 7 параметров преобразования, син- 20 хронизатор 8 передачи, регистр 9 промежуточных результатов и блок 10 свертки, а на приемной стороне — накопительный регистр 11 сдвига, дополнительный блок 12 суммирования, приемный регистр 13 адреса, дополнительный блок 14 памяти, второй коммутатор

15„ блок 16 вычитания, второй датчик !

7 параметров преобразования, синхронизатор 18 приема и ключ 19.

Устройство работает следующим образом, Исходная комбинация импульсов по35 ступает в входной регистр 1, откуда с помощью распределителя 2 отрезки исходной комбинации поочередно поступают в регистр 3, после чего выполняется преобразование каждого отрезка., В процессе преобразования по адресу первого отрезка исходной комбинации иэ блока 4 считывается число, поступающее через первый коммутатор 5 в блок 6, где происходит суммирование

45 по модулю 2П поступившего числа с комбинацией преобразования. Результат суммирования поступает в регистр 3, считанный по этому адресу результат преобразования через первый коммутатор 5 записывается в регистр 9. Подоб50 ным образом преобразуются и другие отрезки исходной комбинации ° Реэуль— таты преобразования каждого отрезка из регистра 9 вместе с их непреобразо55 ванными значениями из распределителя 2 поступают в блок 10,,откуда результат свертки поступает на выход передающей стороны.

На приемной стороне в накопительном регистре !1 накапливаются принимаемые из канала (на чертеже не показан). преобразованные комбинации. Для полу-. чения исходной комбинации в дополнительном блоке 12 выполняется суммирование принятых комбинаций. Затем выполняется обратное преобразование по" лученной суммы, для чего эта сумма поступает в приемный регистр 13.. По .соответствующему адресу из дополни- . тельного блока 14 считывается число, поступающее через второй коммутатор

15 в блок !6, где происходит вычитание из него по модулю 2 формируемой вторым датчиком 17 комбинации. Полученный результат вычитания поступает в приемный регистр 13. В результате происходит считывание из дополнительного блока 14 комбинации результата преобразования, поступающей в накопительный регистр. 11. Из. накопительного регистра 11 через ключ 19 после преобразования всех отрезков комбинация результата преобразования поступает на выход.

После записи полученного результата в накопительный регистр 11, в котором после этого хранятся принятые комбинации и полученный результат по первому отрезку, выполняется их суммирование в дополнительном блоке 2, и цикл преобразования повторяется .

Предлагаемое устройство позволяет повысить достоверность передачи информации при сравнительно небольшом объеме памяти.

Устройство для передачи и приема дискретной информации, содержащее на передающей стороне последовательно соединенные регистр адреса, блок паМяти, первый коммутатор, к управляющему входу которого подключен синхронизатор передачи и блок суммирования, к другому входу которого подключен выход датчика параметров преобразова- ния, а выход блока суммирования подключен к соответствующему входу регистра адреса, а на приемной стороне — последовательно соединенные приемный регистр адреса, дополнительный блок памяти, второй коммутатор, к управляющему входу которого подключен один

5 849515 6

,из выходов синхронизатора приема, и ход коммутатора подключен к входу реблок вычитания, к другому входу кото- гистра промежуточных результатов, а рого подключен выход второго датчика на приемной стороне введены накопи- параметров преобразования, а выход тельный регистр сдвига, выходы котороблока вычитания подключен к соответ- го подключены к входам ключа и дополниствующему входу приемного регистра тельного блока суммирования, при этом адреса, о т л и ч а ю щ е е с я тем, выход дополнительного блока суммиро что, с целью повышения достоверности . вания подключен к входу приемного передачи информации, на передающей регистра адреса, дополнительный выход стороне введены последовательно сое- о второго коммутатора подключен к перводиненные входной регистр исходной ком- му входу накопительного регистра сдвибинации и распределитель и последова- га, к управляющему входу которого и к тельно соединенные регистр промажу- управляющему входу ключа подключены точных результатов и блок свертки, при соответствующие выходы синхронизатора этом первый выход распределителя под- )Б приема. ключен к входу регистра адреса, второй Источники информации, выход — к другому входу блока свертки, принятые во внимание при экспертизе а к управляющему входу распределителя 1. Авторское свидетельство СССР подключен дополнительный выход синхро- И 559417, кл. Н 04 L 1/10 1971 (пронизатора передачи, дополнительный вы- 20 тотип).