Преобразователь двоичного кода вдополнительный

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТИЛЬСТВУ

Союз Советских

Социалистических республик (61) Дополнительное к авт. сеид-ву— (22) Заявлено 10Ц279 (21) 2857801/18-24 с присоединением заявки М (23) Приоритет—

Опубликовано. 3007,81. Бюллетень Но 28

Дата опубликования описания 3007,81 (51)М. Кл з

G 06 F >/02

Государственный комитет

СССР по лелам изобретений и открытий (53) УДК б 81. 32 Ь (088.8) (72) Автор изобретения

В.И. Мяснов (71) заявитель (84 ) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В

ДОПОЛНИТЕЛЬНЫЯ

Изобретение относится к автомати. ке и вычислительной технике и может быть использовано в цифровых вычислительных машинах для преобразования двоичных чисел из прямого кода в дополнительный и обратно.

Известен преобразователь из прямого кода в дополнительный, содержащий триггерный регистр, две группы элементов И, входы которых соединены с единичными и нулевыми выходами триггеров регистра, и группу элементов

ИЛИ, выходы которых соединены со счетными входами триггеров регистра f1), Известный преобразователь имеет высокое быстродействие, однако имеет большое количество аппаратуры, связанное с наличием многовходовых элементов ИЛИ, Наиболее близким к предлагаемому является преобразователь двоичного кода в дополнительный, содержащий (n-1) одноразрядных сумматоров, где и — число разрядов преобразуемого кода, выходы суммы которых являются разрядными выходами преобразователя, а выход переноса 1-го fi - 1-(и-2 одноразрядного сумнатора соединен со входом переноса (i + 1)-ого одноразрядного сумматора. Кроме того, иэ- З1 вестный преобразователь содержит входной регистр и блок управления (2).

Недостаток данного преобразователя состоит в низком быстродействии, связанном с двухтактным принципом работы„ и большое количество аппаратуры.

Цель изобретения — увеличение быстродействия и упрощение преобразования.

Поставле иная цель достигается тем, что в преобразователе двоичного кода

B дополнительный, содержащем (и-1) одноразрядный сумматор, где и — число разрядов преобразуемого кода, выходи суммы которых являются разрядными выходами преобраэователя, выход пе р носа i-ro $i 1-(n-2)) .одноразрядного сумматора соединен со входом переноса (I + 1)-ого одноразрядного сумматора, первые в ходы всех однора.рядных сумматоров связаны с информационными входами преобразователя, младший разряд информационного входа преобразователя соединен со вторым входом первого одноразрядного сумнатора и является младшим разрядом выхода преобразователя, выход суьеы

i-го одноразрядного сумматора связан

851395

10011

+ 1

10101

10101

+ 0

10101

Формул а из обретения

Преобразователь двоичного кода в дополнительный, содержащий (n — 1 ) одноразрядных сумматоров, где п — число разрядов преобразуемого кода, выходы суммы которых являются разряд40 ными выходами преобразователя, а выход переноса <.-ro I i 1 — (n-2)1 одн ораз рядного с уммат ора соедине í со входом переноса (i + 1)-ого одноразрядного сумматора, о т л и ч а ю4 щ и ii c я тем, что, с целью увеличения быстродействия и упрощения устройства, в нем первые входы всех одноразрядных сумматоров соединены с информационными входами преобразователя

®0 младший разряд информационного входа, преобразователя соединен со вторым входом первого одноразрядного сумматора и является младшим разрядом выхода преобразователя, выход суммы

i-ro одноразрядного сумматора соединен со вторым входом (1 + 1)-oro од- норазрядного сумматора.

10101

+ 1

11101

Этап 4.

11101

+ 1

0,01101 ° со вторым входом (i + 1)-ого одноразрядного сумматора.

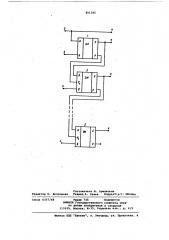

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь двоичного кода в дополнительный содержит полусуьиатор

1, одноразрядные сумматоры 2, информационные входы 3 и выходы 4 преобразов ателя.

Пусть задан прямой код двоичного числа (старший разряд - крайний слева; знаковый разряд не показан)

10011 . Операцию суммирования значений младшего разряда со значением соседнего старшего разряда для. наглядности производим по этапам.

Этап 1. Значение младшего (первого справа) разряда заданного кода, сдвинутого на один разряд в сторону старших разрядов, слагаем с исходным кодом

Этап 2. В почученном коде значение второго разряда, сдвинутого на один разряд в сторону старших разрядов, слагаем с исходным кодом

Этапы 3 и 4 осуществляются аналогично.

Этап 3.

Единица переноса из старшего разряда переносится в знаковый разряд, где нуль индицирует знак "+".

Данный алгоритм является модификацией алгоритма, реализуемого преобразователем (1) с тем различием, что инвертирование осуществляется последовательным прибавлением цифр каждого разряда единицы результата, сдвинутых на один разряд в сторону старших разрядов к значению исходного кода с учетом всех возникающих при этом переносов.

Преобразователь работает следующим образом.

При поступлении входного кода значение младшего разряда, не меня5

30 ясь, поступает на выход преобразователя, а значение второго разряда формируется на выходе сумьи полусумматора 1. Значения остальных разрядов выходного кода поступают на соответствующие разряды выходов 4 преобразователя с выходов сумм соответствующих одноразрядных сумматоров 2.

Эти значения получаются путем суммирования значений соседнего младшего разряда и переноса с него соответствующего разряда входного кода, которые поступают на входы этого сумматора. Сигнал переноса с выхода сумматора 2 старшего разряда выходного кода суммируется со значением знакового разряда. Перенос со знакового разряда теряется. Первый одноразрядный сумматор может быть заменен пол ус уммат ором.

Предлагаемый преобразователь позволяет произвести требуемое преобразование за один такт, чем и достигаетая ускорение преобразования, а также автоматически получить правильное значение знакового разряда. В известных преобразователях приходится искусственно инвертировать значение этого разряда. Крома того, предлагаемое устройство применимо как для преобразования прямого кода в дополнительный, так и наоборот, дополнительного кода в прямой.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

9 238225, кл. G .06 F 5/02, 1968.

2. Хилбурн Дж., Джулич П. МикроЭВМ и микропроцессоры. "Мир", 1979, с. 82, рис. 3.14 (прототип), 851395

I I

1i

Составитель М. Аршавскии

Редактор Н. Безродная .Техред А. Савка Корректс р С. Шекмар

Заказ 6357/68 Тирах 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская нас., д. 4/5

Филиал ППП "Патент", г. Уигород, ул. Проектная, 4