Преобразователь последовательногокода b параллельный

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<щ851 396 (61) Дополнительное к авт. сеид-ву (22) Заявлено 30.11.79 (21) 2845913/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 300781. Бюллетень Н9 28

Дата опубликования описания 30. 07. 81 рцм. к.з

G 06 F 5/04

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325 (088. 8) В.И. Дронов, И.Ю. Когге, А.В. Балаболин и М.С. Кудашов (72) Авторы изобретения

I (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА

В ПАРАЛЛЕЛЬНЫЙ

Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования последовательных двоичных кодов, поступающих по линии связи, в параллельный код.

Известен преобразователь последовательного кода в параллельный содержащий дешифратор, регистр сдвига, коммутатор, триггер режима, триггер выбора комбинации, счетный триггер, генератор тактовых сигналов, блок формирования сигнала "Конец кодовой комбинации", элемент задержки 11. t5

Недостаток этого преобразователя состоит в сложности схемного решения, что требует большого количества оборудования и снижает надежность работы преобразователя. 20

Наиболее близким к предлагаемому

rto технической сущности и схемному построению является преобразователь последовательного кода в параллельный 5 содержащий блок приемных регистров, распределитель импульсов и группу элементов И, входы которых соединены с разрядными выходами распределителя: импульсов, а выходы соединены с ин- 30 формационными входами блока приемных регистров (2) .

Недостаток такого преобразователя состоит в относительно низком быстродействии, связанном с тем, что он не обеспечивает непрерывного приема информации, поступающей из канала обмена по линии связи, в так« те работы канала обмена с вычислительным устройством, которое в процессе обработки информации сбрасывает ее в канал обмена, что снижает быстродействие канала обмена и требует наличия дополнительной памяти в канале обмена для хранения информации, поступающей с вычислительного устройства.

-Цель изобретения — увеличение быстродействия.

Указанная цель достигается тем, что в преобразователь последовательного кода в параллельный, содержащий блок приемных регистров, распределитель импульсов и группу элементов И, первые входы которых соединены с разрядными выходами распределителя импульсов, а выходы-соединены с информационными входами блока приемных регистров, введены. триггер записи, триггер подготовки, элемент ИЛИ, 851396 элемент НЕ и четыре элемента И,причем информационный вход преобразователя подключен к первым входам первого и второго элементов И и через элемент НЕ к первому входу третьего элемента И, вход синхроимпульсов преобразователя соединен со вторыми входами первого и второго элементов

И и с первым входом четвертого элемента И, выход первого элемента И подключен к синхровходу и -входу триггера записи, единичный выход ко, торого соединен с третьим входом второго элемента И и вторым входом четвертого элемента И, а нулевой выход подключен к третьему входу .первого элемента И, выход второго элемента И соединен со вторыми входами элементов И группы, выход четвертого элемента И подключен ко входу распределителя импульсов, последний разрядный выход которого подключен к первому входу элемента ИЛИ и к

3-входу триггера подготовки,единичный выход которого соединен со вторым входом третьего элемента И, выход которого подключен к управляющему входу блока приемных регистров, к

Й-входу триггера записи и к К -входу триггера подготовки, а также ко второму входу элемента ИЛИ, выход которого соЕдинен с синхровходом триг.гера подготовки.

Это позволяет передавать информацию со скоростью ее обработки в канале обмена и не требует наличия дополнительной памяти в канале обмена для хранения обработанной информации, поступающей с вычислительного устройства.

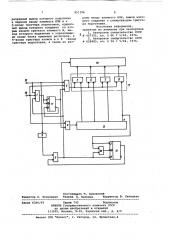

На чертеже представлена функциональная схема предлагаемого преобразователя, содержащего блок приемных регистров, обеспечивающий прием и четырехразрядных слов, поступающих в преобразователь в последовательном коде.

Преобразователь последовательного кода в параллельный содержит элементы И 1-8, элемент HE 9, элемент

ИЛИ. 10, триггер 11 записи, триггер

12 подготовки, распределитель 13 импульсов, блок 14 приемных регистров, информационный вход 15, вход 16 синхроимпульсов. Элементы И 5-8 образуют в совокупности группу элементов И 17.

Перед началом работы преобразователь приводится в исходное состояние.

В результате чего триггер 11 записи и трйггер 12 подготовки находятся в нулевом состоянии, в блоке 14 приемных регистров подготовлен к приему первый приемный регистр, а распределитель 13 импульсов подготав ливает к работе элемент И 5.

Преобразователь работает следующим образом, Каждое информационное слово, поступающее в последовательном коде на информационный вход 15 преобразователя, состоит из маркера слова и кодограммы, которые сопровождаются синхроимпульсами, поступающими на вход

16 преобразователя. При этом маркер слова следует перед кодограммой.

По приходу первого информационного слова на первый вход первого эле мента И 1 поступает маркер слова, 10 котсрый стробируется синхроимпуль- сом, поступающим со входа 16 преобразователя на второй вход первого элемента И 1. Первый элемент И 1, подготовленный к работе сигналом, noct5 тупающим с нулевого выхода триггера

11 записи, открывается и выдает на выходе сигнал, по заднему фронту которого триггер 11 записи переходит в единичное состояние, запрещая работу

Щ первого элемента И 1 и подготавливая к работе второй элемент И 2 для принятия кодограммы, следующей за .маркером, а также четвертый элемент И 4 для прохождения синхроимпульсов на вход распределителя 13 импульсов.

С этого момента начинается процесс принятия кодограммы, поступающей в последовательном коде, и преобразование-ее в параллельный код.

Принцип приема и преобразования передаваемой кодограммы рассмотрим на примере приема кодограммы 0101.

При поступлении первого. знака кодограммы, равного единице, на первый вход второго элемента И 2, стробируемого синхроимпульсом по второму входу, второй элемент И 2 открывается, и на его выходе появляется сигнал, который поступает на первые входы элементов И 5-8. Однако к рафЦ боте подготовлен только элемент И 5 сигналом, поступающим с первого выхода распределителя 13 импульсов.

Элемент И 5 открывается и выдает на выходе сигнал, по заднему фронту которого в первый разряд первого приемного регистра блока 14 приемных регистров записывается единица принимаемой кодограммы.

Синхроимпульс, сопровождающий у первый знак передаваемой жодограммы, поступает также через элемент И

4 на вход распределителя 13 импульсов,который по заднему фронту синхроимпульса переходит во второе положение, подготавливая к работе элемент И 6. На этом заканчивается процесс приема первого знака кодограммы.

Второй знак передаваемой кодограммы равен нулю, поэтому по приЩ ходу на второй вход элемента И 2 синхроимпульса сигнал на .выходе второго элемента И 2 отсутствует. Сигнал на выходе элемента И 6 также отсутствует. Следовательно, во втоЯ ром разряде первого приемного ре851396 гистра блока 14 приемных регистров подтверждается нуль принимаемой кодограммы.

Синхроимпульс, сопровождающий второй знак передаваемой кодограммы, поступает также через элемент И 4 на вход распределителя 13 импульсов, который по заднему фронту.синхроим= пульса переходит в третье положение, подготавливая к работе элемент И 7.

На этом заканчивается процесс приема второго знака кодограммы.

Прием третьего и четвертого знаков кодограммы аналогичен вышеописанному циклу.

В момент приема последнего знака кодограммы на последнем выходе распределителя 13 импульсов присутствует сигнал, который разрешает работу элемента И 8. Этот сигнал также поступает на 3 -вход и через элемент

ИЛИ 10 на синхровход триггера 12, 20 подготавливая его к работе. После приема последнего знака кодограммы распределитель импульсов по заднему фронту синхроимпульса переходит в исходное состояние, формируя разрешающий сигнал на своем первом выходе для работы элемента И 5. По заднему фронту сигнала с последнего выхода распределителя импульсов триггер 12 переходит в единичное состояние, под- 30 готавливая.к работе элемент И 3.Так как передача кодограммы первого передаваемого слова закончена, то сигнал с элемента НЕ 9, говорящий об отсутствии передаваемой информации, откры- З5 вает элемент И 3, и на его выходе формируется сигнал, по переднему фронту которого блок 14 приемных регистров подключает к выходам элементов И 5-8 второй приемный регистр, а триггер 11 записи переходит в нулеsoe, исходное состояние, запрещая работу элементов И 2 и 4 ° Кроме того, сигнал с выхода элемента И 3 поступает на k -вход и через элемент ИЛИ

10 на синхронход триггера 12, подго- 4 тавливая его к работе. На этом закаичивается прием первого информационного слова.

Прием второго информационного слова аналогичен вышеописанному циклу, щ за исключением того, что по переднему фронту маркера слова сигнал с элемента И 3 прекращается и триггер

12 подготовки по концу сигнала с элемента И 3 переключается в исходное, нулевое состоянке. Далее процесс принятия информационного слова аналогичен вышеописанному циклу.

Процесс приема и преобразования информационных слов, поступающих на,информационный вход 15 преобра- Щ зователя, продолжается до принятия из канала обмена по линии связи n-ro информационного слова.

Использование предлагаемого преобразователя обеспечивает расширение Я функциональных возможностей за счет непрерынного режима приема и преобразования информации, поступающей из канала обмена по линии связи, что позволяет передавать информацию из канала обмена по линии связи в предлагаемый преобразователь со скоростью ее обработки в канале обмена и не требует наличия дополнительной паияти в канале обмена для хранения обработанной информации, поступающей с вычислительного устройства. Кроме того, использование в предлагаемом преобразователе триггера записи, триггера подготовки, распределителя импульсов, блока приемных регистрон, которые изменяют свое состояние по заднему фронту управляющего сигнала, делает его не критичным к приходу передних фронтов синхроимпульсов и сигналов маркера слова и знаков кодограммы, а использонание маркера слова в составе передаваемого информационного. слова существенно упрощает преобразователь по приему и преобразованию информационных слов, содержащих нулевую информацию, а также информационных слов, первый передаваемый знак кодограммы которых равен нулю, что существенно повышает надежность и достоверность преобразованной информации.

Формула изобретения

Преобразователь последовательного кода н параллельный, содержащий блок приемных регистров, распределитель импульсов и группу элементов И, первые входы которых соединены с разрядными выходами распределителя импульсов, а выходы соединены с информационными входами блока приемных регистров, отличающийся тем, что, с целью увеличения быстродействия, н него введены триггер записи, триггер подготовки,, элемент

ИЛИ, элемент НЕ.и четыре элемента И, причем информационный вход преобразователя подключен к первым входам первого и второго элементов И и через элемент НЕ к первому входу третьего элемента И> вход синхроимпульсов преобразователя соединен со вторыми входами первого и второго элементов

И и с первым входом четвертого элемента И, выход первого элемента И. подключен к синхровходу и 3 -входу триггера записи единичный выход которого соединен с третьим входом второго элемента И и вторым входом четвертого элемента И, а нулевой выход подключен к третьему входу первого элемента И, выход второго элемента И соединен со вторыми входами элементов И группы, выход четвертого элемента И подключен ко входу распределителя импульсов последний

851396

Составщ рль М. варшавский

Редактор Н. Безродная Техред H. Келушак Корректор В. Синицкая

Заказ 6360/69

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Z(-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 разрядный выход которого подключен к первому входу элемента ИЛИ и к -входу триггера подготовки, единичный выход которого соединен со вторым входом третьего элемента И, выход которого подключен к управляющему входу блока приемных регистров, к

R-входу триггера записи и к k -входу триггера подготовки, а также ко второму входу элемента ИЛИ, выход которого соединен с синхровходом триггера подготовки °

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 407302, кл. G 06 F 5/04, 1974.

2. Авторское свидетельство СССР

Р 628485, кл. 6 06 F 5/04, 1976.