Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскии

Социалистических

Реслублик

Оп ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ («)851491 (61) Дополнительное к авт. свид-ву— (22) Заявлено 16.05.79 (21) 2765991/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

G 11 С 11/00

Гееударствеиимй камитет йо делам изебретеиий и открытий

Опубликовано 30.07.81. Бюллетень № 28

Дата опубликования описания 05.08.81 (53) УДК 681.327..6 (088.8) Ю. А. Трофимов, Л. А. Гелюх и Г. Б. Мелешко., 1

1„; ",- 1т : . „ » - др (72) Авторы изобретения (71) Заявитель (54) ЗАПОМИНАЮШЕЕ УСТРОИСТВО

Изобретение относится к запоминающим устройствам и может быть использовано в системах отображения, передачи и обработки дискретной информации.

Известны запоминающие блоки и устройства, содержащие накопители с непрерывным обращением к адресам, необходимые для отображения записанной в запоминающем устройстве (ЗУ) информации и индикаторе (1).

Недостатком этих устройств является их сложность. î

Наиболее близким к предлагаемому является устройство, содержащее накопитель, адресный счетчик, счетчик записи, формирователь разрешения записи, элементы И и

ИЛИ, В этом устройстве происходит непрерывное последовательное обращение к адресам накопителя и непрерывное считывание информации, отображаемой на индикаторе.

Причем, для запоминания адреса места записи в накопителе и подсветки его в индикаторе используется фазовый признак (2).

Недостатком известного устройства является малый объем памяти, непревышающий емкости индикатора.

Цель изобретения — увеличение информационной емкости устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, информационные входы которого являются информационными входами устройства, счетчик адреса, выходы которого подключены к адресным входам первой группы входов накопителя, тактовый вход и вход установки счетчика адреса подключены соответственно к первой тактовой шине и к шине установки, счетчик записи, выходы которого подключены к входам первого элемента И, а вход установки счетчика записи подключен к шине установки, формирователь, первый и второй входы которого подключены соответственно к первой управляющей и второй тактовой шинам, управляющий вход формирователя подключен к второй управляющей шине, а его первый и второй выходы подключены соответственно к первому входу второго элемента И и к первому входу первого элемента ИЛИ, второй вход второго элемента И подключен к первой тактовой шине, а его выход — к второму входу первого элемента ИЛИ, вы85149 з ход которого подключен к тактовому входу счетчика записи, дополнительно введены реверсивный адресный счетчик, выходы которого подключдцы к адресным входам второй группы входов накопителя, а вход установки подключе :-к шинЕ установки, третий 5 элемент И, первый вход которого подключен к второй управляющей шине, а его выход— к управляющему входу накопителя, четвертый и пятый элементы И, первые входы которых подключены соответственно к второму и к первому входам формирователя, второй и третий элементы ИЛИ, первые входы которых подключены соответственно к выходам четвертого и пятого элементов И, вторые входы — соответственно к второй и третьей управляющей шинам, а входы второго и треть@6 элементов ИЛИ подключены соответственно к первому и к второму входам реверсивного адресного счетчика, дешифратор, входы которого подключены к выходам счетчика адреса, первый и второй выходы подключены к вторым входам четвертого и пятого элементов И, выход первого элемента И подключен к третьим входам четвертого и пятого элементов И, к синхронизирующему входу формирователя и к второму входу третьего элемента И.

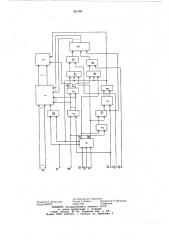

На чертеже приведена блок-схема устройства.

Запоминающее устройство содержит накопитель 1, счетчик 2 адреса, дешифратор 3, формирователь 4, счетчик 5 записи, ревер- зо сивный адресный счетчик 6, блок 7 управления индикатором, первый элемент И 8, второй элемент И 9, третий элемент И 10, четвертый элемент И 11, пятый элемент И 12, первый элемент ИЛИ 13, второй элемент ИЛИ

14, третий элемент ИЛИ 15, информационные шины 16, шину 17 управления (записи), первую тактовую шину 18, управляющую шину 1с1 (редактирования), шину 20 управления (Вычитания), вторую тактовую шину 21, управляющую шину 22 (установки), 40 управляющую шину 23 (вычитания) и управляющую шину 24 (прибавления), выход

25 вычитания формирователя, выход 26 добавления формирователя, выход 27 последнего знака дешифратора, выход 28 первого знака дешифратора. 45

После подачи сигнала установки по шине 22 адресный счетчик 6 и счетчик 5 записи находятся в одинаковом фазовом состоянии и синхронно переключаются под воздействием тактовых импульсов, поступающих на так50 товые входы по шине 18 первого такта. Коэффициенты счета обоих счетчиков одинаковые и, обычно, равны емкости индикатора. На первую группу адресных входов накопителя 1 поступают коды адреса знаков первой строки (так как счетчик 6 установлен в

«О» — первая строка) и на выходах накопителя 1 появляется соответствующая ин4 формация, хранимая по этим адресам в накопителе.

Эта информация поступает в блок 7 управления индикатором и отображается на индикаторе (не показан). Место записи информа ции определяется фазой счетчика 5 (например. -момент,,когда все разряды счетчика 5 находятся в состоянии «О»), а. импульс записи вырабатывается первым элементом И 8.

Момент обрабатывания элемента И 8 в исходном состоянии соответствует первому адресу счетчика 2 и при поступлении на шину 17 записи разрешающего сигнала в первый адрес накопителя запишется код знака, поступающего по информационным шинам 16.

После окончания сигнала по шине 17 записи срабатывает формирователь 4 и на выходе 25 вычитания появляется сигнал, запрещающий прохождение одного импульса первого такта через элемент И 9 на .тактовый вход счетчика 5. При этом изменяется на шаг фаза счетчика 5 по отношению к фазе счетчика 2 (запаздывание). Импульс записи вырабатывается элементом И 8 уже в момент, когда на выходах адресного счетчика 2 находится код второго адреса. При поступлении второго сигнала записи новый знак запишется по второму адресу, а по окончании сигнала записи вновь срабатывает формирователь 4, на выходе 25 появляется сигнал вычитания, запрещающий прохождение еще одного импульса первого такта через элемент И 9 на вход счетчика 5.

При этом фаза счетчика 5, а значит место записи нового знака сдвинется еще на шаг.

Дальнейшая -работа устройства при записи происходит аналогично. После записи предпоследнего знака фаза счетчика 5 соответствует адресу последнего знака строки. Сигнал, вырабатываемый элементом И 8, совпадает при этом по времени с сигналом последнего знака, вырабатываемом дешифратором 3, и поступающим с выхода. 27 на вход элемента И 12.

При записи еще одного знака сигнал вычитания с выхода 25 формирователя поступает на вход элемента И 9 и запрещает прохождение одного импульса первого такта на тактовый вход счетчика 5, а также на вход элемента И 12. Этот сигнал совпадает по времени с сигналом элемента И 8, за счет синхронизации формирователя этим сигналом и с сигналом, вырабатываемым дешифратором 3 по выходу 27. На выходе элемента И 12 появля ется сигнал, поступающий через элемент ИЛИ 15 на вход сложения реверсивного адресного счетчика 6. Код адреса строк изменяется на один шаг, и адресным счетчиком 2 выбирается новая строка.

При подаче на шины вычитания 23 и прибавления 24 импульсов счетчик 6 из851491 меняет свое состояние, увеличивая или уменьшая номера индицируемых строк.

При подаче каждого импульса по какойлибо шине 23 или 24 будет выбираться и индицироваться новая строка.

Для индикации места записи информации сигнал с выхода элемента И 8 подается на управляющий вход блока 7, где используется для подсветки места записи..С помощью сигналов по шинам 19 и 20 редакции можно изменять фазовОе =:.состоя 4, ние счетчика 5 записи путем вычитания импульсов первого такта сигналами вычитания с выхода 25 формирователя или путем добавления импульсов второго такта, поступающих с выхода 26 добавления через элемент ИЛИ 13 на тактовый вход счетчика 5.

Если фазы счетчиков 5 и 2 одинаковы, то сигнал элемента И 8 совпадает по времени с сигналом первого знака с выхода 28 дешифратора 3, При этом, появление импульса добавления с выхода 26 формирователя, совпадающего по времени с импульсом элемента И 8, приводит к появлению импульса на выходе элемента И 11 и уменьшению кода числа, хранимого в счетчике 6. Таким образом, сигнал элемента И 8 не только указывает место записи, но и разрешает сдвиг счетчика 6 при сдвигах места записи знака за пределы одной строки. Границы строки отмечает дешифратор 3.

Введение в устройство дополнительных элементов и связей позволяет увеличить ЗО объем хранимой и индицируемой информации до любой требуемой величины. При разрядности адресного счетчика, равной и, число хранимых в накопителе строк равняется К=2

Формула изобретения

Запоминающее устройство, содержащее накопитель, информационные входы которого являются информационными входами усройства, счетчик адреса, выходы которого подключены к адресным входам первой группы входов накопителя, тактовый вход и вход установки счетчика адреса подключены соответственно к первой тактовой шине и к 45 шине установки, счетчик записи, выходы zd торого подключены к входам первого элемента И, а вход установки счетчика записи подключен к шине установки, формирователь первый и второй входы которого подключены соответственно к первой управляющей и второй тактовой шинам, управляющий вход формирователя, подключен к второй управляющей шине, а его первый и второй выходы подключены соответственно к первому входу второго элемента И и к первому входу первого элемента ИЛИ, второй вход второго элемента И подключен к первой тактовой шине, а его выход — к второму входу первого элемента ИЛИ, выход которого подключен к тактовому входу счетчика записи, отличающееся тем, что, с целью повышения информационной емкости устройства, в него введены реверсивный адресный счетчик, выходы которого подключены к адресным входам второй группы входов накопителя, а вход установки подключен к шине установки, третий элемент И, первый вход которого подключен к второй управляющей шине, а его выход — к управляющему входу накопителя, четвертый и пятый элементы И, первые входы которых подключены соответственно к второму и к первому входам формирователя, второй и третий элементы ИЛИ, первые входы которых подключены соответственно к выходам четвертого и пятого элементов И, вторые входы — соответственно к второй и третьей управляющим шинам, а. входы второго и третьего элементов ИЛИ подключены соответственно к первому и к второму входам реверсивного адресного счетчика, дешифратор, входы которого подключены к выходам счетчика адреса, первый и второй выходы подключены к вторым входам четвертого и пятого элементов И, выход первого элемента И подключен к третьим входам четвертого и пятого элементов И, к синхрозирирующему входу формирователя и к второму входу третьего элемента И.

Источники информации, принятые во внимание при экспертизе

1. Одуло В. Д. и др. Полупроводниковая буферная память системы отображения алфавитно-цифровой информации. Вопросы радиоэлектроники. Серия ЗВТ, вып. 12, 1975.

2. Авторское свидетельство СССР № 643973, кл. G 11 С 11/00, 1976 (прототип) .

851491

Составитель В. Гордонова

Редактор Е. Дичинская . Техред А. Бойкас Корректор Н. Швыдкая

Заказ 6368I73 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4