Коммутатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОВРИтИНИЯ

К . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советеимл

Социвпиетичееиик

Республик

1и 851 772

f 61) Дополнительное к авт. свид-ву (22) Заявлено 10. 10. 79(21) 2829786/18-21 (51)М. К

Н 03 К 17!04/)

H 04 J 3/00 с присоединением заявки М

1Ьеударствеллыб кемнтет

СССР

lo делам лэабретений к еткрмтлй (23)Приоритет

Опубликовано 30.07.81. Бюллетень М28

{53) УД К 681, 32 (088.8) Дата опубликования описания 3 1.07.81 (72) Автор изобретения

В. А. Авдеев

Г

Таганрогский радиотехнкчес .институт им. В. Д. Еальчыкова 1 (7l ) Заявитель.. (54) КОММУТАТОР! . Изобретение относится к коммута» ционной технике.

Известны коммутаторы, содержащие блок сопряжения, блок управления и адресный блок, а также в каждовт ка: нале - блок элементов И-ИЛИ, пешифратор, регистр и блок памяти,(1).

: Наиболее близким по технической сущности к предлагаемому является коммутатор, содержащий блок сопряжения, первая группа входов которого

10 соединена с управляющими .шинами, вторая группа входов — с .первой группой выходов блока управления, входы которого соединены с первой группой

l$ выходов блока сопряжения, вторая группа выходов которого подключена к информационным входам адресного блока, а также в каждом канале — блок элементов И-ИЛИ,дешифратор, регистр и блок камятк, адресные входы которого соединены с выходами адресного блока, информационные входы — с вы1 ходами одноименного регистра, первая

2 ! групт1а информационных входов которого объединена с первыми группамн информационных входов регистров другах каналов и подключена к третьей группе выходов блока сопряжения, а вторая группа информационных выходов соединена с выходаэж одноименного блока haмяти, вторая группа выходов блока управления подключена к управляющим входам блоков памяти, регистров к дешифраторов всех каналов и управляющим входам адресного блока, при этом выходы блока элементов И"ИЛИ последующего канала соедкнены с основными информационнымк входами блока -элементов И-ИЛИ предыдущего канала, а выходы блока элементов И-ИЛИ первого канала подключены к выходным шкнамф).

Недостатком известных устройств является нкзкае быстродействие.

Цель изобретения — повышение быст родействия коммутатора.

Указанная цель достигается тем, что в коммутаторе в каждом канапе

3 85177 выходы регистра соединены с икформационными входами дешифратора, выходы которого подключены к первым управляющим входам всех блоков элементов

И-ИЛИ, вторые управляющие входы кото-. рых соединены с выходами адресного блока, а дополнительный информационный вход каждого блока элементов ИKIH соединен с одноименной янформационной входной шиной.

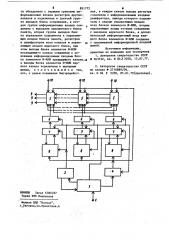

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит блок l сопряжения, первая группа входов которого соединена с управляющими шинами 2, а. вторая группа — с первой группой выходов блока 3 управления,, входы которого соединены с первой группой выходов блока 1 сопряжения, вторая группа выходов которого подключена к информационным входам адресного блока 4. В каждом канале имеются блок

5 элементов И-ИЛИ, дешифратор 6, регистр 7 и блок 8 памяти, адресные входы которого соединены с выходами адресного блока 4, информационные входы — с выходами одноименного регистра 7, первая группа информационных входов которого объединена с первыми группами информационных вхо30 дов регистров 7 других каналов и подключена к третьей группе выходов блока 1 сопряжения, а вторая группа информационных входов соединена с выходами одноименного блока 8 памяти.

Вторая группа выходов блока 3 управления подключена к управляющим входам блоков 8 памяти, регистров 7 и дешифраторов 6 всех каналов и управляющим входам адресного блока 4. Вы40 ходы блока 5 элементов И-ИПИ последующего канала соединены с основными информационными входами блока 5 элементов И-ИЛИ предыдущего канала, а выходы блока 5 элементов И-ИЛИ пер45 вого канала подключены к выходным шинам 9, В каждом канале выходы регистра 7 соединены с информационными входами дешифратора 6, выходы которого подключены к первым управляющим вхо30 дам всех блоков 5 элементов И-ИЛИ, вторые управляющие входы которых соединены с выходами адресного бло-. ка 4, а дополнительный информационный вход каждого блока 5 элементов

И-ИЛИ - с одновременной информационной входной шиной 10.

Устройство работает следуюшим образом.

2 4

Все rn выходных шин 9 разбиты на К групйпо п выходных шин в каждой группе. Каждый блок 8 памяти содержит И60 Ь -разрядных ячеек памяти и предназначен для хранения программы коммутации соответствующей группы выходных шин 9. Так как подключение двух и более информационных входных шин 10 к одной выходной шине 9 является недопустимым соединением, то в каждой ячейке блока 8 памяти записывается код соедчнения некоторой информационной входной шины с какой-либо одной выходной шиной. Ввод программы коммутации в блоки 8 памяти осуществляется через управляющие шины 2 через блок 1 сопряжекия и регистры 7, при этом выбор требуемого блока памяти осуществляется при помощи адресного блока 4. Каждый элемент И блока 5 элементов И-HJIH некоторого канала разрешает прохожде« ние информации с информационной входной шины 10 этого канала на соответствующую выходную шину 9 при нали-чии разрешающих. сигналов с выходов соответствующего дешифратора 6 и.адресного блока 4, определяющих, соответственно, передачу информации от инфориационкой входной шины 10 ка группу выходных шин 9, программа коммутации которых хранится в одноимекI ном этому дешифратору 6 блоке 8 памяти, и передачу информации на тре- буемую выходную шины. Логические элементы ИЛИ блоков 5 элементов ИИЛИ объединяют соответствующие выходы элементов И для каждой одноименной.выходной шины 9. формула изобретения

Коммутатор, содержащий блок сопряжения, первая группа входов которого соединена с управляющими шинами, вторая группа входов †. с первой группой выходов блока управления, входы которого соединены с первой группой выходов блока сопряжения,.вторая группа выходов которого подключена к информационным входам адресного блока, а также в каждом канале — блок . элементов И -ИЛИ,дешифратор, регистр и блок памяти,: адресные входы которого соединены с выходами адресного блока, информационные входы - с вы-! ходами одноименного регистра, первая группа информационных входов котороВНИИПЦ

Тиран

5 851772 го объединена с первыми группами информационных входов регистров других., каналов и подключена к третьей груп-:.

- пе выходов блока сопряюения, а вторая группа информационных входов соединена с выходами одноименного блока памяти, вторая группа выходов бло ка управления подключена к управляющим входам блоков памяти, регистров и дешифраторов всех каналов и управ- 1е ляющим входам адресного блока, при этом выходы блока элементов И-ИЛИ последующего канала соединены с основными информационными входами бло-. ка элементов И-ИЛИ предыдущего канала, у а выходы блока элементов И ИЛИ первого канала подключены к выходным шинам, о т л н ч а ю шийся тем, что, с целью повышения быстродейстФилиал ППП "Патент", г. Уагород,ул. Проектная,4 б вня, в кащдом канале выходы регис тра соединены с информационными входами дешифратора, выходы которого подклю" чены к первым управляющим входам всех блоков элементов И-ИЛИ, вторые управляющие входы которых соединены с выходами адресного блока, а дополнительный информационный вход каждого блока элементов И-ИЛИ соединен с одноименной информационной входной шиной.

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР

В 563732 ° хл. К 04 3 3/00, 15 07.77.

2. Авторское свидетельство СССР по заявке В 2710889/09, кл. Н 04 У 3/00, 05.0I.79(èðîòîòèï).