Устройство дискретной автоподстройкифазы тактовых импульсов b системахсвязи

Иллюстрации

Показать всеРеферат

Союз Советских . Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 18. 09. 79 (21) 2817299/18-09 (51) + с присоединением заявим М9 (23) Приоритет

H L 7/02

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 07.08,81. Бюллетень ¹ 29

Дата опубликования описания 08. 08. 81 (53) УДК 621. 394. .662.2 (088.8) (72) Авторы изобретения

В.Г. Балакай, Т.В. Пушкина и Г.А. Кратистова (71) Заявитель (54) УСТРОЙСТВО ДИСКРЕТНОЙ АВТОПОДСТРОЙКИ ФАЗЫ

TAKT0B6IX ИМПУЛЬСОВ В СИСТЕМАХ СВЯЗИ

Изобретение относится к технике передачи дискретной информации в сис. темах связи и может использоваться в асинхронных системах связи.

Известно устройство дискретной автоподстройки фазы тактовых импульсов в системах связи, содержащее последовательно соединенные генератор исходных частот и реверсивный счетчик, а также фазовый дискриминатор, 1) .

Однако известное устройство обладает низким быстродействием.

Цель изобретения — повышение скорости автоподстройки.

Для этого в устройство дискретной автоподстройки фазы тактовых импульсов в системах связи, содержащее последовательно соединенные генератор исходных частот и реверсивный счетчик, а также фазовый дискриминатор, введены блок управляемых задержек и преобразователь фаза-код, вход которого соединен с выходом фазового дискриминатора, соответствующие входы которого соединены с соответствующими выходами реверсивного счетчика, другие выходы которого подключены к соответствующим входам блока управления задержек, другие входы которого соединены с выходами преобразователя фаза-код, при этом один из входов фазового дискриминатора соединен с одним из входов блока управления задержек, а на один из соответствующих входов фазового дискриминатора поданы информаЦионные посылки. Кроме того, блок управляемых задержек содержит и управляемых задержек,,включенных последовательно друг с другом, каждая из которых содержит последовательно соединенные триггер и коммутатор, входы которых являются входами блока .IS управляемых задержек,,а выход последней задержки — выходом всего устройства.

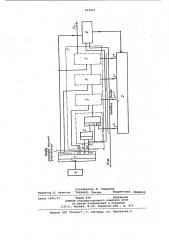

На чертеже приведена структурная

20 электрическая схема устройства автоподстройки фазы тактовых импульсов в системах связи.

Устройство содержит реверсивный счетчик 1, блок 2 управляемых задержек, содержащий и управляемых задержек 3, каждая из которых содержит триггер и коммутатор, генератор 4 исходных частот, преобразователь 5

30 фаза-код и фазовый дискриминатор 6.

853811

Устройство работает следующим образом.

Пусть на входе информационной машины присутствует фронт информации, смещенный относительно фронта тактовой частоты Е - на величину с.

В первом такте с помощью дискриминатора 6 определяется величина рассогласования. Во втором такте в преобразователе 5 "фаза-код" формируется параллельный и-разрядный код, как эквивалент этого смещения. Этот код поступает на блок 2 управляемых задержек. Смещение тактовой частоты на величину осуществляется так: пусть, например, на третий вход и-ного разряда узла управлямой задержки 3 поступает логическая "1".

В этом случае коммутатор узла пропустит частоту, поступающую на первый вход коммутатора, т.е. частоту 2f>, задержанную на такт частоты 2f При наличии "0" на третьем входе коммутатора последний пропускает частоту, поступающую на

ere второй вход, т.е. частоту, не задержанную. Аналогично работают остальные задержки блока 2 управляемых задержек. В и-1 разряде управляемой задержки 3 осуществляется задержка на такт частоты 4 f и т.д. по двоичному закону. Таким образом, в соответствии с двоичным кодом, поступающим с преобразователя 5 фаза-код, подстроенная частота устанавливается синфазно с информационным фрон1 том с точностью до -„ где и — число разрядов. данное устройство позволяет повысить быстродействие по сравнению с известными ус гройствами более чем на порядок.

Формула изобретения

1. Устройство дискретной автоподстройки фазы тактовых импульсов в системах связи, содержащее последовательно соединенные генератор исходных частот и реверсивный счетчик, а также фазовый дискриминатор, о т л и ч а ю щ е е с я тем, что, с целью повышения скорости автоподстройки, введены блок управляемых задержек и преобразователь фаза-код, вход которого соединен с выходом фазового дискриминатора, соответствующие входы которого соединены с соответствующими выходами реверсивного счетчика, другие вы 5 ходы которого подключены к соответствующим входам блока управления задержек, другие входы которого соединены с выходами преобразователя фаза-код, при этом один из входов

Щ фазового дискриминатора соединен с одним из входов блока управления задержек,а на .один из соответствующих входов фазового дискриминатора поданы информационные посылки. д 2. УстрОистВО пО п.1, О т л ич а ю щ е е с я тем, что блок управляемых задержек содержит и управляемых задержек, включенных последовательно друг с другом, каждая из которых содержит последовательно соединенные триггер и коммутатор, входы которых являются входами блока управляемых задержек, а выход послед, ней задержки — выходом всего устройства.

35 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

598260, кл. Н 04 4 7/02,1976 (прототип).

853811

Составитель В. Смирнова

Редактор Б. Федотов ТехредЛ. Пекарь КорректоРК. Швыдкая

Заказ 5696/33 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4