Устройство для приема многопозиционныхсложных сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналкстнчеснкх

Реслублин

oi>853819 (61) Дополнительное к авт. свмд-ву (22) Заявлено 29.1179 (21) 2846779/18-09 с присоединением заявки И9 (23) Приоритет

Опубликовано070881. Бюллетень М29

Дата опубликования описания 09.0881

Н 04 L 27/28

Государственный комнтет

СССР по делам нзобретеннй н открытий (5Я Уд((621. 394.627 (088. 8) (72) Авторы изобретения

В.В.Барлабанов, A.A,Ëèïàòàâ, А ° А.Паламарчук, А,.È.Ñåìåíêî, В,Д.Ушакоз и М.А.Хмелевский с

-- /

I (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОПОЗИЦИОННЫХ СЛОЖНЫХ

СИГНАЛОВ

Изобретение относится к электро" связи и может быть использовано в системах передачи дискретных данных при приеме многопозиционных сложных сигналов, образуемых постоянным числом элементов, выбранных из биортогонального ансамбля.

Известно устройство для приема многопозиционных сложных сигналов, содержащее последовательно соединенные генератор тактовых импульсов и счетчик, выходы которого подключены ко входам коммутатора выходы которого подключены к первым входам элементов равнозначности, вторые входы 15 и выходы которых соединены соответственно с выходами регистра сдвига и входами сумматора, а- также блок памяти и пороговый блок, выход которого подключен к первому входу регистра 2О сдвига (1).

Однако помехоустойчивость такого устройства невысока.

Цель изобретения — повьааение помехоустойчивости устройства 25 Цель достигается тем, что в устройство для приема многопозиционных сложных сигналов, содержащее последовательно соединенные генератор тактовых импульсов к счетчик, выходы 3g которого подключены ко входам коммутатора, выходы которого подключены к первым входам элементов равнозначности, вторые входы которых и выходы соединены соответственно с вы одами регистра сдвига и входами сумматора, а также блок памяти и пороговый блок, выход которого подключен к первому .входу регистра сдвига, введены два инвертора, буферный регистр, делитель, регистр информации и компаратор, входы которого соединены с входами и выходами блока памяти и выходами первого инвертора, к информационным входам которого подключены выходы сумматора, соответствующий выход которого соединен с управляющими входами инверторов и буферного регистра, выходы которого подключены ко входам регистра информации, соответствующие входы которого соединены с дополнительным входом блока памяти, вторым выходом генератора тактовых импульсов и выходом делителя, вход которого соединен с соответствующим выходом счетчика, входом порогового блока и вторьы входом регистра сдвига; при этом выходы счетчика подключены к информациснныч входам второго инвертора, выходы которого с.оелннены r:o

853819 входами буферного регистра, управляющий вход которого соединен с выходом компаратора и управляющим входом блока памяти.

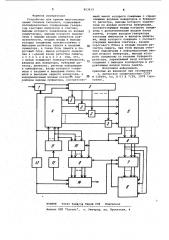

На чертеже приведена структурная электрическая схема описываемого уст,ройства.

Данное устройство для приема многопозиционных сложных сигналов содержит пороговый блок 1, регистр 2 сдвига, элементы 3 равнозначности, коммутатор 4, сумматор 5, инвертор 6, блок 7 памяти, компаратор 8, буферный регистр 9, инвертор 10, счетчик 11, генератор 12 тактовых импульсов, делитель 13 и регистр 14 информации, Устройство работает следующим образом, Входной сигнал, несущий информацию, представляет собой многопозиционный биортогональный код длиной Н который строят так, чтобы свести к 20 минимуму ошибки в информационной последовательности, Например, для передачи информации пачками по пять информационных символов требуется 2 = 2щ =

=32 сигнала, из которых 16 прямых и 25

16 противоположных. При этом, если кодовые комбинации 00000, 01110 00111 передаются сигналами S„, S S> то комбинации, им противоположные 11111, 10001, 11000 †сигналами Б, Sgi Я9

Принимаемый сигнал поступает на вход порогового блока 1, где преобразуется в импульсную последовательность, которая записывается регистром 2 сдвига тактовыми импульсами счетчика 11.

С первого выхода регистра 2 сдвига сигнал поступает на вход первого элемента 3. равнозначности, на второй вход которо-о поступает сигнал с первого выхода коммутатора 4. Коммутатор

4 за период следования информационных 40 посылок биортогонального кода подает

m опорных кодов. С выхода первого элемента 3 разнозначности сигнал (единица при совпадении сигналов на первых выходах регистра и коммута- yg тора и нуль -при несовпадении) поступает на первый вход сумматора

5, Сумматор преобразует число совпадений между принятыми и опорными сиг- щ налами в параллельной двоичной код

При этом 1 на выходе старшего разряда сумматора 5 говорит о приеме прямого кода, а 0 — о приеме обратного. Для выбора максимального сигнала из ансамблю биортогональных кодов выходы младших разрядов двоичного кода числа совпадений сумматора подключены к входам инвертора 6, в котором в случае приема обратного кода по сигналу 0 с выхода стар- Щ щего разряда сумматора 5, подключенного к управляющему входу инвертора

6» двоичный код числа совпадений инвеютиючется,.Например, комбинация

11110,говорит о том, что принят пря фЯ мой код с одной ошибкой, а комбинация 00001 — о том, что принят обратный код с одной ошибкой. На выходе инвертора 6 отклик на первый и второй сигналы будет один — 1110. С выхода инвертора 6 двоичный код поступает на параллельные входы блока 7 памяти и комнаратора 8, В начале цикла обработки ячейки блока 7 памяти находятся в нулевом состоянии, запись информации в него происходит по сигналу с выхода компаратора 8, который появляется только в случае, если поступивший код больше хранящегося в блоке 7, Этот >ке сигнал с выхода компаратора 8 подается на вход разрешения записи буферного регистра 9 для записи информационного кода. Счетчиком 11 формируЮтся разряды информационного кода, которые являются также управляющими сигналами коммутатора 4. В случае приема прямого сигнала соответствующий ему код информационных импульсов проходит инвертор 10 без изменений и записывается в буферный регистр 9 по сигналу с выхода компаратора 8, В последний разряд буферного регистра записывается единица с выхода старшего разряда сумматора

5. При приеме обратного кода комбинация информационного кода с выхода счетчика 11 инвертируется инвертором

10 по сигналу старшего разряда сумматора, а в последний разряд буферного регистра 9 записывается 0 с выхода старшего разряда сумматора.

После окончания N тактов в буферном регистре 9 будет записан код посылки информационных импульсов, соответствующий максимуму взаимной корреляционной функции принятого сигнала и одного из m опорных кодов. Эта комбинация считывается в регистр 14 информации сигналом, поступающим с делителя 13, который также устанавливает в нулевое состояние блок 7 памяти, В течение следующего цикла работы устройства, который длится N периодов тактовой частоты регистра

2 сдвига, информация с выхода регистра 14 информации поступает к потребителю.

Использование описанного устройства для приема многопозиционных сигналов позволит повысить помехоустойчивость приема передаваемой информации в каналах с малым отношением сигнал-шум или увеличить скорость передачи информации без расширения полосы пропускания при достаточной мощности.радиолинии. Это устройство сравнительно просто реализуется с помощью цифровых интегральных схем и не требует создания сложных устройств цикловой синхронизации, 853819

ВНИИПИ Заказ 5698/34 Тираж 698 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Формула изобретения

Устройство для приема многопозиционных сложных сигналоз, содержащее последовательно соединенные генератор тактовых импульсов и счетчик, выходы которого подключены ко входам 5 коммутатора, выходы которого подключены к первым входам элементов равнозначности, вторые входы и выходы которых соединены соответственно с выходами регистра сдвига и входами сумматора, а также блок памяти и пороговый блок, выход которого подключен к г.ервому входу регистра сдвига, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены два инвертора, буферный регистр, делитель, регистр информации и компаратор, входы которсго соединены с входами .и выходами блока памяти и выходами первого инвертора, к информационным входам которого подключены выходы сумматора, .соответству-! ющий выхол которого соединен с управляющими входами инверторов и буферного регистра, выходы которого подключены ко входам регистра инФормации, соответствующие входы которого соединены с дополнительным входом блока памяти, вторым выходом генератора тактовых импульсов и выход м делителя, вход которого соединен с соответствующим выходом счетчика, входом порогового блока и вторым входом регистра сдвига, при этом выходы счетчика подключены к информационным входам второго инвертора, выходы которого соединены со входами буферного регистра, управляющий вход которого соединен с выходом компаратора и управляющим входом блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 528684, кл. Н 03 Н 7/28, 1978 (прототип) .