Устройство для определения места короткого замыкания линии электропередачи

Иллюстрации

Показать всеРеферат

Союз Советсннк

Соцналнстнческнк

Республнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

<ц855546 (6! ) Дополнительное к авт. саид-ву— (22) Заявлено 061179 (21) 2837418/24-21 (5!)М. Кл.

G 01 R 31/08 с присоединением заявки МГосударственный комнтет

СССР яо делам нзобретеннй н открытнй (23) Приоритет—

Опубликовано 150881. Бюллетень Йо 30

Дата опубликования описания 150891 (53) УДК 621, 317,,333.4(088,8) {72) Авторы изобретения!! -... !

В. А. Казинский, Н. А. Гончар, С, И, Гуфин и :-ф -:Н:-,;Циввков !

I, f

Е !!, Р;..,"Ц;;., (7! ) Заяви;гели

Ижевский сельскохозяйственный институт и Ижевский механический институт! !! ;!» (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТА КОРОТКОГО

ЗАМЫКАНИЯ ЛИНИИ ЭЛЕКТРОПЕРЕДАЧИ

Изобретение относится к электроизмерительной технике и может быть использовано для определения расстояния до места короткого замыкания в линии электропередачи.

Известно устройство для определения расстояния до места повреждения на отключенной линии распределительной сети, содержащее источник однофазного переменногс тока, активные и реактивные регулируемые сопротивления, трансформаторы тока и индикатор — сигнализатор, реагирующий на небаланс токов в цепи вторичных обмоток трансформаторов тока (1, Однако это устройство не облада-. ет достаточной точностью из-за необходимости разновременной ручной регулировки активного и реактивного элементов схемы замещения .линии и вычисления расстояния до места замыкания по формулам.

Цель изобретения — повьзаение точности и уменьшение времени контроля, Поставленная цель достигается тем, что в устройство для определения места короткого замыкания линии электропередачи, содержащее источник постоянного напряжения и блок регистрации расстояния до места короткого 30 замыкания, введены кнопка пуска, конденсатор, запоминающие элементы, коммутатор, тнристоры, компараторы, ин" вертирующий компаратор, статический триггер, диод, потенцнометр, резистивные делители напряжения, вычислительный блок,измерительный резистор, источник опорного напряжения, ключ на МДП-транзисторе, причем исток

ИДП-транзистора соединен со входом первого запоминающего элемента, затвор ЧДП-транзистора соединен с выходом. первого компаратора и с единичным входом статического триггера и с управлякщим электродом первого тиристора, анод которого соединен с катодом второго тиристора, со стоком МДП-транзистора, с первьзк выводом измерительного резистора, первым входом коммутатора и первьи входом второго компаратора, второй вывод измерительного резистора соединен со вторым входом коммутатора, с первым выводом линии, с катодом диода, анод которого соединен с первым выводом резистора, второй вывод которого соединен со вторьы входом второго компаратора и с первым выводом резистора, второй вывод которого соединен с выходом второго компарато855546

65 ра и с первым входом третьего компара- тора, выход которого соединен с ну- левым входом статического триггера, выход которого соединен с первым выводом резистора, второй вывод которого соединен со входом второго запоминающего элемента, причем второй вход третьего компаратора соединен со вторым выводом первого резистивного делителя напряжения, третий вывод которого соединен с нулевой шиной, а первый вывод — с выходом первого запоминающего элемента и с первым выводом второго резистивного делителя напряжения, второй вывод которого соединен с первым входом вычислительного блока, второй вход которого соединен с выходом второго запоминающего элемента и с первым выводом резистора, второй вывод которого соединен с нулевой шиной, а выход вычислитель" ного блока соединен со входом блока регистрации расстояния до места короткогD замыкания, при этом третий вывод второго резистивного делителя напряжения соединен с нулевой шиной, а первый и второй выходы коммутатора соединены соответственно со входами третьего и четвертого запоминающих элементов, а третий выход коммутатора соединен с обнуляющими входами этих запоминающих элементов, выходы которых соединены с соответствующими входами инвертирующего компаратора, выход котОрого соединен с первым входом первого компаратора, второй вход которого соединен с движком потенциометра, первый вывод которого соединен с клеммой источника опорного напряжения, второй вывод потенциометра соединен с нулевой шиной, при этом первая клемма источника постоянного напряжения соединена с первым выводом третьего резистивного делителя напряжения, второй вывод которого соединен с первым выводом конденсатора, второй вывод которого соединея с.нулевой шиной, а третий вывод резистивяого делителя напряжения соединен с анодом второго тиристора, управляющий вход которого соединен через кнопку пуска со второй клеммой источника постоянного напряжения, при этом катод первого тиристора соединен с нулевой шиной, причем каждый запоминакщий элемент содержит ИДП-транзистор, МОП-транэистор, з апоминающий конденсатор, причем затвор МДП-транзистора соединен со входом запоминающего .элемента, сток

МДП-транзистора соединен с его истоком, с затвором МОП-.транзистора и с

„ первым выводом запоминающего кондея« сатора, второй вывод которого соединен с нулевой шиной, причем исток

МОП-транзистора соединен с выходом запоминающего элемента, а сток NGHтранзистора — с третьей клеммой источника постоянного напряжения.

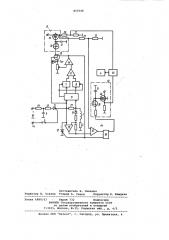

На чертеже приведена принципиальная электрическая схема устройства.

Схема устройства определения места короткого замыкания линии электропе-, редачи содержит источник 1 постоян ного напряжения, подключаемый к объекту контроля, содержащему катушку 2 и резистор 3, блок 4 регистрации расстояния до места короткого замыкания, кнопку 5 пуска, конденсатор 6, запоминающие элементы 7-10, коммутатор 11, тиристоры 12 и 13, компараторы 14-,16, иявертирукщий компаратор 17, статический триггер 18, диод 19, резистивные делители напряжения 20-25, вычислительный блок 26, измерительный резистор 27, ключ 28 на МДП-транзисторе, источник 29 опорного напряжения, причем каждый запоминающий элемент 7-10 содержит МДП-транзистор 30, включенный по схеме диода, запоминающий конденсатор 31 и МОП-транзистор 32, Устройство работает следующим образ ом.

При подключении к отключенному при коротком замыкании объекту контроля источника 1 постоянного напряжения происходит заряд конденсатора 6. При нажатии кнопки 5 пуска происходит включение тиристора 12, что ведет к возникновению переходного процесса в объекте контроля, характеризующегося постоянной времени Т„ .

Напряжение, пропорциональное нарас. тающему току, снимается с резистора

27 и через коммутатор 11 последовательно периодически поступает в эапо минакщие элемеяты 7 и 8, напряжение на выходах которых сравниваются между собой компаратором 17, и в момент их совпадения, характеризующий момент окончания переходного процесса, на выходе компаратора 14 закрывается ключ 28, прекращая заряд через транзистор 30 запомияакщего конденсатора

31, запоминающего элемента 9 от источника 1 постоянного напряжения через резистивные делители 24, 25 и

21. Соотношение резистивяых делителей

20 и 21 составляет 3:1, что обеспечивает подачу. на вычислительный блок

26 напряжения, пропорционального времени Т„ .

Одновременно, по достижению максимума тока переходного процесса, происходит закорачивание через тиристор 13 объекта контроля, в резуль., тате чего экспоненциально убывающее напряжение через компараторы 15 и 16 поступает на вход статического триггера 18, на выходе которого формируется импульс, длительность которого пропорциональна постоянной времени Т переходного процесса при экспоненциальном убывании тока в линии. Опорным сигналом, поступающим на вход компаратора 16, является напряжение, в К раз меньшее максимального, что обеспечивается выбором величины резистивных делителей 22

855546 и 23. На выходе запоминающего элемента 10 появляется напряжение, прапор-> циональное упомянутому Т, которое поступает на второй вход вычислительного блока 26, которое реализует формулу т, т .

Й д

40 Та Т4 где I — расстояние до места короткого замыкания;

Т вЂ” постоянная времени переходного процесса при подключении источника питания;

Т вЂ” постоянная времени переходного процесса прн закорачива.ии линии;

R — образцовое сопротивление, погонная индуктивность, !

Формула из обре те ния

1 ° Устройство для определения места короткого замыкания ликии электропередачи, содержащее источник постоянного напряжения и блок регистрации расстояния до места ксроткого Q5 замыкания, о т л и ч а ю щ е е с я тем, чуа, с целью повьиаення точности и уменьшения времени контроля, в него введены кнопка пуска, конденсатор, запоминающие элементы, коммутатор, 3Q тиристоры, компараторы, инвертирующий компаратор, статический триггер, диод потенциометр, резистивные делители напряжения, вычислительный блок, измерительный резистор, источник опорного напряжения, ключ на МДП-транзисторе, причем исток МДП-транзистора соединен со входом первого запоминающего элемента, затвор МДП-транзистора соединен с выходом первого компаратара и с единичным входом статического триггера и с управляющим электродом первого тиристора, анод которого соединен с катодом второго тиристора, со стоком МДП-транзистора, с первым выводом измерительного 44 резистора, первым входом коммутатора и первым входом в :эрого компаратора, второй вывод измерительного резистора соединен со вторым входом коммутатора, с первым выводом линии, с като- 5g дом диода, анод которого соединен с первым выводом резистора, второй вывод котброго соединен со вторым нхо дом второго компаратора и с первьй выводом резистора, второй вывод которого соединен с выходом второго компаратора и с первым входом третьего компаратора, выход которого соединен с нулевым входом статического триггера, выход которого соединен с пер вым выводом резистора, второй вы- Щ ,вод которого соединен со входом вто" рого запоминающего элемента, причем второй вход третьего компаратора соединен со вторым выводом первого резистивного делителя напряжения, третий вывод которого соединен с нулевой шиной, а первый нынад — с выходом первогс запоминающего элемента и с первым выводом второго резистивного делителя напряжения, второй вывод которого соединен с первым входом вычислительного блока, второй вход которого соединен с вых дом второго запоминающего элемента и с первым выводом резистора, второй вывод которого соединен с нулевой шиной, а выход вычислительного блока соединен со нходом блока регистрации расстояния до места короткого замыкания, при этом. третий вывод второго резистивного делителя напряжения соединен с нулевой шиной, а первый и второй выходы коммутатора соединены соответственно со входами третьего и четвертого запоминающих элементов, а третий ныхад коммутатора соединен с обнуляющими входами этих запоминающих элементов, выходы которых соединены с соответствующими входами инвертирукщега компаратора, выход которого соединен с первым входом первого компаратора, второй вход которого соединен с движком потенциометра, первый вывод которого соединен с клеммой источника опорного напряжения, второй вывод потенциометра соединен с нулевой шиной, при этом первая клемма источника постоянного напряжения соединена с первым выводом третьего резистивного делителя напряжения, второй вывод которого соединен с первьм выводом конденсатора, второй вывод которого соединен с нулевой шиной, а третий вывод реэистивного делителя напряжения соединен с анодом второго тиристора, управляющий вход которого соединен через кнопку пуска со второй клеммой источника постоянного н4 пряжения, при этом катод первого тиристара соединен с нулевой шиной, 2. Устройство no rt.1, о т л и ч а» ю щ е е с я тем,что каждый запоминаю-щий элемент содержит МДП-транзистор, МОП-транзистор, запоминающий конденсат р, причем затвор МДП-транзистора соединен со нхадам запоминающего элемента, сток МДП-транзистора соединен с его истоком, с затвором МОП-транзистора и с первым выводом запоминающего конденсатора, второй, вывод которого соединен с нулевой шиной, причем исток МОП-транзистора соединен с выходом запоминающего элемента, а сток

МОП-транзистора - c третьей клеммой источника постоянного напряжения, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

432430, кл.2G 01 R 31/08, 1971.

855546

Составитель И, Савенко

Редактор Л. Повхан Техред A. Савка Корректор Н. Швыдкая

Заказ 6899/63 Тираж 732 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,. Ж-35, Раушская наб,, д, 4/5

Филиал ППП "Патент", r, Ужгород, ул, Проектная, 4