Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву Р 419893 (22) Заявлено 17.12.79 (21) 2855401/18-24 (51)М

G F 9/22 с присоединением заявки М (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 15.08.81, Бюллетень Й9 30

Дата опубликования описания 15. 08. 81 (53) УДК 681.325 (088. 8) (72) Авторы изобретения

Г.Н. Тимонькин, В.С. Харченко, И.П. Варбаш и С.Н. Ткаченко (54) УСТРОИСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

Изобретение относится к автоматике и вычислительной технике, может быть применено при проектировании устройств управления микропрограммных ЭВМ.

По основному авт.св. ht 419893 известно устройство микропрограммного управления, содержащее адресный запоминающий блок, операционный запоминающий блок, буферный регистр, регистр адреса, регистр команд, дешифратор, генератор импульсов, две группы элементов И, группу элементов

ИЛИ и элемент задержки (11.

Недостатком данного устройства является низкая экономичность, вызванная избыточностью операционного запоминающего блока. Избыточность информации, хранимой в операционном 20 запоминающем блоке, обусловлена следующим. В этом блоке хранятся операционные микрокоманды, которые считываются в соответствии с адресами, поступающими из адресного запоми- 25 нающего блока. Операционный запоминающий блок оптимизирован по числу операционных микрокоманд, которые записаны в нем без повторений. Однако при этом не учитывается возмож- 30 ность повторения отдельных частей различных операционных микрокоманд.

Цель изобретения — повышение надежности, а также повышение экономичности устройства за счет снижения сложности операционного запоминающего блока.

Поставленная цель достигается тем, что устройство микропрограммного управления дополнительно содержит групп элементов ИЛИ и и операционных запоминающих блоков, причем выходы элементов ИЛИ первой группы соединены с первыми группами входов операционных запоминающих блоков со второго по (n+1)-ый и выходы элементов

ИЛИ со второго по (и+1)-ую группы соединены соответственно со вторыми группами входов операционных запоминающих блоков со второго по (n+1)-ый, выходы которых являются выходами устройства.

Сущность изобретения состоит в снижении объема памяти, необходимого для хранения операционных микрокоманд путем однократной записи их повторяющихся частей, содержащихся в одной зоне. При этом под зоной понимается часть операционного запоминающего блока шиной R> < йо.

855662

Ю

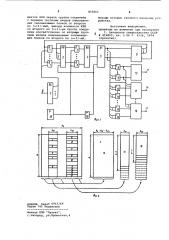

На фиг. 1 приведена функциональная схема устройства микропрограммного управления; на фиг. 2 — пример распределения операционной памяти по отдельным операционным запоминающим блокам при наличии повторяющихся частей операционных микрокоманд в различных зонах для случая и=2.

Схема устройства (фиг.1) включает первую группу элементов И 1, буферный регистр 2, вторую группу элементов И 3, регистр 4 адреса, дешифратор 5, адресный запоминающий блок 6, регистр 7 команд со входом 8, первую группу элементов ИЛИ

9, первый операционный запоминающий блок 10 с выходом 11, вторую группу элементов ИЛИ 12, второй операционный запоминающий блок 13 с выходом

14, (и+))-я группа элементов ИЛИ 15, (и+1)-й операционный запоминающий блок 16 с выходом 17, генератор 18 импульсов, элемент 19 задержки.

На фиг. 2 цифрами I u II обозначены повторяющиеся части двух групп операционных микрокоманд,расположенные в первой зоне, цифрами

ill-V - повторяющиеся части групп операционных микрокоманд, расположенные во второй зоне. Символом N обозначено общее число операционных микрокоманд, символами R — разрядность операционных микрокоманд, R и R — разрядности первой и второй зон, содержащие повторяющиеся части соответственно.

В адресном запоминающем блоке 6 хранятся адресные последовательности микрокоманд, а в операционных запоминающих блоках 10,13 и 16 — различные зоны операционных частей микрокоманд. Причем в операционном запоминающем блоке 10 записана зона частей операционных микрокоманд,не содержа-.— щая повторений, а в операционных запоминающих блоках 13 и 16 — зоны операционных микрокоманд, имеющих общие повторяющиеся части.

Устройство микрокомандного управления работает следующим образом.

Код операции из регистра 7 команд через элементы И 1 передается в буферный регистр 2. lio первому импульсу генератора 18 этот код переписывается в регистр. 4 адреса через элементы

И 3. Затем этим импульсом, задержанным элементом 19 задержки на время, возбуждается один из выходов дешифратора 5 и одновременно обнуляется буферный регистр 2. В соответствии с дешифрированным адресом из адресного запоминающего блока 6 через его группу выходов в буферный регистр 2 записывается адрес следующей микрокоманды. Одновременно со считыванием информации из блока 6 считывается информация из всех операционных запоминающих блоков 10, 13 и 16. При этом адреса, по которым считываются части операционных микрокоманд из блоков 10, 13 и 16 формируются следующим образом.

Для первого операционного запоминающего блока 10 — на выходе одного из элементов ИЛИ первой группы 9; для второго операционного запоминающего блока 13 — на выходе одного из элементов ИЛИ первой группы 9 (если часть операционной микрокоманды, записанная в боке 13, не является повторяющей, т.е. используется один раз), или на выходе одного из элементов ИЛИ 12 второй группы (если часть операционной микрокоманды, записанная в блоке 13, является повторяющейся, т.е. используется несколько раз в различных микрокомандах);для (и+1)-ro операционного запоминающего блока 16 — на выходе одного из элементов ИЛИ 9 первой группы (есть часть операционной микрокоманды, записанная в блоке 16, используется один раз) или на выходе одного из элементов ИЛИ (и+1)-й группы 15 (если эта часть используется несколько раз).

Части операционных микрокоманд из блоков 10, 13 и 16 поступают на выходы 11,14, и 17 и далее на объект управления. По очередному тактовому импульсу адрес следующей микрокоманды передается из буферного регистра

2 в регистр 4 адреса, а затем дешифрируется дешифратором 5. В дальнейшем работа устройства продолжается аналогично. Ветвление в устройстве микропрограммного управления осуществляется в моменты появления на выходе одиночного разряда адресного запоминающего блока 6 единичного сигнала, по которому опрашивается состояние некоторых разрядов кода операции, поступающего в регистр 7 команд .В результате через элементы И 1 первой группы модифицируется адрес очередной микрокоманды, записанный в буферном регистре 2.

Таким образом, введение и дополнительных операционнйх блоков и групп элементов ИЛИ и обусловленных ими связей позволяет существенно снизить объем памяти, необходимой для хранения операционных микрокоманд. Это повышает экономичность и надежность устройства в целом.

Формула изобретения

Устройство микропрограммного управления по авт.св. 9 419893, отличающееся тем, что, с целью повышения надежности, оно дополнительно содержит и групп элементов ИЛИ и и операционных за,поминающих блоков, причем выходы эле855662 ментов ИЛИ первой группы соединены с первыми группами входов операционных запоминающих блоков со второго по (n+1)-ный, выходи элементов ИЛИ со второго по (n+1) ую группу соединены соответственно со вторыыи группами входов операционных запоминающих блоков со второго по (n+1)-ый, ВНИИПИ Заказ б 915/б 9

Тираж 745 Подписное

Филиал ППП "Патент", r.Ужгород, ул.Проектная,4 выходы которых являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 419893, кл. G 06 F 9/16, 1974 (прототип).