Интегратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Реснублик

855674

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 2%0378 (21) 2596608/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.0881. Бюллетень ¹ 30

Дата опубликования описания 150881

<З1) М. Кл.

G G 7/186

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 681. 335 (088.8) (72) Автор изобретения

Н.И.Коровин

I.:

Специальное конструкторское бюро псс;приборостроению (1 (71) Заявитель

-- I (54) ИНТЕГРАТОР

Изобретение относится к вычислительной технике и может быть использовано при интегрировании двух и более аналоговых сигналов последователь-5 но во времени.

Известны интеграторы, содержащие операционный усилитель, интегрирующнй конденсатор, масштабные резисторы и устройство управления для поочеред- 1О ного подключения каждого из входных сигналов ко входу интегратора через соответствующие масштабные резисторы, которое осуществляется с помощью ключей последовательного и параллельного типа $1). 15

Недостатком данных интеграторов с ключами последовательного типа является сложность. вызванная трудностью выполнения бесконтактных ключей последовательного типа, например, 2О на дефицитных элементах - оптронах, а также снижение точности из-эа утечек ключей последовательного типа вследствие утечек, в особенности при больших постоянных времени интегрирования. В интеграторах с управляищими устройствами на более простых ключах параллельного типа утечки ключей в закрытом состоянии не снижают точности интегратора, так как токи утечек замыкаются через низкоомные ограни-. чивающие резисторы. Однако в этом случае точность интеграторов снижается за счет остаточного падения напряжейия на ключах, а также из-за напряжения смещения операционного усилителя.

Наиболее близким к предлагаемому является интегратор, содержащий операционный усилитель, инвертирующий вход которого соединен через конденсатор с выходом операционного усилителя, а через две параллельные цепи из переменного (масштабного) и ограничивающего резистора с соответствующими входными клеммами, причем общая точка резисторов каждой цепи подключена через ключ двухтактного распределителя к общей шине Г2 J.

Недостатком данного интегратора является низкая точность из-за влияния остаточного напряжения на ключе и напряжения смещения операционного усилителя.

Цель изобретения — повыаение точности интегратора при наличии напряжения смещения операционного усилителя и остаточного напряжения ключей устрсйства управления.

855674 указанная цель достигается тем, вывод резисторов 4 и 3 заземпяется, что в интегратор, содержащий опера- тем самым от инвертирующего входа ционный усилитель, инвертирующий операционного усилителя 1 отключавхо4 которого соединен через интегри- ется источник сигнала U . K инвертирующий конденсатор с выходом опера- рующему входу операционного усилителя

I ционного усилителя, а неинвертирующий 1 подводится ток от второго источ,,вход подключен к шине нулевого потек- ника сигнала U через резисторы циала, причем первый вход интегратора б и 5,происходит переэаряд конденсачерез первый ограничивающий резистор тора 2 и формирование времени паузы. подключен к первому выводу первого В идеальном случае, когда остаточное масштабного резистора и замыкающему напряжение переключателя 9 и напряконтакту переключателя, второй вход жение смещения операционного усилите- . интегратора через второй ограничиваю- ля 1 равны нулю при соединении общещий резистор соединен с первым выводом го вывода, например резисторов 4 и 3: второго масштабного резистора и размы- с шиной нулевого потенциала, выводы кающим контактом переключателя, пере- резистора 3 оказываются эквипотенциключающий контакт которого подключен 15 альными, ток через резистор 3 не прок шине нулевого потенциала, введены текает. При наличии же остаточного четыре разделительных диода, соеди- напряжения ключей двухтактного расненных попарно встречно-параллельно, пределителя и напряжения смещения причем второй вывод каждого масштаб-, операционного усилителя 1 при эамкнуного резистора чбрез соответствующие 2О той на шину нулевого потенциала обвстречно-параллельно соединенные раэ- . щего вывода резисторов 4 и 3, к реэис- делительные диоды подключен к инвер- . тору 3 приложена аглебраическая сумма тирующему входу операционного усили- остаточного напряжения переключателя теля. 9 и напряжения смещения операционного

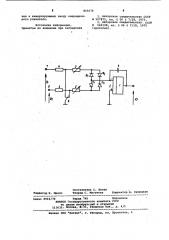

Ка чертеже приведена схема инте- 2 усилителя 1, вызывающая параэитный гратора ток интегратора. Однако эа счет вклюИнтегратор содержит операционный чения в каждую иэ цепей двух встречноусилитель 1, инвертирующий вход кото- параллельно включенных диодов, упомярого соединен через интегрирующий кон- нутое паразитное напряжение прикладыденсатор .2 с выходом операционного вается непосредственно к диодам, коусилителя, две параллельные цепи торые вследствие нелинейности харакиэ масштабного и ограничивающего теристики при малых уровнях паразитрезисторов 3, 4 и 5, б соответствен- ного напряжения практически раэрыно соединены с входами 7 и 8 инте- вают цепь, повышая точность интегратора, причем общий вывод резисто- гратора. .ров 3, 4 и 5, б каждой цепи подключен З5 Технико-зкономическая эффективчереэ переключатель 9 к шине нуле- ность изобретения .определяется более вого,потенциала, и включенные после- простым выполнением интегратора при довательно с каждым из масштабных ре- заданной точности. зясторов два встречно-параллельно соединенных разделительных диода 40 Формула изобретения

1О„,1О и 11„, 11

Йнтегратор работает следующим обИнтегратор, содержащий операционразом. ный усилитель, инвертирующий вход

Напряжение 0 и U2 входных сигна- которого соединен. через интегрирующий лов с входов 7 и 8 вйэывает протека- 4> конденсатор с выходом операционного ние токов через ограничивающие резис- усилителя, а неинвертирующий вход торы 4 и б. Tîê, протекающий через с шиной нулевого потенциала, причем резистор б, замыкается на шину ну- первый вход интегратора через первый левого потенциала через переключатель ограничивающий резистор подключен

9 двухтактного расцределителя и не о к первому выводу первого масштабного достигает инвертирующего входа one- резистора и замыкающему контакту перерационного усилителя 1. В то же вре- ключателя, второй вход интегратора мя ток через резисторы 4 и 3 подво- через второй ограничивающий резистор дится к инвертирующему входу опера- соединен с первым выводом первого ционного усилителя 1 и заряжает интегри- масштабного резистора и размыкающим рующий конденсатор 2,происходит формиро-з5 контактом переключателя, переключаю- . вание,например,времени импульса Вели- щий контакт которого подключен к шине чина тока (длительность импульса) оп- нулевого потенциала, о т л и ч а юределяется напряжением 04 и сУммаРной Щ и и с я тем, что, с целью повышевеличиной сопротивлений резисторов ния точности интегратора, в него ввв4 и 3. Как правило, сопротивлейие Я дены четыре разделительных диода, ограничивающего резистора 4 выбирает- соединенных попарно встречно-парал,ся меньше. сопротивления гззистора 3. лельио, причем второй вывод каждого

В следующий момент времени .замыкает-. масштабного резистора через соответся другой контакт переключателя 9 ствующие встречна-параллельно соедидвухтактного распределителя, общий, ненцые разделительные диоцы подклю855674!

Корректор,В. Синипкая

Составитель С. Белан

Техред С. Мигунова

Редактор Н. Иинко

Заказ 6916/70 Тирам 745 Подписное

ВНИИПИ ГосУдарственного комитета СССР по делам изобретений и открытий

113035.москва, Ж-35, Раущская наб., д. 4/5

Филиал ППП "Патент", r. Уигород, ул. Проектная, 4 чен к инвертирующему входу -операцион.ного усилителя.

Источники инФормации. принятые во внимание при экспертизе

1., авторское свидетельство СССР

Р 507872, кл. G 06 G 7/18, 1973.

2..Авторское свидетельство: СССР

9 542198, кл. G 06 G 7/18, 1975 (прототип) °