Регистр сдвига

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Э (61) Дополнительное к авт. свид-ву (22) Заявлено 24.07. 79 (2f) 2800917/18-24 (53)hh. Ка.

3 с присоединением заявки Но (23) Приоритет

G 11 С 19/00

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 15,0881, Бюллетень Но 30

Дата опубликования описания 15. 08. 81 (53) УДК 681.327 ° 66 (088. 8) (72) Автор изобретения

Л.П. Петренко л (73) Заявитель (54) РЕГИСТР СДВИГА

30

Изобретение относится к вычислительной технике и может быть использовано.при построении регистров сдвига.

Известен сдвигающий регистр, каждый разряд ячейки которого состоит из двух синхронных элементов, а к первому элементу каждого разряда присоединяется дополнительный расширитель из элементо И-ИЛИ. Регистр имеет общую шину установки нуля н две шины сдвигающнх импульсов, по одной из которых поступает прямой сигнал, а по другой — инвертированный 4 1 . о

Наиболее близким по технической сущности к изобретению является однофазный двухтактный регистр с параллельно-последовательным сдвигом, содержащий разрядные шины и подключенные к ним разрядные ячейки, каждая из которых выполнена из двух входовых элементов И с инвертором на первом входе и соединены последовательно с элементом ИЛИ 2).

Недостатком таких сдвигающих регистров является сложность схемного выполнения.

Цель изобретения - упрощение регистра сдвига.

Поставленная цель достигается тем,: что в регистре сдвига, содержащем ячейки памяти, каждая нз которых выполнена на последовательно соединенных элементах ИЛИ и И, формирователь тактовых импульсов, первый и второй входы которого соединены соответственно с тактовой шиной и шиной сброса, вторые входы элементов И четных ячеек памяти подключены к первому выходу формирователя тактовых импульсов, ко второму выходу которого подсоединены вторые входы элементов И нечетных ячеек памяти, выход элемента И каждой ячейки памяти соединен с первым входом элемента ИЛИ

1данной ячейки памяти и с первым вхо дом элемента ИЛИ последующей ячейки памяти ° кроме того, формирователь тактовых импульсов содержит последовательно включенные первый элемент И, первый элемент ИЛИ и T-триггер, элементы задержки, второй и третий элементы ИЛИ, инвертор, второй и третий элементы И, выходы которых соединены с выходамн формирователя тактовых импульсов, одни из входов второго н третьего элементов И подключены,соответст.венно к выходам второго и третьего

855732

4 элементов ИЛИ, первые входы которых соединены.с выходами элементов задержки, а вторые входы — с выходами

T-триггера, другие входы второго и третьего элементов И подсоединены к выходу инвертора, вход которого подключен ко второму входу формирователя тактовых импульсов и к одному из входов первого элемента И, другой вход которого соединен с одним из выходов T-триггера, второй вход первого элемента ИЛИ соединен с первым входом формирователя тактовых импульсов.

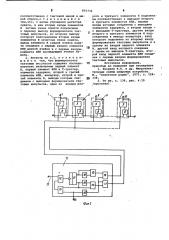

На фиг.1 представлена функциональная схема предлагаемого регистра сдвига; на фиг. 2 - временная диаграмма работы регистра сдвига.

Регистр сдвига содержит ячейки

1-4 памяти, которые содержат элементы И 5 и элементы ИЛИ 6, выходы

7-10 ячеек 1-4 памяти, формирователь

11 тактовых импульсов, который содержит элементы ИЛИ 12-14, элементы И 15-17, элементы 18 и 19 задержки, инвертор 20, T-триггер 21, тактовая шина 22 и шина 23 сброса.

Работа регистра сдвига заключает ся в следующем.

При t поступает через вход регистра на элемент ИЛИ 6 ячейки памяти импульс запуска (фиг.2,a),ïðè- .

-чем подача запускающего импульса засинхронизирована с наличием на выходе элемента И 16 (фиг.2,к ) высокого потенциала, а на выходе элемента И 17 (фиг.2,ц) низкого потенциала, на первом входе элемента И 5 ячейки 1 памяти появляется высокий .сигнал, что приводит к появлению сигнала на выходе элемента И 55 (фиг.2,М). С выхода 7 ячейки 1 памяти сигнал поступает на первый вход элемента ИЛИ 6 этой ячейки памяти и поддерживает высокий уровень на выходе этого элемента ИЛИ (фиг.2,0) до тех пор, пока уровень сигнала на выходе элемента И 16 не уменьшится. С выхода 7 сигнал Через элемент ИЛИ 6 поступает на первый вход элемента

И 5 ячейки 2 памяти,но,поскольку на выходе элемента И 17 уровень сигнала низкий, то данная ячейка памяти не возбуждается.

При t на вход 22 поступает тактовый импульс (фиг.2,Ь) и через элемент ИЛИ 12 - иа вход T-триггера 21.

После окончания t действия импульса (фиг.),Ь) уровни сигнала на выходе

Т-три&гера 21 меняются (фиг.2 З,Ь 1.

«Цля того, чтобы сигналы на выходах элементов И 16 и 17 были смещены друг относительно друга на величину переходных процессов в ячейке 2 памяти регистра (элемента И 5) включены элементы 18 и 19 задержки, так что на выходе элемента ИЛИ 13 сигнал (фиг.2,e) уменьшается только при с», тогда как уровень на выходе эле

t0

$0

И мента ИЛИ 14 возрастает при t . В ь . соответствии с уровнями сигнала (фиг.2,ерш) изменяется уровень на выходе элемента И 16 (фиг.2,к ) и И 17 (фиг.2,л).

При с, когда уровень на выходе элемента И 17 возрастает, увеличивается уровень на выходе элемента

И 5 ячейки 2 памяти (фиг.2р ) и элемента ИЛИ 6 ячейки 1 памяти (фиг. 1,р ) .

При t» уменьшаются уровни сигнала на выходах элементов И 5, ИЛИ 6 ячейки 1 памяти.

При й5 и и й< и <р происхОдит аналогичная ситуация, за счет наложения двух тактовых сигналов. Припоследующая ячейка памяти успевает возбудиться, но время задержки должно выбраться таким, чтобы оно не превышало переходные процессы одной ячейки памяти, в противном случае будет возбуждаться несколько ячеек памяти сразу, например две, хотя данный регистр допускает возбуждение двух ячеек памяти одновременно, т.е. проскакивание сигнала с предыдущей ячейки памяти на две последующих. Главное, чтобы не было проскакивания сразу на три ячейки памяти.

Возбуждение второй ячейки 2 памяти устраняется автоматически за счет того, что высокий потенциал остается только на одном из выходов элементов

И 16 и 17.

При t поступает на шину 23 и на входы элементов И 15 и инвертора 20 импульс -сброса (фиг.2,6 ). На выходе инвертора 20 (фиг.2,g) уровень падает, так же как и на выходах элементов И 16 и 17, что приводит к обесточиванию всех ячеек памяти регистра и информация исчезает.

Поскольку для ввода информации необходимо, чтобы высокий сигнал был на выходе элемента И 16, а при сбросе этого может не получиться, поэтому сигнал с выхода элемента И 15 поступает на первый вход элемента

ИЛИ 12, так, что, если при сбросе сигнал находится на единичном выходе

T-триггера 21, то импульс сброса поступает на вход Т-триггера 21 и при „ переводит его в другое состояние (фиг.2,д и е ). После регистр готов к приему информации.

Использование изобретения позволяет уменьшить число элементов на разряд сдвигающего регистра.

Формула изобретения, 1. Регистр сдвига, содержащий ячейки памяти, каждая из которых. выполнена на последовательно соединенных элементах ИЛИ и И, формирователь тактовых импульсов, первый и второй входы которого соединены

855732 фиг.! соответственно с тактовой шиной и шиной сброса,отличающийся тем,что, с целью упрощения регистра сдвига, в нем вторые входы элементов

И четных ячеек памяти подключены, к первому выходу формирователя тактовых импульсов, ко второму выходу которого подсоединены вторые входы элементов И нечетных ячеек памяти, выход элемента H каждой ячейки памяти соединен с первым входом элемента

ИЛИ данной ячейки и с первым входом . элемента ИЛИ последующей ячейки памяти.

2. Регистр по п,i, о т л и ч а юшийся тем, что формирователь тактовых им пульсов содержит последовательно включенные первый элемент

И, первый элемент ИЛИ и Т-триггер, элементы задержки, второй и третий элементы ИЛИ, инвертор, второй и третий элементы И, выходы которых соединены с выходами формирователя тактовых импульсов, одни из входов юторого и третьего элементов И подключены соответственно к выходам второго и третьего элементов ИЛИ, первые входы которых соединены с выходами элементов задержки, а вторые входы— с выходами Т-триггера, другие входы второго и третьего элементов И подсоединены к выходу ннвертора, вход которого подключен ко второму входу формирователя тактовых импульсов и к одному из входов первого элемента о И, другой вход которого соединен с одним из выходов Т-триггера, вто- . рой вход первого элемента ИЛИ соединен с первым входом формирователя тактовых импульсов.

15 Источники информации, принятые во внимание при экспертизе

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств, М., "Советское радио", 1975, с. 129 «ф 138.

2. То же, с. 139, рис. 4.10 (прототин).

855732

Составитель А.Воронин

Техред Л. Пекарь .Корректор С. Шекмар

Редактор М. Погориляк

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6923/73

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4