Запоминающее устройство с обнаружением одиночных ошибок

Иллюстрации

Показать всеРеферат

Свез Сееетекнк

Сецнавнетическик

Рвсн

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВй ЕТИЛЬСТВУ

«i355738 (61) Дополнительное к aar. свид-ву (22) Заявлено 300879 (21) 2815317/18-24 с присоединением заявки Йо (23) Приоритет

Опубликовано 150881, Бюллетень Й9 30 (51)pA. Kll 3

G 11 С 29/00

Государственный комнтет

СССР но делам нзобретеннй н открытнй (53) УДК 681 327 6 (088.8) Дата опубликования описания 15. 08. 81 с

A.È. Карпухин и A.È. Коекин (72) Авторы иэобретемия (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ

ОДИНОЧНЫХ ОШИБОК

Изобретение относится к вычислительной технике и.может быть использовано при проектировании запоминающих устройств повышенной надежности.

Известны запоминающие устройства с обнаружением одиночных ошибок,которые содержат блок свертки по модулю два, подключенный к регистрам, блок сравнения, подключенный к выходам триггеров контрольных разрядов регистров и к выходам блока свертки по модулю два, и блок преобразования контрольных разрядов P1) .

Недостатком этого устройства 15 .является низкая его надежность за счет введения дополнительного оборудования в виде контрольных разрядов.

Наиболее близким по технической сущности к изобретению является эа- 20 помЭиающее устройство с обнаружением ошибки, содержащее регистр адреса, входной регистр числа с контрольным разрядом на нечетность (четкость), дешифратор адреса, накопитель, схему 25 проверки на четкость, выходной регистр числа, усилители считывания и блок управления E2).

Недостатком этого устройства является низкая надежность за счет избы- 30 точного оборудования, необходимого для запоминания контрольных разрядов.

Цель изобретения — повышение надежности.

Поставленная цель достигается тем, что в запоминающее устройство с с бнаружением одиночных ошибок, содержащее адресный регистр, первые выходы которого подключены ко входам адресного дешифратора, первый накопитель, адресные входы которого подключены к выходам адресного дешифратора, а его информационные входы являются информационными входами устройства, блок управления, первый выход которого подключен к первому управляющеМУ входу первого накопителя, и блок контроля, дополнительно введены второй накопитель, адресные входы которого подключены к выходам адресного дешифратора, информационные входы — к информационным входам первого накопителя, а первый управляющий вход — к первому выходу блока управления, формирователь. контрольного разряда, входы которого подключены к информационным входам первого накопителя, первый элемент И, первый вход которого подключен к выходу формирователя контрольного

855738 разряда, а второй вход — к первому выходу блока управления, второй элемент И, первый вход которого подключен ко второму выходу адресного регистра, а выход - к первому входу блока контроля, элемент ИЛИ, первый вход которого подключен к, выходу первого элемента И, а второй входк выходу второго элемента И, а выход элемента ИЛИ подключен ко второму входу адресного дешифратора, группу элементов ИЛИ, первые входы которых подключены к выходам первого накопителя, а вторые входы - к выходам второго накопителя, выходы групп, элементов ИЛИ подключены ко вторым входам блока контроля и являются выходами устройства, второй выход блока управления подключен ко второму входу второго элемента И и ко вторым управляющим, входам первого и второго накопителей. !

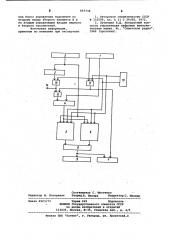

Блок-схема запоминающего устройства с обнаружением одиночных ошибок приведена на чертеже.

Запоминающее устройство с обнаружением одиночных ошибок содержит адресный регистр 1, входной регистр

2 числа, подключенный к формирователю

3 контрольного разряда, адресный дешифратор 4,первый накопитель 5, второй накопитель б, блок 7 контроля, группу элементов ИЛЙ 8, выходной регистр 9 числа, первый элемент.

И 10, второй элемент И 11, элемент

ИЛИ 12, блок 13 управления, информационный выход 14.

Запоминающее устройство с обнаружением одиночных ошибок работает, следующим образом.

При з аписи информационное слово с входного регистра 2 числа поступает на формирователь 3 контрольного разряда, вырабатывающий старший разряд адреса, сигнал с которого через первый элемент И 10 и при наличии управляющего сигнала записи с блока

13 управления и элемента ИЛИ 12 совместно с сигналами с младших разрядов адресного регистра 1 поступает на вход адресного дешифратора 4, где вырабатывается сигнал записи информации с входного регистра 2 числа в накопители 5 и б, а также на информационный выход 14 для формирования полного адреса, необходимого при считывании информации.

Таким образом, в накопителе 5 содержатся информационные .слова толью с четным, а в накопителе 6,с нечетным числом единицо что и является предпосылкой обнаружения одиночной ошибки без использования дополнительного контрольного разряда

s информационном слове.

При считывании с адресного регистра 1 сигналы с младших разрядов адресного. регистра 1 поступают непосредственно, а с старшего разряда через второй элемент И 11 при -на:личии управляющего сигнала считывания с блока 13 управления и элемента ИЛИ 12 на входы адресного дешифратора 4, где вырабатываются сигналы считывания информации с той части блока запоминания, которая определяется старшим разрядом адреса. Считанная информация через группу элементов ИЛИ 8 поступает на входы блока 7 контроля совместно с сигна1О лом с выхода второго элемента И 11, а также на выходной регистр 9 числа.

Предлагаемое изобретение позволяет обнаруживать одиночные ошибки без использования дополнительного

1$ контрольного разряда, что приводит к уменьшению оборудования, а значит к повышению надежности устройства.

Кроме того, снижается стоимость запоминающего устройства.

Формула изобретения

Запоминающее устройство с обнаружением одиночных ошибок, содержащее

25 адресный регистр, первые выходы которого подключены к первым входам адресного дешифратора, первый накопитель, адресные входы которого подключены к выходам адресного дешифgg ратора, в его информационные входы являются информационными входами устройства, блок управления, первый выход которого подключен к первому управляющему входу первого накопи3 теля, и блок контроля, о т л и ч аю щ е е с я; тем, что, с целью.повышения надежности устройства, в него. введены второй накопитель, адресные входы которого подключены к выходам адресного дешифратора, информационные входы — к информационным входам первого накопителя, а первый управляющий вход — к первому выходу блока управления, формирователь контрольного разряда, входы которого подфЯ ключены к информационным входам первого накопителя, первый элемент

И, первый вход которого подключен к выходу формирователя контрольного. разряда, а второй вход — к первому

5Q выходу блока управления, второй элемент И, первый вход которого подключен ко второму выходу адресного регистра, а выход — к первому входу блока контроля, элемент ИЛИ, первый вход которого подключен к выходу первого элемента И, а второй вход - к выходу второго элемента И, а выход элемента ИЛИ подключен ко второму входу адресного дешифратора, группу элементов ИЛИ, первые входы

6О которых подключены к выходам первого накопителя, а вторые входы — к выходам второго накопителя, выходы группы элементов ИЛИ подключены ко вторым входам блока контроля и явля6$ ются выходами устройства, второй вы855738

Составитель С. Шустенко

Редактор M. Погориляк ТехредЛ. Пекарь Корректор С. Шекмар

Тираж 645 Подписное °

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6923/73

Филиал ППП "Патент", г..ужгород, ул. Проектная,4 ход блока управления подключен ко второму входу второго элемента И и ко вторым управляющим входам первого и второго накопителей.

Источники инФормации, . принятые во внимание при экспертизе

1; Авторское свидетельство СССР

В 333599, кл. G 11 С 29/00, 1972 °

2. Путинцев Н.Д. Аппаратный контроль управляющих цифровых вычислительных машин. N., "Советское радио", 1966 (прототип).