Оперативное запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ н>855739 (61) Дополнительное к авт. свид-ву (22) Заявлено 01. 11. 79 (21) 2846519/18-24

<51)м. к. с присоединением заявки NP

G 11 С 29/00

Государствеииый комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 15.08.81,Бюллетень No 30

Дата опубликования описания 15. 08. 81 (53) УДК 681.327 (088.8) (72) Авторы изобретения

А.М. Богомолов, В. И. Кнышев, В.Л. Скиби ский, Ю.А. Слнвицкий, Г.М. Чекаловец н Н.К. Иваитзв"(71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С АВТОНОМНЫМ КОНТРОЛЕМ

Изобретение относится к запоминающим устройствам и может быть исполь-, зовано при создании оперативных запоминающих устройств в интегральном исполнении.

Известно оперативное запоминающее устройство с автономным контролем, содержащее регистр адреса, адресный коммутатор, накопитель, элементы И, регистр числа, бло . управления, блок свертки по заданному модулю, блок сравнения, кодовые шины адреса и числа P1) .

Недостатком этого устройства является невысокое быстродеЪствие. . 15

Наиболее близким техническим решением к изобретению является устройство, содержащее дешифратор строк и буферный регистр, дешифратор столбцов и буферный регистр, выходы кото- 20 рых через усилители строк и усилители столбцов подключены к матрице памяти, устройство синхронизации и управления, два выхода которого подключены к дешифратору строк и буферному ре- 25 гистру и дешнфратбру столбцов и буферному регистру, два других выхода - к усилителям столбцов, устройство ввода-вывода подключено к устройству синхронизации и управления, 30 дешифратору столбцов и буферному регистру 2).

Недостатком такого устройства является низкое быстродействие, обусловленное сложностью средств контроля при производстве и испытаниях устройства, выполненного в виде интегральной схемы.

Цель изобретения - повышение быстродействия устройства эа счет введения средств автономного контроля в интегральную схему.

Поставленная цель достигается тем, что в оперативное запоминающее устройство с автономным контролем,содержащее накопитель, дешифраторы,усилители, блок управления и блок ввода-вывода информации, причем выходы первого дешифратора подключены соответственно ко входам первого усилителя, выходы которого соединены соответственно с одними иэ входов накопителя, другие, входы которого подключены к выходам второго усилителя, один иэ выходов блока ввода-вывода информации является первым выходом устройства, а другие выходы соединены с одними иэ входов второго дешифратора, выходы которого подключены ко входам второго усилителя, выходы .

855739

5 !

О

40 б5 блока управления соединены соответ-; ственно с управляющими входами дешифраторов и усилителей, введены счетчик, генератор импульсов, формирователи импульсов, элементы ИЛИ и блок анализа, причем вход генератора импульсов является первым входом устройства и соединен с первыми входами счетчика, первого формирователя импульсов и блока анализа, выход генератора импульсов подключен к первому входу второго формирователя импульсов и второму входу счетчика, один из выходов которого соединен со вторым входом первого формирователя импульсов, а другие выходы подключены соответственно ко входам первого дешифратора, другим входом второго дешифратора и третьему входу первого формирователя импульсов, первый выход которого соединен со вторым входом второго формирователя импульсов, а второй выход — co вторым входом блока анализа, третий вход .которого подключен к первому выходу устройства, первый выход второго формирователя импульсов соединен с четвертым входом блока анализа, второй выход с пятым входом блока анализа и первым входом первого элемента ИЛИ, а третий выход — с первым входом второго элемента ИЛИ, первый вход третьего зле лента ИЛИ подключен к третьему выходу первого формирователя импульсов, выходы элементов ИЛИ соедииены соответственно со входами блока ввода-вывода информации, вторые входы элементов ИЛИ и выход блока анализа являются соответственно вторым, третьим и четвертым входами и вторым выходом устройства.

Крома того, введены схема сравнения, элемент Й и триггеры, причем выход схемы сравнения подключен к первому входу элемента И, выход которого соединен с первым входом первого триггера, выход которого подключен к первому входу второго триггера, второй вход и выход которого соединены соответственно с первым входом и с выходом блока анализа, входы схемы сравнения подключены соответственно ко второму и к третьему входам блока анализа, а вторые входы элемента И и первого триггера — соответственно к четвертому и пятому входам блока анализа.

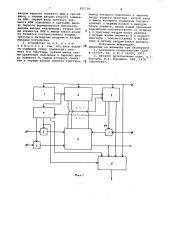

На фиг.1 и 2 приведена функциональ ная скема предлагаемого устройства; на фщр. 3 — функциональная схема, блока анализа.

Устройство содержит генератор 1 импульсов, счетчик 2, первый 3 и второй 4 формирователи импульсов, первый 5, второй 6 и третий 7 элементы

ИЛИ, блок 8 анализа и блок 9 оперативной памяти, состоящий из накопителя 10, первого 11 и второго 12,цешифратора, первого 13 и второго 14 усилителей, блока 15 управления и блока 16 ввода-вывода информации.

Выходы первого дешифратора 11 подключены соответственно ко входам первого усилителя 13, выходы которого соединены соответственно с одними из входов накопителя 10. Другие входы накопителя 10 подключены к выходам второго усилителя 14. Один из выходов блока 16 ввода-вывода информации является первым входом устройства, а другие выходы соединены с одними из входов второго дешифратора 12, выходы которого подключены ко входам второго усилителя 14. Выходы блока 15 управления соединены соответственно с управляющими входами дешифраторов

11 и 12 и усилителей 13 и 14.

Вход генератора 1 импульсов является первым входом устройства и соединен с первыми входами счетчика 2, 20 первого формирователя 3 импульсов и блока 8 анализа. Выход генератора 1 импульсов подключен к первому входу второго формирователя 4 импульсов и второму входу счетчика 2, один из выg5 ходов которого соединен со вторым входом первого формирователя 3 импульсов, а другие выходы подключены соответственно ко входам первого дешифратора 11, другим входом второго дешифратора 12 и третьему входу первого формирователя 3 импульсов. Первый выход первого формирователя 3 импульсов соединен со вторым входом второго формирователя 4 импульсов, а второй выход — со вторым входом блока 8 анализа, третий вход которого подключен к первому выходу устройства. Первый выход второго формирователя 4 импульсов соединен с четвертым входом блока 8 анализа, второй выход — с пятым

40 входом блока 8 анализа и первым входом.первого элемента ИЛИ 5, а третий выход — с первым входом второго эле-, мента ИЛИ 6. Первый вход третьего элемента ИЛИ 7 подключен к третьему выходу первого формирователя 3 импульсов. Выходы элементов ИЛИ 5,6 и

7 соединены соответственно со входами блока 16 ввода-вывода информации. Вторые входы элементов ИЛИ 5,6

5р и 7 и выход блока 8 анализа являются соответственно вторым, третьим и четвертым входами и вторым выходом устройства. При этом блок 8 анализа выполнен содержащим первый 17 и второй 18 триггеры, элемент И 19 и схему 20 сравнения.

Выход схемы 20 сравнения подключен к первому входу элемента И 19, выход которого соединен с первым входом первого триггера 17. Выход первого триггера 17 подключен к первому входу второго триггера 18,второй вход и выход которого соединены соответственно с первым входом и с выходом блока 8 анализа. Входы схемы

20 сравнения подключены соответствен855739 но ко нторому и к третьему входам блока 8 анализа, а вторые входы элемента И 19 и первого триггера 17 соответственно к четвертому и пятому входам блока 8 анализа.

Устройство работает следующим образом.

Внешним сигналом "Антоном", посту.пающим на первый вход устройства, начинается режим записи информации в устройство. Этот сигнал устанавливает в начальное состояние счетчик 2, первый формирователь 3 импульсов, предназначенный для формирования тестовых импульсов, и второй триггер 18 блока 8 анализа и запускает генератор 1 импу.:ьсов.

Второй формирователь 4 импульсон выдает импульсы, обеспечивающие режим записи, а счетчик 2 последовательно выдает адреса, поступающие через дешифраторы 11 и 12 и усилители 3 и 14 20 на входы накопителя 10. При этом импульсы с выхода первого разряда счет чика 2 через первый формирователь 3 импульсов и третий элемент ИЛИ 7 поступает на соответствующий вход блока 16 ввода-вывода информации.

В режиме записи во все четные ячейка накопителя 10 записываются логические "1", а во все нечетные ячейки — логические "0". В следующем цикле контроля работы устройства вы- 30 полняется режим считывания информации, записанной в предыдущем цикле.

Второй формирователь 4 импульсов устанавливает в начальное состояние первый триггер 17 блока 8 анализа. 35 . С одного из выходов счетчика 2 подается на втброй вход первого формиронателя 3 импульсов адрес, по которому считывается информация из ячейки накопителя 10. Одновременно с другого gg выхода счетчика 2, соответствующего выходу его первого разряда, поступает импульс на третий вход первого формирователя 3 импульсов, со второго выхода которого на второй вход блока

8 анализа подается тестовая информация. Эта тестовая, информация сравнивается схемой 20 сравнения с информацией, считанной из накопителя 10 по адресу, поступившему с одного из выходов счетчика 2. 56 о

В случае несовпадения импульс с выхода схемы 20 сравнения перебрасывает первый триггер 17, таким образом вырабатывается импульс ошибки, который фиксируется вторым триггером

18, с выхода которого подается на второй выход устройства. При появлении первого импульса ошибки, процесс контроля устройстна заканчивается.

При совпадении и схеме 20 сравнения 60 тестовой информации с информацией, считанной из накопителя 10, по первому адресу, сигнал ошибки отсутствует, и далее аналогичным образом проверяется следующая ячейка накопителя 10 65 в соответствии с адресом, поступающи.. на второй вход первого формирователя

3 импульсов с одного из ныходон счетчика 2 одновременно с импульсом, поступающим с другого его выхода, соответствующего выходу его следующего разряда, на третий вход первого формирователя 3 импульсов.

Таким образом, при отсутствии ошибки проверяются все ячейки накопителя 10.

Технико-экономическое преимущество предлагаемого устройства заключается н повышении быстродействия в реI жиме его проверки за счет ввода средств автономного контроля в оперативное запоминающее устройство, выполненное в виде микросхемы.

Формула изобретения

1. Оперативное запоминающее устройство с автономным контролем,содержащее накопитель, дешифраторы, усилители, блок управления и блок ввода-вывода информации, причем выходы первого дешифратора подключены соответственно к входам первого усилителя, выходы которого соединены соответственно с одним из входов накопителя, другие выходы блока вводанывода информации является первым выходом устройства, а другие выходы соединены с одними из входов второго дешифратора, выходы которого подключены ко входам второго усилителя, выходы блока управления соединены соответственно с управляющими входами дешифраторов и усилителей, о т-. л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит счетчик, генератор импульсов, формирователи импульсов, элементы ИЛИ и блок анализа, причем вход генератора импульсов является первым входом устройства и соединен с первыми входами счетчика, первого формирователя импульсов и блока анализа, выход генератора импульсов подключен к первому входу второго формирователя импульсов и второму входу счетчика, один иэ выходов которого соединен со вторым входом первого формирователя импульсов, а другие выходы подключены соответственно ко входам первого дешифратора, другим входом второго дешифратора и третьему входу первого формирователя импульсов, первый выход которого соединен со вторым входом второго формирователя импульсов, а второй выход — со вторым входом блока анализа, третий вход . которого подключен к первому выходу устройства, первый выход второго формирователя импульсов соединен с четвертым входом блока анализа, второй выход - с пятым входом блока анализа и первым

855739 входом первого элемента ИЛИ,а третий выход с первым входом второго элемента ИЛИ, первый вход третьего элемента ИЛИ подключен к третьему выходу первого формирователя импульсов, выходы вывода информации, вторые входы элементов ИЛИ и выход блока анали. за являются соответственно вторым, третьим и четвертым входами и вторым выходом устройства.

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок анализа содержит схему сравнения, элемент И и триггеры, причем выход схемы сравнения подключен к первому входу элемента И, выход которого соединен с первым входом первого триггера, выход которого подключен к первому входу второго триггера, второй вход и выход которого соединены соответственно с первым входом и выходом блока анализа, входы схемы сравнения подключены соответственно ко второму и к третьему входам блока анализа, а вторые входы элемента И и первого триггера — соответственно к четвертому и пятому входам блока анализа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 557419, кл. G 11 С 29/00, 1977.

2. Каталог интегральных схем, ч.1, Под ред. Б.A. Бородина. ЦКБ, 1978

35 (прототип).